КУРСОВОЙ ПРОЕКТ

на тему:

«Микропроцессорные

системы»

1.

Цель работы

Разработать микропроцессорную

систему в составе:

- I-8088,

- 2 кБ ROM,

- 4 кБ RAM,

- I-8255

- I-8279.

2. Разработка структурной схемы

Данная работа посвящена разработке

микропроцессорной системы с минимальной конфигурацией, что предполагает

использование управляющих сигналов, формируемых непосредственно на выводах микропроцессора

Intel 8088. Структурная схема системы представлена на рисунке 1.

Микропроцессорная система состоит из девяти

основных узлов:

• Тактовый генератор GEN;

• Микропроцессор CPU;

• Буферный регистр RG;

• Шинный формирователь BD;

• Модуль памяти MEMR;

• Модуль ввода/вывода IOU;

• Шина адреса ША;

• Шина данных ШД;

• Шина управления ШУ.

Тактовый генератор GEN служит для генерации

тактирующего сигнала обеспечивающего синхронизацию работы микропроцессора и

микропроцессорной системы в целом. Так же формирует сигнала “ready” служащий

для индикации момента, когда установились частота генерируемого сигнала, и

сигнала “reset” служащего для сброса микропроцессора и других элементов

системы.

Микропроцессор CPU обеспечивает выполнение программы, хранящейся модуле памяти, формирует

адреса и сигналы управления для обращения к определенным ячейкам памяти модуля

памяти, и отдельным элементам системы, таким как порты ввода/вывода, контроллер

прерываний. Ниже поясняется назначение этих сигналов:

A (15-0) – адрес ячейки памяти или

порта ввода/вывода;

D(7-0)- 8 разрядная шина данных;

CLK -

тактовая частота, синхронизирующая работу микропроцессора;

RDY -

сигнал готовности;

CLR- сигнал сброса микропроцессора;

STB – выход строба адреса. Служит

сигналом разрешения передачи адреса для буферного регистра.

DT /R – сигнал для шинного формирователя, служащий для указания направления передачи

данных (в CPU/ от CPU).

DE – сигнал активизации шины данных.

Низкий уровень подключает микропроцессор к шине данных, высокий уровень

переводит выходы шинного формирователя в высокоимпедансное состояние.

M/IO – сигнал, служащий для

различения обращения к модулю памяти или модулю ввода/вывода.

RD – сигнал стробирующий чтение данных из модуля памяти или модуля ввода/вывода.

WR – сигнал стробирующий запись данных в модуль памяти или модуль ввода/вывода.

Буферный регистр RG служит для удержания адреса на шине адреса (буферизация), в течении

некоторого времени определяемого сигналом STB.

Так же служит для усиления сигналов

A/D (15-0).

Шинный формирователь BD служит для коммутации микропроцессора

с шиной данных, выбора направления передачи данных, усиления сигнала выдаваемого

микропроцессором на шину.

Модуль памяти MEMR обеспечивает запись, чтение, хранение

данных. Хранит программу необходимую для работы процессора.

Модуль ввода/вывода IOU обеспечивает обмен данными между

микропроцессорной системой и подключаемыми к ней внешними устройствами.

Шина адреса шестнадцати разрядная

шина, служащая для передачи адреса ячейки памяти при обращении к модулю памяти,

адреса порта при обращении к портам ввода/вывода, или адреса контроллера прерываний

при обмене данными между контроллером прерываний и процессором.

Шина данных восьми разрядная шина,

необходимая для обмена данными между процессором и модулем памяти, процессором

и модулем ввода/вывода.

Шина управления служит для передачи

управляющих сигналов, таких как чтение данных, запись данных, выбор порт/память

при адресации, и др., от процессора к другим модулям системы, а так же для передачи

сигналов запроса прерывания от модуля ввода/вывода к процессору.

Рис. 1. Структурная схема системы

3

Разработка принципиальной

электрической схемы

Генератор тактовых импульсов выполнен

на микросхеме 8284. Генератор имеет в своем составе кварцевый резонатор для

обеспечения повышенной стабильности частоты генерируемого сигнала, кнопку

сброса обеспечивающую выдачу генератором на вход процессора сигнала RESET, ![]()

![]() RC цепь исключающую эффект “дребезга” контактов при нажатии кнопки

сброса. Генератор имеет пять входов и три выхода. Ко входам X1 и X2

подключается кварцевый резонатор, вход F/C служит для выбора внутреннего или

внешнего задающего генератора, при подаче на него логического “0” генерация

тактовых импульсов производится внутренним генератором, при подаче “1” –

внешним задающим генератором, вход CSN позволяет обеспечить синхронизацию

тактовых сигналов путем сброса делителей частоты при работе от внешнего

задающего генератора. Входы F/C и CSN в данной схеме заземлены. Ко входу RES

подключается кнопка сброса. На выходе CLK подключенному ко входу CLK процессора,

формируется тактовый сигнал генерируемый генератором. Выход RES служит для выдачи

сигнала сброса, и подключен ко входу RESET процессора. Выход RDY генератора подключен ко входу RDY процессора, и

выдает сигнал готовности генератора.

RC цепь исключающую эффект “дребезга” контактов при нажатии кнопки

сброса. Генератор имеет пять входов и три выхода. Ко входам X1 и X2

подключается кварцевый резонатор, вход F/C служит для выбора внутреннего или

внешнего задающего генератора, при подаче на него логического “0” генерация

тактовых импульсов производится внутренним генератором, при подаче “1” –

внешним задающим генератором, вход CSN позволяет обеспечить синхронизацию

тактовых сигналов путем сброса делителей частоты при работе от внешнего

задающего генератора. Входы F/C и CSN в данной схеме заземлены. Ко входу RES

подключается кнопка сброса. На выходе CLK подключенному ко входу CLK процессора,

формируется тактовый сигнал генерируемый генератором. Выход RES служит для выдачи

сигнала сброса, и подключен ко входу RESET процессора. Выход RDY генератора подключен ко входу RDY процессора, и

выдает сигнал готовности генератора.

![]()

![]()

![]()

![]() В качестве центрального процессора используется микросхема микропроцессора

I-8088. Эта микросхема имеет шестнадцать адресных выходов A0-A15 и совмещённых

с младшими разрядами адреса шину данных D0-D7, которые соответственно

обеспечивают выдачу адреса на шину адреса, и выдачу (прием) данных на (с) шину

данных. Эти выходы подключены к двум микросхемам 8282 и к одной микросхеме 8286

таким образом, что младшие восемь разрядов подключены к одной микросхеме 8282 и

одной 8286, старшие к оставшейся микросхеме 8282. Сигнал STB формируемый

микропроцессором является стробирующим сигналом для буферных регистров RG.

Выход DT /R формирует сигнал направления передачи данных для шинного формирователя

выполненного на микросхеме 8286. Сигнал DEN определяет тип информации передаваемой в текущий момент на шину AD0-A15

(адрес/данные), и является сигналом выбора микросхемы для шинного формирователя.

Сигнал IO/M служит для указания типа устройства (память или устройства В/В) при

адресации. Сигналы RD, WR являются стробирующими сигналами чтения и записи соответственно. Вход

процессора MN/MX служит для выбора типа конфигурации системы (максимальная/минимальная).

Для выбора минимальной конфигурации этот вход подключен к логической “1”.

В качестве центрального процессора используется микросхема микропроцессора

I-8088. Эта микросхема имеет шестнадцать адресных выходов A0-A15 и совмещённых

с младшими разрядами адреса шину данных D0-D7, которые соответственно

обеспечивают выдачу адреса на шину адреса, и выдачу (прием) данных на (с) шину

данных. Эти выходы подключены к двум микросхемам 8282 и к одной микросхеме 8286

таким образом, что младшие восемь разрядов подключены к одной микросхеме 8282 и

одной 8286, старшие к оставшейся микросхеме 8282. Сигнал STB формируемый

микропроцессором является стробирующим сигналом для буферных регистров RG.

Выход DT /R формирует сигнал направления передачи данных для шинного формирователя

выполненного на микросхеме 8286. Сигнал DEN определяет тип информации передаваемой в текущий момент на шину AD0-A15

(адрес/данные), и является сигналом выбора микросхемы для шинного формирователя.

Сигнал IO/M служит для указания типа устройства (память или устройства В/В) при

адресации. Сигналы RD, WR являются стробирующими сигналами чтения и записи соответственно. Вход

процессора MN/MX служит для выбора типа конфигурации системы (максимальная/минимальная).

Для выбора минимальной конфигурации этот вход подключен к логической “1”.

![]() Буферные

регистры выполнены на восьми разрядных микросхемах 8282. Входы данных этих микросхем

подключены к выходам AD0-A15 микропроцессора, выходы подключены к шине адреса.

На вход стробирования STB поступает сигнал сторбирования адреса STB с

процессора, ко входу выбора микросхемы OE подведен логический “0”.

Буферные

регистры выполнены на восьми разрядных микросхемах 8282. Входы данных этих микросхем

подключены к выходам AD0-A15 микропроцессора, выходы подключены к шине адреса.

На вход стробирования STB поступает сигнал сторбирования адреса STB с

процессора, ко входу выбора микросхемы OE подведен логический “0”.

Шинный формирователь выполнен на

восьми разрядной микросхеме 8286. Входы данных этой микросхемы подключены к

входам/выходам AD0-AD7 микропроцессора, выходы подключены к шине данных. На

вход направления передачи данных поступает сигнал DT/R с процессора, ко входу выбора микросхемы OE подведен сигнал DEN формируемый

процессором.

На рис. 2а показан фрагмент

принципиальной схемы подключения микропроцессора I-8086 к системной шине.

Рис. 2а. Подключение микропроцессора

к системной шине

В соответствии с заданием выбрано ПЗУ

с ёмкостью 2Кх8 и ОЗУ с ёмкостью 4Кх8. Подключение ОЗУ и ПЗУ к системной шине

приведено на рис. 1б.

В качестве ПЗУ использована

микросхема К568РЕ1, которая содержит 8 разрядов данных и 11 адресных входов,

позволяющих обращаться к 2 Кбайт памяти.

Располагаем в 64К байтовом адресном

пространстве память ПЗУ в диапазоне адресов от 0000h до 07FFh (2К байт). Для обращения к данному адресному пространству и формированию

сигнала «CS» для ПЗУ используем дешифратор адреса ПЗУ, состоящий из логических

элементов DD1.1, DD2.1, DD3.1 и DD4.1.

В качестве ОЗУ использованы 2

микросхемы К537РУ10 емкостью 2Кх8 каждая, в результате чего получаем суммарную

ёмкость ОЗУ 4к. Входные сигналы управления определяют работу микросхемы в

режиме записи и считывания. При установленном адресе и сигналах «CS»= «WE»=0,

«OE»=1 производится запись в ОЗУ установленного на шине данных записываемого

байта данных. При установленном адресе и сигналах «CS»= «OE»=0, «WE»=1 производится чтение из памяти выбранного байта на шину данных.

Располагаем в 64К байтовом адресном

пространстве память ОЗУ в диапазоне адресов от 1000h до 1FFFh (4K байт). Для обращения к данному адресному пространству и формированию

управляющих сигналов для ОЗУ используем дешифратор адреса ОЗУ, состоящий из

логических элементов DD1.2, DD2.2, DD3.2, DD2.3, DD5.1, DD5.2. Микросхема ОЗУ HS7 выбирается при A11=0 (т.к. имеет диапазон адресов

1000h-17FFh), а микросхема ОЗУ HS8 выбирается при A11=1 (т.к. имеет

диапазон адресов 1800h-1FFFh).

Рис. 2б. Подключение ПЗУ и ОЗУ к

системной шине

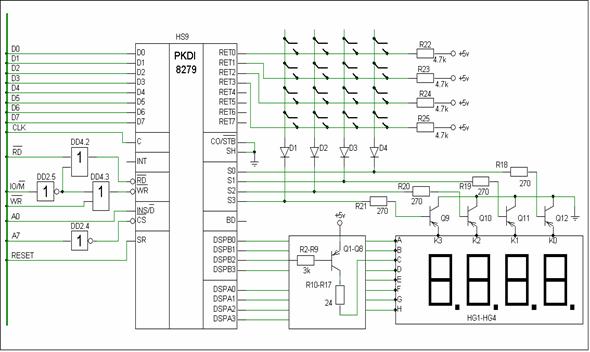

Проведём подключение микросхемы программируемого

контроллера I 8279, предназначенного для

обслуживания клавиатуры и алфавитно-цифрового дисплея.

Микросхема состоит из двух

функционально-автономных частей:

- клавиатурной, обеспечивающей ввод

информации в БИС через линии возврата с клавиатуры RET7-RET0,

- дисплейной части, обеспечивающей

вывод информации по двум 4-х разрядным каналам DSPA3-DSPA0 и DSPB3-DSPB0 в виде

двоичного кода на 8- и 16-разрядные цифровые и алфавитно-цифровые дисплеи.

Кроме того, микросхема обеспечивает формирование сигналов сканирования S3-S0

клавиатуры и дисплея, а также сигнала для межразрядного гашения «BD» информации на дисплее.

Подключим микросхему 8279 следующим

образом:

- будем использовать режим

дешифрированного сканирования, при котором c выходов сканирования S3-S0 непосредственно выдаются сигналы сканирования

клавиатуры и дисплея;

- используем для обмена программный

опрос (а не аппаратную систему прерываний);

- используем линейный выбор устройства

ввода-вывода, при котором на вход «CS» заводим инверсный разряд адресной шины А7.

Подключаем микросхему к системной

шине (см. рис. 2в):

- к выводам D7-D0 подключаем

системную шину данных;

- входы сброса, синхронизации и

выбора кристалла микросхемы подключаем к соответствующим сигналам управляющей

шины «RESET», «CLK», «А7»;

- на вход «INS/D» заводим разряд адресной шины A0;

- на вход «RD», «WR» микросхемы подаём сигналы с выходов дешифратора, построенного DD2.4, DD2.5, DD4.2, DD4.3, на входы которого поступают сигналы с системной шины «IO/M», «RD», «WR».

Подключаем клавиатуру и дисплей к микросхеме

8279:

- в качестве дисплея используем 4 7-сегментных

индикатора с общим анодом;

- выводы 8279 DSPA3-DSPA0 и

DSPB3-DSPB0 через усилитель, построенный на транзисторах, подсоединяем

непосредственно к выводам «А», «Б», «С», «D», «E», «F», «G», «H» индикаторов;

- выходы S0-S3 через формирователи,

построенные на транзисторах, подсоединяем к общим анодам 7-сегментных

индикаторов;

- в качестве клавиатуры используем

матрицу ключей 4х4, столбцы которой подключаются к выводам S0-S3, а замыкаемые через ключи столбцы к строкам линии возврата RET3-RET0.

Рис. 2в. Подключение 8279 к системной

шине, дисплею и клавиатуре

Проведём подключение микросхемы

программируемого параллельного интерфейса I-8255, предназначенного для организации ввода-вывода параллельной

информации различного формата и позволяющего реализовывать большинство

известных протокола обмена. Со стороны системной шины микросхема содержит

двунаправленный 8-разрядный канал данных, сигналы чтения «RD» и записи «WR», определяющих вид операции, сигнал выбора кристалла «CS» и входы А0 и А1 для адресации внутренних регистров микросхемы и вход

сброса «RESET». Со стороны подключения внешних устройств микросхема содержит 3 двунаправленных

канала А, В и С для обмена данными. Сигналы управления со стороны системной

шины определяют вид операции, выполняемой микросхемой 8255 в соответствии с

таблицей.

|

Операция |

Сигналы управления |

||||

|

CS |

RD |

WR |

А1 |

А0 |

|

|

Запись

управляющего слова из МП |

0 |

1 |

0 |

1 |

1 |

|

Запись в

канал А |

0 |

1 |

0 |

0 |

0 |

|

Запись в

канал B |

0 |

1 |

0 |

0 |

1 |

|

Запись в

канал C |

0 |

1 |

0 |

1 |

0 |

|

Чтение

данных из канала А |

0 |

0 |

1 |

0 |

0 |

|

Чтение

данных из канала В |

0 |

0 |

1 |

0 |

1 |

|

Чтение

данных из канала С |

0 |

0 |

1 |

1 |

0 |

|

Отключение

микросхемы от ШД |

1 |

х |

х |

х |

х |

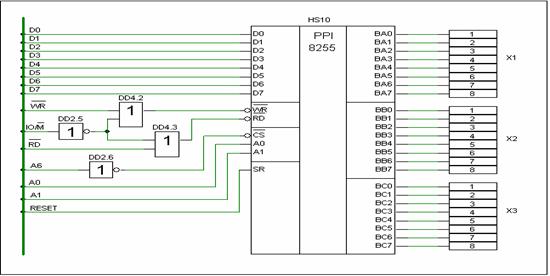

Подключение микросхемы 8255 к

системной шине (см. рис. 2г):

- линии D0-D7 подключаются к шине

данных;

- сигналы «WR» и «RD» подключаются

через дешифратор DD2.5, DD4.2, DD4.3, позволяющий получить сигналы чтения и

записи для внешнего устройства;

- вход «CS» к инверсному сигналу шины

адреса А6;

- входы А1 и А0 к одноимённым входам

адресной шины;

- 8-разрядные порты ввода-вывода

выводим на разъёмы Х1, Х2 и Х3.

Рис. 2г. Подключение 8255 к системной

шине

4. Программирование I-8279

Программирование микросхем

микропроцессорного комплекта и, в частности, микросхемы 8279 осуществляется,

как правило, с помощью программы начальной инициализации, которая выполняется

при включении питания (или после сигнала RESET поданный на микропроцессор),

начиная с начального адреса выполнения общей программы микропроцессора, или в

процессе обмена данными между микропроцессором и внешними устройствами.

Программирование микросхемы

подразумевает наличие форматов команд, данных и управляющих слов, с помощью

которых микропроцессор программирует микросхему и осуществляет обмен. Программирование

8279 осуществляется с помощью восьми команд.

В адресном пространстве портов

ввода-вывода микросхема 8279 представлена 2 портами. Адреса микросхемы 8279 в

адресном пространстве ВУ следующие

-

регистр данных - 80h;

-

регистр команд и состояния -

81h.

После подачи сигнала RESET запрограммируем БИС в следующем режиме:

-

сканирование контактной клавиатуры c внутренней дешифрацией и с запретом одновременного нажатия

2-х и более клавиш;

-

4 разрядный 8-ми символьный дисплей;

-

чтение ОЗУ клавиатуры и запись индикаторного ОЗУ;

-

адрес индикаторного ОЗУ равен нулю;

- коэффициент деления входной частоты

равен 0Fh.

MOV AL, 01h ; команда установки режима индикатора

и клавиатуры;

заполнение строки дисплея слева,

сканирование контактной; клавиатуры с блокировкой одновременного нажатия;

клавиш, дешифрация сигналов

сканирования внутренняя OUT 81h, AL;

вывод команды из МП в регистр команд

8279MOV AL, 2Fh;

команда программирования

синхронизации c;

коэффициентом деления базовой

тактовой частоты на 0FhOUT 81h, AL;

вывод команды из МП в регистр команд

8279.

Символы, сформированные нажатыми

клавишами считываем через память FIFO. Осуществим ввод 8 байтов и запомним их в

массиве KEYS (первый байт находится по старшему адресу).

MOV SI, 8;

счётчик массиваMOV AL, 40h;

команда чтения буферного ОЗУ

клавиатуры без;

автоинкремента и с начальным адресом ОЗУ

000b OUT 81h, AL

N1: IN AL, 81h; МП ждёт до готовности ввода

TEST

AL, 0Fh

JZ

N1

IN

AL, 80h;

передача введённых данных в КЕYS MOV KEYS[SI-1], AL

DEC SI

JNZ N1

Осуществим индикацию 4 цифр,

хранящихся по адресу DIG (младшая цифра хранится по меньшему адресу).

MOV SI, 4 ; счётчик массива

MOV AL, 90h ; команда записи в индикаторное ОЗУ с

;

автоинкрементом и с начальным адресом

ОЗУ 000b

OUT 81h, AL

N2: MOV AL, DIG[SI-1] ; цикл вывода цифр в память

индикатора

OUT

80h, AL

DEC

SI

JNZ

N1

5. Программирование I-8255

Программирование микросхемы 8255

осуществляется со стороны микропроцессора командами IN и OUT в программе

начальной инициализации. Режим работы каждого из двунаправленных каналов программируется

с помощью управляющего слова, которое может задавать один из трёх режимов

работы:

- основной режим ввода-вывода (режим

0);

- стробируемый ввод-вывод (режим 1);

- режим двунаправленной передачи

(режим 2).

В дополнение к основным режимам

работы микросхема 8255 обеспечивает возможность программной независимой

установки в 1 или в 0 любого из разрядов канала С. В режимах 1 и 2 возможно

проведение контроля за состоянием работы микросхемы 8255 и внешнего устройства,

которое к ней подключено. Контроль осуществляется чтением слова состояния

канала С по команде IN (обычная операция чтения канала С).

В адресном пространстве портов

ввода-вывода микросхема 8255 представлена 4 портами. Микросхема 8255 в

соответствии с подключением на принципиальной схеме в адресном пространстве

устройств ввода-вывода имеет следующие адреса:

-

адрес канала А - 40h;

-

адрес канала В - 41h;

-

адрес канала С - 42h;

-

адрес регистра режима -

43h;

Запрограммируем микросхему на работу

каналов А, В, С в режиме 0, причём каналы А и В работают в режиме вывода

информации, а канал С в режиме ввода.

MOV AL, 89h ; команда режима

OUT 43h, AL

MOV AL, BYTE1 ; вывод BYTE1 в канал А

OUT

40h, AL

MOV

AL, BYTE21 ; вывод BYTE2 в канал B

OUT 41h, AL

IN AL, 42h ; ввод BYTE3 из канала С в регистр АL

ВЫВОДЫ

В соответствии с заданными требованиями

разработана микропроцессорная система на базе МП 8088, содержащая 2к ПЗУ, 4к

ОЗУ и микросхемы 8279 и 8255.

Написана программа инициализации микросхем

8255 и 8279.

Таблица. Перечень элементов

|

Поз. обозн. |

Наименование |

|

Кол- во |

Примечание |

|

|

Микросхемы |

|

|

|

|

HS1 |

8284 |

|

1 |

|

|

HS2 |

8088 |

|

1 |

|

|

HS3, HS4 |

8282 |

|

2 |

|

|

HS5 |

8286 |

|

1 |

|

|

HS6 |

К568РЕ1 |

|

1 |

|

|

HS7, HS8 |

К537РУ10 |

|

2 |

|

|

HS9 |

8279 |

|

1 |

|

|

HS10 |

8255 |

|

1 |

|

|

DD1 |

К531ЛЕ7 |

|

1 |

|

|

DD2 |

К531ЛН1 |

|

1 |

|

|

DD3 |

К155ЛА3 |

|

1 |

|

|

DD4 |

К155ЛЛ1 |

|

1 |

|

|

DD5 |

К155ЛА4 |

|

1 |

|

|

|

Кварцевый

резонатор |

|

|

|

|

BP1 |

Кварц 9

МГц |

|

1 |

|

|

|

Резисторы |

|

|

|

|

R1 |

100 кОм |

|

1 |

|

|

R2- R9 |

3 кОм |

|

8 |

|

|

R10-R17 |

24 Ом |

|

8 |

|

|

R18-R21 |

270 Ом |

|

4 |

|

|

R22-R25 |

4.7 кОм |

|

4 |

|

|

|

Конденсатор |

|

|

|

|

C1 |

С – 10B – 1.0мкФ |

|

1 |

|

|

|

Диоды |

|

|

|

|

D1-D4 |

КД522А |

|

4 |

|

|

|

Транзисторы |

|

|

|

|

Q1-Q12 |

2N2907 |

|

12 |

|

|

|

Индикаторы |

|

|

|

|

HG1-HG4 |

АЛС324Б |

|

4 |

|

|

|

Клавиатура |

|

|

|

|

|

Матрица ключей клавиатуры 4х4 |

|

1 |

|

|

|

Коннекторы |

|

|

|

|

Х1-Х3 |

CON-8 |

|

3 |

|