лЏл░л▒лЙЛђл░ЛѓлЙЛђлйл░ЛЈ Лђл░л▒лЙЛѓл░.

лалхл░л╗лИлил░ЛєлИЛЈ лИ лЙл▒ЛЂл╗ЛЃлХлИл▓л░лйлИлх л┐лЙл┤ЛЂлИЛЂЛѓлхл╝ЛІ л┐ЛђлхЛђЛІл▓л░лйлИл╣

лдлхл╗Лї Лђл░л▒лЙЛѓЛІ РђЊ лИлиЛЃЛЄлхлйлИлх лЙЛђл│л░лйлИлил░ЛєлИлИ л┐ЛђлхЛђЛІл▓л░лйлИл╣ л▓ л╝лИл║ЛђлЙл║лЙлйЛѓЛђлЙл╗л╗лхЛђлх ATmega128 лИ лЙл▒ЛЂл╗ЛЃлХлИл▓л░лйлИЛЈ л┐лЙл┤ЛЂлИЛЂЛѓлхл╝ЛІ л┐ЛђлхЛђЛІл▓л░лйлИл╣.

1. лъЛЂлйлЙл▓лйЛІлх

ЛЂл▓лхл┤лхлйлИЛЈ

люлИл║ЛђлЙл║лЙлйЛѓЛђлЙл╗л╗лхЛђЛІ ATmega128 лИЛЂл┐лЙл╗ЛїлиЛЃЛјЛѓ 34 лИЛЂЛѓлЙЛЄлйлИл║л░ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лГЛѓлИ

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ лИ л╝лхЛЁл░лйлИлил╝ ЛЂл▒ЛђлЙЛЂл░ Лђл░ЛЂл┐лЙл╗л░л│л░ЛјЛѓ лЙЛѓл┤лхл╗ЛїлйЛІл╝лИ л▓лхл║ЛѓлЙЛђл░л╝лИ л▓ л┐ЛђлЙЛЂЛѓЛђл░лйЛЂЛѓл▓лх

л┐л░л╝ЛЈЛѓлИ л┐ЛђлЙл│Лђл░л╝л╝. лџл░лХл┤лЙл╝ЛЃ л┐ЛђлхЛђЛІл▓л░лйлИЛј л┐ЛђлИЛЂл▓лЙлхлй ЛЂл▓лЙл╣ л▒лИЛѓ Лђл░лиЛђлхЛѕлхлйлИЛЈ, л║лЙЛѓлЙЛђЛІл╣

л┤лЙл╗лХлхлй л▒ЛІЛѓЛї ЛЃЛЂЛѓл░лйлЙл▓л╗лхлй ЛЂлЙл▓л╝лхЛЂЛѓлйлЙ ЛЂ л▒лИЛѓлЙл╝ I Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░ SREG.

люл╗л░л┤ЛѕлИлх л░л┤ЛђлхЛЂл░ л┐ЛђлЙЛЂЛѓЛђл░лйЛЂЛѓл▓л░ л┐л░л╝ЛЈЛѓлИ л┐ЛђлЙл│Лђл░л╝л╝

л░л▓ЛѓлЙл╝л░ЛѓлИЛЄлхЛЂл║лИ лЙл┐Лђлхл┤лхл╗ЛЈЛјЛѓЛЂЛЈ л║л░л║ л▓лхл║ЛѓлЙЛђЛІ ЛЂл▒ЛђлЙЛЂл░ лИ л┐ЛђлхЛђЛІл▓л░лйлИл╣.

лЪлЙл╗лйЛІл╣ л┐лхЛђлхЛЄлхлйЛї л▓лхл║ЛѓлЙЛђлЙл▓ л┐Лђлхл┤ЛЂЛѓл░л▓л╗лхлй л▓ Лѓл░л▒л╗. 6. лЪлхЛђлхЛЄлхлйЛї лЙЛѓЛђл░лХл░лхЛѓ Лѓл░л║лХлх ЛЃЛђлЙл▓лхлйЛї л┐ЛђлИлЙЛђлИЛѓлхЛѓл░ л┤л╗ЛЈ л║л░лХл┤лЙл│лЙ

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лЪЛђлхЛђЛІл▓л░лйлИЛЈ ЛЂ л╝л╗л░л┤ЛѕлИл╝лИ л░л┤ЛђлхЛЂл░л╝лИ лИл╝лхЛјЛѓ л▒лЙл╗ЛїЛѕлИл╣ ЛЃЛђлЙл▓лхлйЛї л┐ЛђлИлЙЛђлИЛѓлхЛѓл░:

RESET лИл╝лхлхЛѓ лйл░лИл▓ЛІЛЂЛѕлИл╣ ЛЃЛђлЙл▓лхлйЛї л┐ЛђлИлЙЛђлИЛѓлхЛѓл░, ЛЂл╗лхл┤ЛЃЛјЛЅлИл╝ ЛЈл▓л╗ЛЈлхЛѓЛЂЛЈ лил░л┐ЛђлЙЛЂ л▓лйлхЛѕлйлхл│лЙ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ

INT0 лИ Лѓ.л┤.

лбл░л▒л╗лИЛєл░. лњлхл║ЛѓлЙЛђЛІ ЛЂл▒ЛђлЙЛЂл░ лИ л┐ЛђлхЛђЛІл▓л░лйлИл╣

|

Рёќ л┐.л┐. |

лљл┤ЛђлхЛЂ |

лўЛЂЛѓлЙЛЄлйлИл║

|

лЮл░лИл╝лхлйлЙл▓л░лйлИлх

|

|

1 |

2 |

3 |

4 |

|

1 |

$0000 |

RESET |

лАл▒ЛђлЙЛЂ л┐лЙ ЛЂлИл│лйл░л╗ЛЃ Reset, л▓л║л╗ЛјЛЄлхлйлИЛј л┐лИЛѓл░лйлИЛЈ лИ ЛЂЛѓлЙЛђлЙлХлхл▓лЙл╝ЛЃ Лѓл░л╣л╝лхЛђЛЃ |

|

2 |

$0002 |

INT0 |

лЌл░л┐ЛђлЙЛЂ л▓лйлхЛѕлйлхл│лЙ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ 0 |

|

3 |

$0004 |

INT1 |

лЌл░л┐ЛђлЙЛЂ л▓лйлхЛѕлйлхл│лЙ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ 1 |

|

4 |

$0006 |

INT2 |

лЌл░л┐ЛђлЙЛЂ л▓лйлхЛѕлйлхл│лЙ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ 2 |

|

5 |

$0008 |

INT3 |

лЌл░л┐ЛђлЙЛЂ л▓лйлхЛѕлйлхл│лЙ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ 3 |

|

6 |

$000A |

INT4 |

лЌл░л┐ЛђлЙЛЂ л▓лйлхЛѕлйлхл│лЙ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ 4 |

|

7 |

$000C |

INT5 |

лЌл░л┐ЛђлЙЛЂ л▓лйлхЛѕлйлхл│лЙ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ 5 |

|

8 |

$0006 |

INT6 |

лЌл░л┐ЛђлЙЛЂ л▓лйлхЛѕлйлхл│лЙ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ 6 |

|

9 |

$0010 |

INT7 |

лЌл░л┐ЛђлЙЛЂ л▓лйлхЛѕлйлхл│лЙ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ 7 |

|

10 |

$0012 |

TIMER2 COMP |

лАлЙл▓л┐л░л┤лхлйлИлх

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T2 |

|

11 |

$0014 |

TIMER2

OVF |

лЪлхЛђлхл┐лЙл╗лйлхлйлИлх

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T2 |

|

12 |

$0016 |

TIMER1 CAPT |

лЌл░ЛЁл▓л░Лѓ

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T1 |

|

13 |

$0018 |

TIMER1 COMPA |

лАлЙл▓л┐л░л┤лхлйлИлх

┬Флљ┬╗ Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T1 |

|

14 |

$001A |

TIMER1 COMPB |

лАлЙл▓л┐л░л┤лхлйлИлх

┬ФB┬╗ Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T1 |

лъл║лЙлйЛЄл░лйлИлх Лѓл░л▒л╗.6

|

1 |

2 |

3 |

4 |

|

15 |

$001C |

TIMER1 OVF |

лЪлхЛђлхл┐лЙл╗лйлхлйлИлх

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T1 |

|

16 |

$001E |

TIMER0 COMP |

лАлЙл▓л┐л░л┤лхлйлИлх

л┐ЛђлИ ЛЂЛђл░л▓лйлхлйлИлИ Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T0 |

|

17 |

$0020 |

TIMER0

OVF |

лЪлхЛђлхл┐лЙл╗лйлхлйлИлх

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T0 |

|

18 |

$0022 |

SPI, STC |

лЌл░л▓лхЛђЛѕлхлйл░

л┐лхЛђлхЛЂЛІл╗л║л░ л┐лЙЛђЛѓл░ SPI |

|

19 |

$0024 |

UART0, RX |

лЌл░л▓лхЛђЛѕлхлйлИлх

л┐ЛђлИлхл╝л░ UART0 |

|

20 |

$0026 |

UART0, UDRE |

лалхл│лИЛЂЛѓЛђ

л┤л░лйлйЛІЛЁ UART0 л┐ЛЃЛЂЛѓ |

|

21 |

$0028 |

UART0, TX |

лЌл░л▓лхЛђЛѕлхлйлИлх

л┐лхЛђлхл┤л░ЛЄлИ UART0 |

|

22 |

$002A |

ADC |

лЌл░л▓лхЛђЛѕлхлйлИлх

AD л┐ЛђлхлЙл▒Лђл░лилЙл▓л░лйлИЛЈ |

|

23 |

$002C |

EE READY |

лЊлЙЛѓлЙл▓лйлЙЛЂЛѓЛї EEPROM |

|

24 |

$002E |

ANALOG COMP |

лАЛђл░л▒л░ЛѓЛІл▓л░лйлИлх

л░лйл░л╗лЙл│лЙл▓лЙл│лЙ л║лЙл╝л┐л░Лђл░ЛѓлЙЛђл░ |

|

25 |

$0030 |

TIMER1 COMPC |

лАлЙл▓л┐л░л┤лхлйлИлх ┬ФлА┬╗ Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T1 |

|

26 |

$0032 |

TIMER3┬а CAPT |

лЪлхЛђлхл┐лЙл╗лйлхлйлИлх

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T3 |

|

27 |

$0034 |

TIMER3 COMPA |

лАлЙл▓л┐л░л┤лхлйлИлх

┬ФA┬╗ Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T3 |

|

28 |

$0036 |

TIMER3 COMPB |

лАлЙл▓л┐л░л┤лхлйлИлх

┬ФB┬╗ Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T3 |

|

29 |

$0038 |

TIMER3 COMPC |

лАлЙл▓л┐л░л┤лхлйлИлх

┬ФлА┬╗ Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T3 |

|

30 |

$003A |

TIMER3 OVF |

лЪлхЛђлхл┐лЙл╗лйлхлйлИлх

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T3 |

|

31 |

$003C |

USART1, RX |

лЌл░л▓лхЛђЛѕлхлйлИлх

л┐ЛђлИлхл╝л░ UART |

|

32 |

$003E |

USART1, UDRE |

лалхл│лИЛЂЛѓЛђ

л┤л░лйлйЛІЛЁ UART1 л┐ЛЃЛЂЛѓ |

|

33 |

$0040 |

USART1, TX |

лЌл░л▓лхЛђЛѕлхлйлИлх

л┐лхЛђлхл┤л░ЛЄлИ UART1 |

|

34 |

$0042 |

TWI |

лЪЛђлхЛђЛІл▓л░лйлИлх

лЙЛѓ л╝лЙл┤ЛЃл╗ЛЈ TWI |

|

35 |

$0044 |

SPM_RDY |

лЊлЙЛѓлЙл▓лйлЙЛЂЛѓЛї

SPM |

люлИл║ЛђлЙл║лЙлйЛѓЛђлЙл╗л╗лхЛђЛІ ATmega128 ЛЂлЙл┤лхЛђлХл░Лѓ л┤л▓л░ ЛЂл┐лхЛєлИл░л╗ЛїлйЛІЛЁ

8-Лђл░лиЛђЛЈл┤лйЛІЛЁ Лђлхл│лИЛЂЛѓЛђл░ л╝л░ЛЂлЙл║ л┐ЛђлхЛђЛІл▓л░лйлИл╣: Лђлхл│лИЛЂЛѓЛђ л╝л░ЛЂлЙл║ л▓лйлхЛѕлйлИЛЁ л┐ЛђлхЛђЛІл▓л░лйлИл╣ EIMSK (External

Interrupt Mask) лИ

Лђлхл│лИЛЂЛѓЛђ л╝л░ЛЂлЙл║ л┐ЛђлхЛђЛІл▓л░лйлИл╣ Лѓл░л╣л╝лхЛђлЙл▓/ЛЂЛЄлхЛѓЛЄлИл║лЙл▓ TIMSK (Timer/Counter

Interrupt Mask).

лџЛђлЙл╝лх ЛѓлЙл│лЙ, л▓ Лђлхл│лИЛЂЛѓЛђл░ЛЁ ЛЃл┐Лђл░л▓л╗лхлйлИЛЈ л▒л╗лЙл║л░л╝лИ л▓л▓лЙл┤л░-л▓ЛІл▓лЙл┤л░ л╝лЙл│ЛЃЛѓ ЛЂЛЃЛЅлхЛЂЛѓл▓лЙл▓л░ЛѓЛї

л┤ЛђЛЃл│лИлх л▒лИЛѓЛІ Лђл░лиЛђлхЛѕлхлйлИЛЈ лИ л▒лИЛѓЛІ л╝л░ЛЂлЙл║.

лЪЛђлИ л▓лЙлилйлИл║лйлЙл▓лхлйлИлИ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л▒лИЛѓ I Лђл░лиЛђлхЛѕлхлйлИЛЈ л▓ЛЂлхЛЁ

л┐ЛђлхЛђЛІл▓л░лйлИл╣ (л▓ Лђлхл│лИЛЂЛѓЛђлх SREG) лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ лИ л▓ЛЂлх л┐ЛђлхЛђЛІл▓л░лйлИЛЈ лил░л┐ЛђлхЛЅл░ЛјЛѓЛЂЛЈ. лЪЛђлЙЛєлхл┤ЛЃЛђл░ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ

л╝лЙлХлхЛѓ ЛЃЛЂЛѓл░лйлЙл▓лИЛѓЛї л▒лИЛѓ I, ЛЄЛѓлЙл▒ЛІ

Лђл░лиЛђлхЛѕлИЛѓЛї л▓л╗лЙлХлхлйлйЛІлх л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лњЛІЛЁлЙл┤ лИли л┐ЛђлЙЛєлхл┤ЛЃЛђЛІ лЙл▒Лђл░л▒лЙЛѓл║лИ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐ЛђлЙлИЛЂЛЁлЙл┤лИЛѓ

л┐лЙ л║лЙл╝л░лйл┤лх RETI, л║лЙЛѓлЙЛђл░ЛЈ ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓ л▒лИЛѓ I (=1).

лџлЙл│л┤л░ л▓ ЛЂЛЄлхЛѓЛЄлИл║ л║лЙл╝л░лйл┤ лил░л│ЛђЛЃлХлхлй л▓лхл║ЛѓлЙЛђ л┐ЛђлЙЛєлхл┤ЛЃЛђЛІ

лЙл▒Лђл░л▒лЙЛѓл║лИ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ, ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлИл╣ Лёл╗л░л│, л▓ЛІлил▓л░л▓ЛѕлИл╣ л┐ЛђлхЛђЛІл▓л░лйлИлх, л░л┐л┐л░Лђл░ЛѓлйлЙ

лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ. лЮлхл║лЙЛѓлЙЛђЛІлх Лёл╗л░л│лИ л┐ЛђлхЛђЛІл▓л░лйлИл╣ л╝лЙлХлйлЙ лЙЛЄлИЛЂЛѓлИЛѓЛї л┐ЛђлЙл│Лђл░л╝л╝лйлЙ.

лЋЛЂл╗лИ ЛЃЛЂл╗лЙл▓лИЛЈ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л▓лЙлилйлИл║л╗лИ, л║лЙл│л┤л░

ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлИл╣ л▒лИЛѓ Лђл░лиЛђлхЛѕлхлйлИЛЈ лЙЛЄлИЛЅлхлй, Лёл╗л░л│ ЛЇЛѓлЙл│лЙ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л▒ЛЃл┤лхЛѓ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлй лИ

ЛЂлЙЛЁЛђл░лйлхлй л▓ Лѓл░л║лЙл╝ ЛЂлЙЛЂЛѓлЙЛЈлйлИлИ, л┐лЙл║л░ л┐ЛђлхЛђЛІл▓л░лйлИлх лйлх л▒ЛЃл┤лхЛѓ Лђл░лиЛђлхЛѕлхлйлЙ лИл╗лИ Лёл╗л░л│ лйлх л▒ЛЃл┤лхЛѓ

лЙЛЄлИЛЅлхлй л┐ЛђлЙл│Лђл░л╝л╝лйлЙ.

лЋЛЂл╗лИ ЛЃЛЂл╗лЙл▓лИЛЈ л┐ЛђлхЛђЛІл▓л░лйлИл╣ л▓лЙлилйлИл║л╗лИ, л║лЙл│л┤л░ лЙЛЄлИЛЅлхлй л▒лИЛѓ Лђл░лиЛђлхЛѕлхлйлИЛЈ л▓ЛЂлхЛЁ л┐ЛђлхЛђЛІл▓л░лйлИл╣, Лёл╗л░л│лИ л┐ЛђлхЛђЛІл▓л░лйлИл╣

л▒ЛЃл┤ЛЃЛѓ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйЛІ лИ ЛЂлЙЛЁЛђл░лйлхлйЛІ л▓ Лѓл░л║лЙл╝ ЛЂлЙЛЂЛѓлЙЛЈлйлИлИ, л┐лЙл║л░ л▓ЛЂлх л┐ЛђлхЛђЛІл▓л░лйлИЛЈ лйлх л▒ЛЃл┤ЛЃЛѓ

Лђл░лиЛђлхЛѕлхлйЛІ лИ лЙл▒Лђл░л▒лЙЛѓл░лйЛІ л▓ л┐лЙЛђЛЈл┤л║лх л┐ЛђлИлЙЛђлИЛѓлхЛѓлЙл▓.

лЪЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ ЛЃЛђлЙл▓лйЛј ЛЂлИл│лйл░л╗л░ Лёл╗л░л│л░ лйлх лИл╝лхЛјЛѓ, л░ ЛЃЛЂл╗лЙл▓лИЛЈ

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ лИл╝лхЛјЛѓ л╝лхЛЂЛѓлЙ, л┐лЙл║л░ л░л║ЛѓлИл▓лхлй л▓лйлхЛѕлйлИл╣ ЛЂлИл│лйл░л╗.

лалхл│лИЛЂЛѓЛђ л╝л░ЛЂлЙл║

л▓лйлхЛѕлйлИЛЁ л┐ЛђлхЛђЛІл▓л░лйлИл╣┬а EIMSK:

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

$39 ($59) |

INT7

|

INT6

|

INT5

|

INT4

|

INT3

|

INT2

|

INT1

|

INT0

|

EIMSK

|

|

лўЛЂЛЁлЙл┤лйлЙлх лилйл░ЛЄлхлйлИлх |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

лЉлИЛѓЛІ 7...0 РђЊ лал░лиЛђлхЛѕлхлйлИлх л▓лйлхЛѕлйлИЛЁ л┐ЛђлхЛђЛІл▓л░лйлИл╣ INT7...INT0.

лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйЛІЛЁ л▒лИЛѓл░ЛЁ INT7 РђЊ INT0 лИ

ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░ (SREG) Лђл░лиЛђлхЛѕл░ЛјЛѓЛЂЛЈ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлИл╝

л▓ЛІл▓лЙл┤л░л╝ ЛЂлИл│лйл░л╗лЙл▓ л▓лйлхЛѕлйлИЛЁ л┐ЛђлхЛђЛІл▓л░лйлИл╣. лљл║ЛѓлИл▓лйлЙЛЂЛѓЛї ЛЂлИл│лйл░л╗л░ л┐лЙ л╗Лјл▒лЙл╝ЛЃ лИли ЛЇЛѓлИЛЁ л▓ЛІл▓лЙл┤лЙл▓

л▓ЛІлилЙл▓лхЛѓ лил░л┐ЛђлЙЛЂ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ, л┤л░лХлх лхЛЂл╗лИ л▓ЛІл▓лЙл┤ лйл░лилйл░ЛЄлхлй л║л░л║ л▓ЛІЛЁлЙл┤. лГЛѓлЙ лЙл▒лхЛЂл┐лхЛЄлИл▓л░лхЛѓ

л▓лЙлил╝лЙлХлйлЙЛЂЛѓЛї лЙЛђл│л░лйлИлил░ЛєлИлИ л┐ЛђлЙл│Лђл░л╝л╝лйлЙл│лЙ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ.

лалхл│лИЛЂЛѓЛђ Лёл╗л░л│лЙл▓ л▓лйлхЛѕлйлИЛЁ л┐ЛђлхЛђЛІл▓л░лйлИл╣┬а EIFR:

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

$38 ($58) |

INTF7

|

INTF6

|

INTF5

|

INTF4

|

INTF3

|

INTF2

|

INTF1

|

INTF0

|

EIFR

|

|

лўЛЂЛЁлЙл┤лйлЙлх лилйл░ЛЄлхлйлИлх |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

лЉлИЛѓЛІ 7...0 РђЊ лцл╗л░л│лИ л▓лйлхЛѕлйлИЛЁ л┐ЛђлхЛђЛІл▓л░лйлИл╣ INTF7РђдINTF0. лњ ЛЂл╗ЛЃЛЄл░лх л┐лЙЛЂЛѓЛЃл┐л╗лхлйлИЛЈ лил░л┐ЛђлЙЛЂл░ лйл░ л┐ЛђлхЛђЛІл▓л░лйлИлх лйл░

л║л░л║лЙл╣-л╗лИл▒лЙ лИли л▓ЛІл▓лЙл┤лЙл▓ INT7 РђЊ INT0 ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ ( =1)

ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлИл╣ Лёл╗л░л│ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ INTF7 РђЊ INTF0. лЋЛЂл╗лИ л▒лИЛѓ I Лђлхл│лИЛЂЛѓЛђл░ SREG лИ

ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлИл╣ л▒лИЛѓ Лђл░лиЛђлхЛѕлхлйлИЛЈ (INT7 РђЊ INT0) Лђлхл│лИЛЂЛѓЛђл░ EIMSK ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйЛІ, ЛѓлЙ

л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ л┐лхЛђлхЛЁлЙл┤ л┐лЙ л▓лхл║ЛѓлЙЛђЛЃ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лЪЛђлИ л▓лЙлил▓Лђл░Лѓлх лИли л┐ЛђлЙЛєлхл┤ЛЃЛђЛІ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ

Лёл╗л░л│ лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ. лџЛђлЙл╝лх ЛѓлЙл│лЙ, Лёл╗л░л│ л╝лЙлХлйлЙ лЙЛЄлИЛЂЛѓлИЛѓЛї, лил░л┐лИЛЂл░л▓ л▓ лйлхл│лЙ л╗лЙл│лИЛЄлхЛЂл║ЛЃЛј 1.лъл▒Лђл░ЛѓлИЛѓлх л▓лйлИл╝л░лйлИлх, ЛЄЛѓлЙ л┐ЛђлЙл│Лђл░л╝л╝лйлЙ ЛЃЛЂЛѓл░лйлЙл▓лИЛѓЛї Лёл╗л░л│

л▓лйлхЛѕлйлхл│лЙ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ, лил░л┐лИЛЂл░л▓ л▓ лйлхл│лЙ 1, лйлхл▓лЙлил╝лЙлХлйлЙ!

лалхл│лИЛЂЛѓЛђЛІ

ЛЃл┐Лђл░л▓л╗лхлйлИЛЈ л▓лйлхЛѕлйлИл╝лИ л┐ЛђлхЛђЛІл▓л░лйлИЛЈл╝лИ┬а EICRA лИ EICRB:

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

$6A |

ISC31

|

ISC30

|

ISC21

|

ISC20

|

ISC11

|

ISC10

|

ISC01

|

ISC00

|

EICRA

|

|

лўЛЂЛЁлЙл┤лйлЙлх лилйл░ЛЄлхлйлИлх |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

$3A ($5A) |

ISC71

|

ISC70

|

ISC61

|

ISC60

|

ISC51

|

ISC50

|

ISC41

|

ISC40

|

EICRB

|

|

лўЛЂЛЁлЙл┤лйлЙлх лилйл░ЛЄлхлйлИлх |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

лЉлИЛѓЛІ 7...0 РђЊ ISCX1, ISCX0: лЉлИЛѓЛІ ЛЃл┐Лђл░л▓л╗лхлйлИЛЈ

лЙл┐лЙлилйл░л▓л░лйлИлхл╝ л▓лйлхЛѕлйлИЛЁ л┐ЛђлхЛђЛІл▓л░лйлИл╣ INT7 РђЊ INT0. лЌл░л┐ЛђлЙЛЂЛІ л▓лйлхЛѕлйлИЛЁ л┐ЛђлхЛђЛІл▓л░лйлИл╣ лйл░ л▓ЛІл▓лЙл┤л░ЛЁ INT7 РђЊ INT0

ЛЈл▓л╗ЛЈЛјЛѓЛЂЛЈ л░л║ЛѓлИл▓лйЛІл╝лИ, лхЛЂл╗лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлй Лёл╗л░л│ I Лђлхл│лИЛЂЛѓЛђл░ SREG лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйл░

ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅл░ЛЈ л╝л░ЛЂл║л░ л▓ Лђлхл│лИЛЂЛѓЛђлх EIMSK. лЌл░л┐ЛђлЙЛЂ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ л╗лЙл│лИЛЄлхЛЂл║лЙл╝ЛЃ ЛЃЛђлЙл▓лйЛј

лИл╗лИ ЛёЛђлЙлйЛѓл░л╝ лЙл┐Лђлхл┤лхл╗ЛЈлхЛѓЛЂЛЈ л▓ ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓лИлИ ЛЂ Лѓл░л▒л╗. 7.

лбл░л▒л╗лИЛєл░ 7

лБл┐Лђл░л▓л╗лхлйлИлх

лЙл┐лЙлилйл░л▓л░лйлИлхл╝ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ

|

ISCx1 |

ISCx0 |

лъл┐лИЛЂл░лйлИлх |

|

0 |

0 |

лЌл░л┐ЛђлЙЛЂ

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л│лхлйлхЛђлИЛђЛЃлхЛѓЛЂЛЈ┬а лйлИлил║лИл╝

ЛЃЛђлЙл▓лйлхл╝┬а лйл░ INTx |

|

0 |

1 |

лЌл░ЛђлхлилхЛђл▓лИЛђлЙл▓л░лйлЙ |

|

1 |

0 |

лЌл░л┐ЛђлЙЛЂ

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л│лхлйлхЛђлИЛђЛЃлхЛѓЛЂЛЈ ЛЂл┐л░л┤л░ЛјЛЅлИл╝ ЛёЛђлЙлйЛѓлЙл╝┬а

лйл░ INTx |

|

1 |

1 |

лЌл░л┐ЛђлЙЛЂ

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л│лхлйлхЛђлИЛђЛЃлхЛѓЛЂЛЈ лйл░Лђл░ЛЂЛѓл░ЛјЛЅлИл╝ ЛёЛђлЙлйЛѓлЙл╝┬а

лйл░ INTx |

лЪЛђлИл╝лхЛЄл░лйлИлх. лЦ л╝лЙлХлхЛѓ л▒ЛІЛѓЛї Лђл░л▓лхлй 7, 6, 5,

4, 3, 2, 1 лИл╗лИ 0. лЪЛђлИ лИлил╝лхлйлхлйлИлИ л▒лИЛѓлЙл▓ ISCx1/ISCx0 л┐ЛђлхЛђЛІл▓л░лйлИлх

л┤лЙл╗лХлйлЙ л▒ЛІЛѓЛї лил░л┐ЛђлхЛЅлхлйлЙ лЙЛЄлИЛЂЛѓл║лЙл╣ л▒лИЛѓл░ Лђл░лиЛђлхЛѕлхлйлИЛЈ л▓ Лђлхл│лИЛЂЛѓЛђлх GIMSK. лњ лИлйлЙл╝ ЛЂл╗ЛЃЛЄл░лх

л╝лЙлХлхЛѓ л┐ЛђлЙлИлилЙл╣ЛѓлИ л┐ЛђлхЛђЛІл▓л░лйлИлх л▓ л╝лЙл╝лхлйЛѓ лИлил╝лхлйлхлйлИЛЈ л▒лИЛѓл░.

лњЛЁлЙл┤ЛІ л┐ЛђлхЛђЛІл▓л░лйлИл╣ INTx л┐лхЛђлИлЙл┤лИЛЄлхЛЂл║лИ лЙл┐Лђл░ЛѕлИл▓л░ЛјЛѓЛЂЛЈ лйл░ л┐Лђлхл┤л╝лхЛѓ лйл░л╗лИЛЄлИЛЈ лил░л┐ЛђлЙЛЂл░.

лЋЛЂл╗лИ л▓лйлхЛѕлйлИл╣ лил░л┐ЛђлЙЛЂ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ ЛёлИл║ЛЂлИЛђЛЃлхЛѓЛЂЛЈ л┐лЙ ЛёЛђлЙлйЛѓЛЃ, ЛѓлЙ л┤л╗ЛЈ л│л░Лђл░лйЛѓлИЛђлЙл▓л░лйлйлЙл│лЙ

ЛЂЛђл░л▒л░ЛѓЛІл▓л░лйлИЛЈ л┤л╗лИЛѓлхл╗ЛїлйлЙЛЂЛѓЛї лИл╝л┐ЛЃл╗ЛїЛЂл░ л┤лЙл╗лХлйл░ л▒ЛІЛѓЛї л▒лЙл╗ЛїЛѕлх, ЛЄлхл╝ лЙл┤лИлй л┐лхЛђлИлЙл┤ Лѓл░л║ЛѓлЙл▓лЙл╣

ЛЄл░ЛЂЛѓлЙЛѓЛІ л┐ЛђлЙЛєлхЛЂЛЂлЙЛђл░. лЌл░л╝лхЛѓлИл╝, ЛЄЛѓлЙ ЛЄл░ЛЂЛѓлЙЛѓл░ л┐ЛђлЙЛєлхЛЂЛЂлЙЛђл░ л╝лЙлХлхЛѓ л▒ЛІЛѓЛї л╝лхлйЛїЛѕлх ЛЄл░ЛЂЛѓлЙЛѓЛІ XTAL лИли-лил░ л▓лЙлил╝лЙлХлйлЙл│лЙ лйл░л╗лИЛЄлИЛЈ л┤лхл╗лИЛѓлхл╗ЛЈ. лЌл░л┐ЛђлЙЛЂ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ

л┐лЙ л╗лЙл│лИЛЄлхЛЂл║лЙл╝ЛЃ ЛЃЛђлЙл▓лйЛј л┤лЙл╗лХлхлй л┐ЛђлЙл┤лЙл╗лХл░ЛѓЛїЛЂЛЈ, л┐лЙл║л░ л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ Лѓлхл║ЛЃЛЅл░ЛЈ лИлйЛЂЛѓЛђЛЃл║ЛєлИЛЈ лИ лЙлй л▒ЛЃл┤лхЛѓ лил░ЛёлИл║ЛЂлИЛђлЙл▓л░лй. лЌл░л┐ЛђлЙЛЂ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ

л╗лЙл│лИЛЄлхЛЂл║лЙл╝ЛЃ┬а ЛЃЛђлЙл▓лйЛј, лхЛЂл╗лИ лЙлй Лђл░лиЛђлхЛѕлхлй,

л▒ЛЃл┤лхЛѓ л│лхлйлхЛђлИЛђлЙл▓л░ЛѓЛї лил░л┐ЛђлЙЛЂ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┤лЙ ЛѓлхЛЁ л┐лЙЛђ, л┐лЙл║л░ лйл░ л▓ЛЁлЙл┤лх ЛЃл┤лхЛђлХлИл▓л░лхЛѓЛЂЛЈ

лйлИлил║лИл╣ ЛЃЛђлЙл▓лхлйЛї.

лалхл│лИЛЂЛѓЛђ л╝л░ЛЂлЙл║

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ Лѓл░л╣л╝лхЛђл░л╝/ЛЂЛЄлхЛѓЛЄлИл║л░л╝┬а TIMSK:

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

$37 ($57) |

OCIE2

|

TOIE2

|

TICIE1

|

OCIE1A

|

OCIE1B

|

TOIE1

|

OCIE0

|

TOIE0

|

TIMSK

|

|

лўЛЂЛЁлЙл┤лйлЙлх лилйл░ЛЄлхлйлИлх |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

лЉлИЛѓ 7 РђЊ OCIE2:┬а лал░лиЛђлхЛѕлхлйлИлх

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј Лѓл░л╣л╝лхЛђл░ 2.

лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх OCIE2 лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░

Лђл░лиЛђлхЛѕл░лхЛѓЛЂЛЈ л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛђл░л▓лйлхлйлИЛЈ лИ ЛЂлЙЛЂЛѓлЙЛЈлйлИЛЈ

Лѓл░л╣л╝лхЛђл░ 2. лАлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхлх л┐ЛђлхЛђЛІл▓л░лйлИлх (ЛЂ л▓лхл║ЛѓлЙЛђлЙл╝ $0012) лИл╝лхлхЛѓ л╝лхЛЂЛѓлЙ, лхЛЂл╗лИ

л┐ЛђлЙлИлилЙл╣л┤лхЛѓ ЛЂлЙл▓л┐л░л┤лхлйлИлх л┐ЛђлИ ЛЂЛђл░л▓лйлхлйлИлИ ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛђл░л▓лйлхлйлИЛЈ лИ ЛЂлЙЛЂЛѓлЙЛЈлйлИЛЈ

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ 2. лњ Лђлхл│лИЛЂЛѓЛђлх Лёл╗л░л│лЙл▓ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ TIFR ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ┬а Лёл╗л░л│ OCF2.

лЉлИЛѓ 6 РђЊ TOIE2:┬а

лал░лиЛђлхЛѕлхлйлИлх л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛј Лѓл░л╣л╝лхЛђл░ 2. лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх TOIE2 лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I

Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░ Лђл░лиЛђлхЛѕл░лхЛѓЛЂЛЈ л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛј Лѓл░л╣л╝лхЛђл░ 2. лАлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхлх

л┐ЛђлхЛђЛІл▓л░лйлИлх (ЛЂ л▓лхл║ЛѓлЙЛђлЙл╝ $0014) л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ, лхЛЂл╗лИ л┐ЛђлЙлИлилЙл╣л┤лхЛѓ л┐лхЛђлхл┐лЙл╗лйлхлйлИлх Лѓл░л╣л╝лхЛђл░

2. лњ Лђлхл│лИЛЂЛѓЛђлх Лёл╗л░л│лЙл▓ TIFR ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ┬а

Лёл╗л░л│ TOV2 л┐лхЛђлхл┐лЙл╗лйлхлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 2.

лЉлИЛѓ 5 РђЊ TICIE1:┬а лал░лиЛђлхЛѕлхлйлИлх

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ лил░ЛЁл▓л░ЛѓЛЃ Лѓл░л╣л╝лхЛђл░ 1. лЪЛђлИ

ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх TICIE1 лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░ Лђл░лиЛђлхЛѕл░лхЛѓЛЂЛЈ

л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ лил░ЛЁл▓л░ЛѓЛЃ Лѓл░л╣л╝лхЛђл░ 1. лАлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхлх л┐ЛђлхЛђЛІл▓л░лйлИлх (ЛЂ л▓лхл║ЛѓлЙЛђлЙл╝ $0016)

л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ, лхЛЂл╗лИ л┐ЛђлЙлИлилЙЛѕлхл╗ лил░ЛЁл▓л░Лѓ л┐лЙ л▓ЛІл▓лЙл┤ЛЃ 29, PD4(IC1). лњ Лђлхл│лИЛЂЛѓЛђлх Лёл╗л░л│лЙл▓

TIFR ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ Лёл╗л░л│ ICF1 лил░ЛЁл▓л░Лѓл░ Лѓл░л╣л╝лхЛђл░

1.

лЉлИЛѓ 4 РђЊ OCIE1A:┬а лал░лиЛђлхЛѕлхлйлИлх л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј Лђлхл│лИЛЂЛѓЛђл░ лљ ЛЂ Лѓл░л╣л╝лхЛђлЙл╝ 1.

лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх OCIE1A лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░

Лђл░лиЛђлхЛѕл░лхЛѓЛЂЛЈ л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј Лђлхл│лИЛЂЛѓЛђл░ A ЛЂ ЛЂлЙЛЂЛѓлЙЛЈлйлИлхл╝ Лѓл░л╣л╝лхЛђл░ 1.

лАлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхлх л┐ЛђлхЛђЛІл▓л░лйлИлх (ЛЂ л▓лхл║ЛѓлЙЛђлЙл╝ $0018) л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ, лхЛЂл╗лИ лИл╝лхлхЛѓЛЂЛЈ ЛЂлЙл▓л┐л░л┤лхлйлИлх

ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░ A ЛЂ ЛЂлЙЛЂЛѓлЙЛЈлйлИлхл╝ Лѓл░л╣л╝лхЛђл░ 1. лњ Лђлхл│лИЛЂЛѓЛђлх Лёл╗л░л│лЙл▓ TIFR

ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ┬а Лёл╗л░л│ OCF1A

ЛЂлЙл▓л┐л░л┤лхлйлИЛЈ┬а Лђлхл│лИЛЂЛѓЛђл░ лљ

ЛЂ Лѓл░л╣л╝лхЛђлЙл╝ 1.

лЉлИЛѓ 3 РђЊ OCIE1B:┬а лал░лиЛђлхЛѕлхлйлИлх л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј┬а Лђлхл│лИЛЂЛѓЛђл░ B ЛЂ Лѓл░л╣л╝лхЛђлЙл╝ 1. лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх OCIE1B лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I

Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░ Лђл░лиЛђлхЛѕл░лхЛѓЛЂЛЈ л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј Лђлхл│лИЛЂЛѓЛђл░ B ЛЂ ЛЂлЙЛЂЛѓлЙЛЈлйлИлхл╝

Лѓл░л╣л╝лхЛђл░ 1. лАлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхлх л┐ЛђлхЛђЛІл▓л░лйлИлх (ЛЂ л▓лхл║ЛѓлЙЛђлЙл╝ $001A) л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ, лхЛЂл╗лИ

лИл╝лхлхЛѓЛЂЛЈ ЛЂлЙл▓л┐л░л┤лхлйлИлх ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░ B ЛЂ ЛЂлЙЛЂЛѓлЙЛЈлйлИлхл╝ Лѓл░л╣л╝лхЛђл░ 1. лњ Лђлхл│лИЛЂЛѓЛђлх

Лёл╗л░л│лЙл▓ TIFR ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ┬а Лёл╗л░л│ OCF1B ЛЂлЙл▓л┐л░л┤лхлйлИЛЈ Лђлхл│лИЛЂЛѓЛђл░ B ЛЂ Лѓл░л╣л╝лхЛђлЙл╝ 1.

лЉлИЛѓ 2 РђЊ TOIE1:┬а

лал░лиЛђлхЛѕлхлйлИлх л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛј Лѓл░л╣л╝лхЛђл░ 1. лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх TOIE1 лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░ Лђл░лиЛђлхЛѕл░лхЛѓЛЂЛЈ

л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛј Лѓл░л╣л╝лхЛђл░ 1. лАлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхлх л┐ЛђлхЛђЛІл▓л░лйлИлх (ЛЂ л▓лхл║ЛѓлЙЛђлЙл╝

$001лА) л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ, лхЛЂл╗лИ л┐ЛђлЙлИлилЙл╣л┤лхЛѓ л┐лхЛђлхл┐лЙл╗лйлхлйлИлх Лѓл░л╣л╝лхЛђл░ 1. лњ Лђлхл│лИЛЂЛѓЛђлх Лёл╗л░л│лЙл▓

TIFR ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ Лёл╗л░л│ TOV1

л┐лхЛђлхл┐лЙл╗лйлхлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 1.

лЉлИЛѓ 1 РђЊ OCIE0:┬а лал░лиЛђлхЛѕлхлйлИлх

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј Лѓл░л╣л╝лхЛђл░ 0. лЪЛђлИ

ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх OCIE0 лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░ Лђл░лиЛђлхЛѕл░лхЛѓЛЂЛЈ л┐ЛђлхЛђЛІл▓л░лйлИлх

л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛђл░л▓лйлхлйлИЛЈ лИ ЛЂлЙЛЂЛѓлЙЛЈлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 0.

лАлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхлх л┐ЛђлхЛђЛІл▓л░лйлИлх (ЛЂ л▓лхл║ЛѓлЙЛђлЙл╝ $001E) л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ, лхЛЂл╗лИ л┐ЛђлЙлИлилЙл╣л┤лхЛѓ

ЛЂлЙл▓л┐л░л┤лхлйлИлх л┐ЛђлИ ЛЂЛђл░л▓лйлхлйлИлИ ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛђл░л▓лйлхлйлИЛЈ лИ ЛЂлЙЛЂЛѓлЙЛЈлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 0.

лњ Лђлхл│лИЛЂЛѓЛђлх Лёл╗л░л│лЙл▓ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ TIFR ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ Лёл╗л░л│ OCF0 ЛЂлЙл▓л┐л░л┤лхлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 0.

лЉлИЛѓ 0 РђЊ TOIE0:┬а

лал░лиЛђлхЛѕлхлйлИлх л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛј Лѓл░л╣л╝лхЛђл░ 0. лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх TOIE0 лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I

Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░ Лђл░лиЛђлхЛѕл░лхЛѓЛЂЛЈ л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛј Лѓл░л╣л╝лхЛђл░ 0. лАлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхлх

л┐ЛђлхЛђЛІл▓л░лйлИлх (ЛЂ л▓лхл║ЛѓлЙЛђлЙл╝ $0020) л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ, лхЛЂл╗лИ л┐ЛђлЙлИлилЙл╣л┤лхЛѓ л┐лхЛђлхл┐лЙл╗лйлхлйлИлх Лѓл░л╣л╝лхЛђл░

0. лњ Лђлхл│лИЛЂЛѓЛђлх Лёл╗л░л│лЙл▓ TIFR ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ┬а

Лёл╗л░л│ TOV0 л┐лхЛђлхл┐лЙл╗лйлхлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 0.

лалхл│лИЛЂЛѓЛђ л╝л░ЛЂлЙл║

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ Лѓл░л╣л╝лхЛђл░л╝/ЛЂЛЄлхЛѓЛЄлИл║л░л╝┬а ETIMSK:

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

$7D |

-

|

-

|

TICIE3

|

OCIE3A

|

OCIE3B

|

TOIE3

|

OCIE3C

|

OCIE1C

|

ETIMSK

|

|

лўЛЂЛЁлЙл┤лйлЙлх лилйл░ЛЄлхлйлИлх |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

лЉлИЛѓ 7, л▒лИЛѓ 6 РђЊ лЌл░ЛђлхлилхЛђл▓лИЛђлЙл▓л░лйлЙ.

лЉлИЛѓ 5 РђЊ TICIE3:┬а лал░лиЛђлхЛѕлхлйлИлх

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ лил░ЛЁл▓л░ЛѓЛЃ Лѓл░л╣л╝лхЛђл░ 3. лЪЛђлИ

ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх TICIE3 лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░ Лђл░лиЛђлхЛѕл░лхЛѓЛЂЛЈ

л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ лил░ЛЁл▓л░ЛѓЛЃ Лѓл░л╣л╝лхЛђл░ 3. лАлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхлх л┐ЛђлхЛђЛІл▓л░лйлИлх (ЛЂ л▓лхл║ЛѓлЙЛђлЙл╝ $0032)

л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ, лхЛЂл╗лИ л┐ЛђлЙлИлилЙЛѕлхл╗ лил░ЛЁл▓л░Лѓ л┐лЙ л▓ЛІл▓лЙл┤ЛЃ 9, PE7(ICP3). лњ Лђлхл│лИЛЂЛѓЛђлх

Лёл╗л░л│лЙл▓ ETIFR ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ Лёл╗л░л│ ICF3C лил░ЛЁл▓л░Лѓл░

Лѓл░л╣л╝лхЛђл░ 3.

лЉлИЛѓ 4 РђЊ OCIE3A:-

лал░лиЛђлхЛѕлхлйлИлх л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј Лђлхл│лИЛЂЛѓЛђл░ лљ ЛЂ Лѓл░л╣л╝лхЛђлЙл╝

3. лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх OCIE3A лИ

ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░ Лђл░лиЛђлхЛѕл░лхЛѓЛЂЛЈ л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј

Лђлхл│лИЛЂЛѓЛђл░ A ЛЂ ЛЂлЙЛЂЛѓлЙЛЈлйлИлхл╝ Лѓл░л╣л╝лхЛђл░ 3. лАлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхлх л┐ЛђлхЛђЛІл▓л░лйлИлх (ЛЂ л▓лхл║ЛѓлЙЛђлЙл╝

$0034) л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ, лхЛЂл╗лИ лИл╝лхлхЛѓЛЂЛЈ ЛЂлЙл▓л┐л░л┤лхлйлИлх ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░ A ЛЂ ЛЂлЙЛЂЛѓлЙЛЈлйлИлхл╝

Лѓл░л╣л╝лхЛђл░ 3. лњ Лђлхл│лИЛЂЛѓЛђлх Лёл╗л░л│лЙл▓ ETIFR

ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ┬а Лёл╗л░л│ OCF3A

ЛЂлЙл▓л┐л░л┤лхлйлИЛЈ┬а Лђлхл│лИЛЂЛѓЛђл░ лљ

ЛЂ Лѓл░л╣л╝лхЛђлЙл╝ 3.

лЉлИЛѓ 3 РђЊ OCIE3B:┬а лал░лиЛђлхЛѕлхлйлИлх л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј┬а Лђлхл│лИЛЂЛѓЛђл░ B ЛЂ Лѓл░л╣л╝лхЛђлЙл╝ 3. лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх OCIE3B лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I

Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░ Лђл░лиЛђлхЛѕл░лхЛѓЛЂЛЈ л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј Лђлхл│лИЛЂЛѓЛђл░ B ЛЂ ЛЂлЙЛЂЛѓлЙЛЈлйлИлхл╝

Лѓл░л╣л╝лхЛђл░ 3. лАлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхлх л┐ЛђлхЛђЛІл▓л░лйлИлх (ЛЂ л▓лхл║ЛѓлЙЛђлЙл╝ $0036) л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ, лхЛЂл╗лИ

лИл╝лхлхЛѓЛЂЛЈ ЛЂлЙл▓л┐л░л┤лхлйлИлх ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░ B ЛЂ ЛЂлЙЛЂЛѓлЙЛЈлйлИлхл╝ Лѓл░л╣л╝лхЛђл░ 3. лњ Лђлхл│лИЛЂЛѓЛђлх

Лёл╗л░л│лЙл▓ ETIFR ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ┬а

Лёл╗л░л│ OCF3B ЛЂлЙл▓л┐л░л┤лхлйлИЛЈ Лђлхл│лИЛЂЛѓЛђл░ B ЛЂ Лѓл░л╣л╝лхЛђлЙл╝ 3.

лЉлИЛѓ 2 РђЊ TOIE3:- лал░лиЛђлхЛѕлхлйлИлх л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛј

Лѓл░л╣л╝лхЛђл░ 3. лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх TOIE3 лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░ Лђл░лиЛђлхЛѕл░лхЛѓЛЂЛЈ

л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛј Лѓл░л╣л╝лхЛђл░ 3. лАлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхлх л┐ЛђлхЛђЛІл▓л░лйлИлх (ЛЂ л▓лхл║ЛѓлЙЛђлЙл╝ $003A) л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ, лхЛЂл╗лИ л┐ЛђлЙлИлилЙл╣л┤лхЛѓ л┐лхЛђлхл┐лЙл╗лйлхлйлИлх Лѓл░л╣л╝лхЛђл░ 3.

лњ Лђлхл│лИЛЂЛѓЛђлх Лёл╗л░л│лЙл▓ ETIFR ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ Лёл╗л░л│ TOV3 л┐лхЛђлхл┐лЙл╗лйлхлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 3.

лЉлИЛѓ 1 РђЊ OCIE3C:┬а лал░лиЛђлхЛѕлхлйлИлх л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј Лђлхл│лИЛЂЛѓЛђл░ C ЛЂ Лѓл░л╣л╝лхЛђлЙл╝ 3. лЪЛђлИ

ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх OCIE3лА лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░ Лђл░лиЛђлхЛѕл░лхЛѓЛЂЛЈ

л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛђл░л▓лйлхлйлИЛЈ C ЛЂ ЛЂлЙЛЂЛѓлЙЛЈлйлИлхл╝ Лѓл░л╣л╝лхЛђл░ 3. лАлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхлх л┐ЛђлхЛђЛІл▓л░лйлИлх (ЛЂ

л▓лхл║ЛѓлЙЛђлЙл╝ $0038) л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ, лхЛЂл╗лИ л┐ЛђлЙлИлилЙл╣л┤лхЛѓ ЛЂлЙл▓л┐л░л┤лхлйлИлх л┐ЛђлИ ЛЂЛђл░л▓лйлхлйлИлИ ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ

Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛђл░л▓лйлхлйлИЛЈ C лИ ЛЂлЙЛЂЛѓлЙЛЈлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 3. лњ

Лђлхл│лИЛЂЛѓЛђлх Лёл╗л░л│лЙл▓ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ ETIFR

ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ Лёл╗л░л│ OCF3C ЛЂлЙл▓л┐л░л┤лхлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 3.

лЉлИЛѓ 0 РђЊ OCIE1C:┬а лал░лиЛђлхЛѕлхлйлИлх л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј Лђлхл│лИЛЂЛѓЛђл░ C ЛЂ Лѓл░л╣л╝лхЛђлЙл╝ 1. лЪЛђлИ

ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх OCIE1лА лИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛѓл░ЛѓЛЃЛЂл░ Лђл░лиЛђлхЛѕл░лхЛѓЛЂЛЈ

л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛђл░л▓лйлхлйлИЛЈ C ЛЂ ЛЂлЙЛЂЛѓлЙЛЈлйлИлхл╝ Лѓл░л╣л╝лхЛђл░ 1. лАлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхлх л┐ЛђлхЛђЛІл▓л░лйлИлх (ЛЂ

л▓лхл║ЛѓлЙЛђлЙл╝ $0030) л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ, лхЛЂл╗лИ л┐ЛђлЙлИлилЙл╣л┤лхЛѓ ЛЂлЙл▓л┐л░л┤лхлйлИлх л┐ЛђлИ ЛЂЛђл░л▓лйлхлйлИлИ ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ

Лђлхл│лИЛЂЛѓЛђл░ ЛЂЛђл░л▓лйлхлйлИЛЈ C лИ ЛЂлЙЛЂЛѓлЙЛЈлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 1. лњ

Лђлхл│лИЛЂЛѓЛђлх Лёл╗л░л│лЙл▓ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ ETIFR

ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ Лёл╗л░л│ OCF1C ЛЂлЙл▓л┐л░л┤лхлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 1.

лалхл│лИЛЂЛѓЛђ Лёл╗л░л│лЙл▓ л┐ЛђлхЛђЛІл▓л░лйлИл╣ л┐лЙ Лѓл░л╣л╝лхЛђл░л╝/ЛЂЛЄлхЛѓЛЄлИл║л░л╝┬а TIFR:

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

$36 ($56) |

OCF2

|

TOV2

|

ICF1

|

OCF1A

|

OCF1B

|

TOV1

|

OCF0

|

TOV0

|

TIFR

|

|

лўЛЂЛЁлЙл┤лйлЙлх лилйл░ЛЄлхлйлИлх |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

лЉлИЛѓ 7 РђЊ OCF2:┬а лцл╗л░л│ 2

ЛЂлЙл▓л┐л░л┤лхлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 2 лИ л┤л░лйлйЛІЛЁ OCR2. лЉлИЛѓ OCF2 ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ л┐ЛђлИ ЛЂлЙл▓л┐л░л┤лхлйлИлИ ЛЂлЙЛЂЛѓлЙЛЈлйлИЛЈ

Лѓл░л╣л╝лхЛђл░ 2 лИ ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░ OCR2. лЉлИЛѓ OCF2 л░л┐л┐л░Лђл░ЛѓлйлЙ лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ л┐ЛђлИ

лЙл▒Лђл░л▒лЙЛѓл║лх ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхл│лЙ л▓лхл║ЛѓлЙЛђл░ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лњлЙлил╝лЙлХлйл░ лЙЛЄлИЛЂЛѓл║л░ л▒лИЛѓл░ лил░л┐лИЛЂЛїЛј л▓лЙ

Лёл╗л░л│ л╗лЙл│лИЛЄлхЛЂл║лЙл╣ 1. лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйЛІЛЁ л▒лИЛѓл░ЛЁ I л▓ Лђлхл│лИЛЂЛѓЛђл░ЛЁ SREG, OCIE2 лИ OCF2

л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј Лѓл░л╣л╝лхЛђл░ 2.

лЉлИЛѓ 6 РђЊ┬а

TOV2:┬а лцл╗л░л│ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛЈ Лѓл░л╣л╝лхЛђл░

2. лЉлИЛѓ TOV2 ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ л┐ЛђлИ

л┐лхЛђлхл┐лЙл╗лйлхлйлИлИ Лѓл░л╣л╝лхЛђл░ 2. лълй л░л┐л┐л░Лђл░ЛѓлйлЙ лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ л┐ЛђлИ лЙл▒Лђл░л▒лЙЛѓл║лх ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхл│лЙ

л▓лхл║ЛѓлЙЛђл░ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лњлЙлил╝лЙлХлйл░ лЙЛЄлИЛЂЛѓл║л░ л▒лИЛѓл░ лил░л┐лИЛЂЛїЛј л▓лЙ Лёл╗л░л│ л╗лЙл│лИЛЄлхЛЂл║лЙл╣ 1. лЪЛђлИ

ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I л▓┬а Лђлхл│лИЛЂЛѓЛђлх SREG,

ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйЛІЛЁ л▒лИЛѓл░ЛЁ OCIE2 лИ TOV2 л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛј Лѓл░л╣л╝лхЛђл░

2. лњ ЛђлхлХлИл╝лх PWM ЛЇЛѓлЙЛѓ л▒лИЛѓ ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ, л┐ЛђлИ л┐лхЛђлхЛЁлЙл┤лх ЛЄлхЛђлхли $00.

лЉлИЛѓ 5 РђЊ ICF1:┬а лцл╗л░л│ лил░ЛЁл▓л░Лѓл░

л▓ЛЁлЙл┤л░. лЉлИЛѓ ICF1 ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ л▓ ЛЂл╗ЛЃЛЄл░лх лил░ЛЁл▓л░Лѓл░ л▓ЛЁлЙл┤л░ лИ л┐лЙл║л░лиЛІл▓л░лхЛѓ,

ЛЄЛѓлЙ лилйл░ЛЄлхлйлИлх Лѓл░л╣л╝лхЛђл░ 1 л┐лхЛђлхЛЂл╗л░лйлЙ л▓лЙ л▓ЛЁлЙл┤лйлЙл╣ Лђлхл│лИЛЂЛѓЛђ лил░ЛЁл▓л░Лѓл░ ICR1. лЉлИЛѓ лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ

л░л┐л┐л░Лђл░ЛѓлйлЙ л┐ЛђлИ лЙл▒Лђл░л▒лЙЛѓл║лх ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхл│лЙ л▓лхл║ЛѓлЙЛђл░ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лњлЙлил╝лЙлХлйл░ лЙЛЄлИЛЂЛѓл║л░

л▒лИЛѓл░ лил░л┐лИЛЂЛїЛј л▓лЙ Лёл╗л░л│ л╗лЙл│лИЛЄлхЛЂл║лЙл╣ 1.

лЉлИЛѓ 4 РђЊ OCF1A:┬а лцл╗л░л│ 1A ЛЂлЙл▓л┐л░л┤лхлйлИЛЈ л▓ЛІЛЁлЙл┤л░. лЉлИЛѓ OCF1A ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ л┐ЛђлИ ЛЂлЙл▓л┐л░л┤лхлйлИлИ ЛЂлЙЛЂЛѓлЙЛЈлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 1 лИ

ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░ OCR1A. лЉлИЛѓ OCF1A л░л┐л┐л░Лђл░ЛѓлйлЙ лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ л┐ЛђлИ лЙл▒Лђл░л▒лЙЛѓл║лх

ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхл│лЙ л▓лхл║ЛѓлЙЛђл░ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лњлЙлил╝лЙлХлйл░ лЙЛЄлИЛЂЛѓл║л░ л▒лИЛѓл░ лил░л┐лИЛЂЛїЛј л▓лЙ Лёл╗л░л│ л╗лЙл│лИЛЄлхЛЂл║лЙл╣

1. лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I л▓┬а Лђлхл│лИЛЂЛѓЛђлх

SREG, ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйЛІЛЁ л▒лИЛѓл░ЛЁ OCIE1A лИ OCF1A л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј

л▓ЛІЛЁлЙл┤л░ Лѓл░л╣л╝лхЛђл░-ЛЂЛЄлхЛѓЛЄлИл║л░ 1.

лЉлИЛѓ 3 РђЊ OCF1B:┬а

лцл╗л░л│ 1B ЛЂлЙл▓л┐л░л┤лхлйлИЛЈ л▓ЛІЛЁлЙл┤л░. лЉлИЛѓ

OCF1B ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ л┐ЛђлИ ЛЂлЙл▓л┐л░л┤лхлйлИлИ ЛЂлЙЛЂЛѓлЙЛЈлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 1 лИ ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░

OCR1B. лЉлИЛѓ OCF1B л░л┐л┐л░Лђл░ЛѓлйлЙ лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ л┐ЛђлИ лЙл▒Лђл░л▒лЙЛѓл║лх ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхл│лЙ л▓лхл║ЛѓлЙЛђл░

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лњлЙлил╝лЙлХлйл░ лЙЛЄлИЛЂЛѓл║л░ л▒лИЛѓл░ лил░л┐лИЛЂЛїЛј л▓лЙ Лёл╗л░л│ л╗лЙл│лИЛЄлхЛЂл║лЙл╣ 1. лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝

л▒лИЛѓлх I л▓ Лђлхл│лИЛЂЛѓЛђлх SREG, ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйЛІЛЁ л▒лИЛѓл░ЛЁ OCIE1B лИ OCF1B л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ┬а л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј л▓ЛІЛЁлЙл┤л░ Лѓл░л╣л╝лхЛђл░ 1.

лЉлИЛѓ 2 РђЊ TOV1:┬а

лцл╗л░л│ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 1.

лЉлИЛѓ TOV1 ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ л┐ЛђлИ л┐лхЛђлхл┐лЙл╗лйлхлйлИлИ Лѓл░л╣л╝лхЛђл░ 1. лълй л░л┐л┐л░Лђл░ЛѓлйлЙ лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ л┐ЛђлИ

лЙл▒Лђл░л▒лЙЛѓл║лх ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхл│лЙ л▓лхл║ЛѓлЙЛђл░ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лњлЙлил╝лЙлХлйл░ лЙЛЄлИЛЂЛѓл║л░ л▒лИЛѓл░ лил░л┐лИЛЂЛїЛј л▓лЙ

Лёл╗л░л│ л╗лЙл│лИЛЄлхЛЂл║лЙл╣ 1. лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I л▓┬а

Лђлхл│лИЛЂЛѓЛђлх SREG, ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйЛІЛЁ л▒лИЛѓл░ЛЁ TOIE1 лИ TOV1 л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ┬а л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛј Лѓл░л╣л╝лхЛђл░ 1.

лЉлИЛѓ 1 РђЊ OCF0:┬а лцл╗л░л│ 0

ЛЂлЙл▓л┐л░л┤лхлйлИЛЈ л▓ЛІЛЁлЙл┤л░. лЉлИЛѓ OCF0

ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ л┐ЛђлИ ЛЂлЙл▓л┐л░л┤лхлйлИлИ ЛЂлЙЛЂЛѓлЙЛЈлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 0 лИ ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░ OCR0

. лЉлИЛѓ OCF0 л░л┐л┐л░Лђл░ЛѓлйлЙ лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ л┐ЛђлИ лЙл▒Лђл░л▒лЙЛѓл║лх ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхл│лЙ л▓лхл║ЛѓлЙЛђл░

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лњлЙлил╝лЙлХлйл░ лЙЛЄлИЛЂЛѓл║л░ л▒лИЛѓл░ лил░л┐лИЛЂЛїЛј л▓лЙ Лёл╗л░л│ л╗лЙл│лИЛЄлхЛЂл║лЙл╣ 1. лЪЛђлИ

ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I л▓ Лђлхл│лИЛЂЛѓЛђлх SREG, ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйЛІЛЁ л▒лИЛѓл░ЛЁ OCIE0 лИ OCF0 л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ

л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј л▓ЛІЛЁлЙл┤л░ Лѓл░л╣л╝лхЛђл░ 1.

лЉлИЛѓ 0 РђЊ TOV0:┬а

лцл╗л░л│ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 0.

лЉлИЛѓ TOV0 ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ л┐ЛђлИ л┐лхЛђлхл┐лЙл╗лйлхлйлИлИ Лѓл░л╣л╝лхЛђл░ 0. лълй л░л┐л┐л░Лђл░ЛѓлйлЙ лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ л┐ЛђлИ

лЙл▒Лђл░л▒лЙЛѓл║лх ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхл│лЙ л▓лхл║ЛѓлЙЛђл░ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лњлЙлил╝лЙлХлйл░ лЙЛЄлИЛЂЛѓл║л░ л▒лИЛѓл░ лил░л┐лИЛЂЛїЛј л▓лЙ

Лёл╗л░л│ л╗лЙл│лИЛЄлхЛЂл║лЙл╣ 1. лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I л▓ Лђлхл│лИЛЂЛѓЛђлх SREG, ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйЛІЛЁ

л▒лИЛѓл░ЛЁ TOIE0 лИ TOV0 л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ┬а

л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛј Лѓл░л╣л╝лхЛђл░ 0.

лалхл│лИЛЂЛѓЛђ Лёл╗л░л│лЙл▓ л┐ЛђлхЛђЛІл▓л░лйлИл╣ л┐лЙ Лѓл░л╣л╝лхЛђл░л╝/ЛЂЛЄлхЛѓЛЄлИл║л░л╝┬а ETIFR:

|

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

$7C |

-

|

-

|

ICF3C

|

OCF3A

|

OCF3B

|

TOV3

|

OCF3C

|

OCF1C

|

ETIFR

|

|

лўЛЂЛЁлЙл┤лйлЙлх лилйл░ЛЄлхлйлИлх |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

лЉлИЛѓ 7, л▒лИЛѓ 6 РђЊ лЌл░ЛђлхлилхЛђл▓лИЛђлЙл▓л░лйлЙ.

лЉлИЛѓ 5 РђЊ ICF3C:┬а лцл╗л░л│ лил░ЛЁл▓л░Лѓл░ л▓ЛЁлЙл┤л░. лЉлИЛѓ ICF3C ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ л▓ ЛЂл╗ЛЃЛЄл░лх лил░ЛЁл▓л░Лѓл░ л▓ЛЁлЙл┤л░ лИ л┐лЙл║л░лиЛІл▓л░лхЛѓ,

ЛЄЛѓлЙ лилйл░ЛЄлхлйлИлх Лѓл░л╣л╝лхЛђл░ 3 л┐лхЛђлхЛЂл╗л░лйлЙ л▓лЙ л▓ЛЁлЙл┤лйлЙл╣ Лђлхл│лИЛЂЛѓЛђ лил░ЛЁл▓л░Лѓл░ ICR3. лЉлИЛѓ лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ

л░л┐л┐л░Лђл░ЛѓлйлЙ л┐ЛђлИ лЙл▒Лђл░л▒лЙЛѓл║лх ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхл│лЙ л▓лхл║ЛѓлЙЛђл░ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лњлЙлил╝лЙлХлйл░ лЙЛЄлИЛЂЛѓл║л░

л▒лИЛѓл░ лил░л┐лИЛЂЛїЛј л▓лЙ Лёл╗л░л│ л╗лЙл│лИЛЄлхЛЂл║лЙл╣ 1.

лЉлИЛѓ 4 РђЊ OCF3A:┬а лцл╗л░л│ 3A ЛЂлЙл▓л┐л░л┤лхлйлИЛЈ л▓ЛІЛЁлЙл┤л░. лЉлИЛѓ OCF3A ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ л┐ЛђлИ ЛЂлЙл▓л┐л░л┤лхлйлИлИ ЛЂлЙЛЂЛѓлЙЛЈлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 3 лИ ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ

Лђлхл│лИЛЂЛѓЛђл░ OCR3A. лЉлИЛѓ OCF3A л░л┐л┐л░Лђл░ЛѓлйлЙ лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ л┐ЛђлИ лЙл▒Лђл░л▒лЙЛѓл║лх ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхл│лЙ

л▓лхл║ЛѓлЙЛђл░ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лњлЙлил╝лЙлХлйл░ лЙЛЄлИЛЂЛѓл║л░ л▒лИЛѓл░ лил░л┐лИЛЂЛїЛј л▓лЙ Лёл╗л░л│ л╗лЙл│лИЛЄлхЛЂл║лЙл╣ 1. лЪЛђлИ

ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I л▓┬а Лђлхл│лИЛЂЛѓЛђлх SREG,

ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйЛІЛЁ л▒лИЛѓл░ЛЁ OCIE3A лИ OCF3A л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј л▓ЛІЛЁлЙл┤л░

Лѓл░л╣л╝лхЛђл░ 3.

лЉлИЛѓ 3 РђЊ OCF3B:┬а

лцл╗л░л│ 3B ЛЂлЙл▓л┐л░л┤лхлйлИЛЈ л▓ЛІЛЁлЙл┤л░. лЉлИЛѓ

OCF3B ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ л┐ЛђлИ ЛЂлЙл▓л┐л░л┤лхлйлИлИ ЛЂлЙЛЂЛѓлЙЛЈлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 3 лИ ЛЂлЙл┤лхЛђлХлИл╝лЙл│лЙ Лђлхл│лИЛЂЛѓЛђл░

OCR3B. лЉлИЛѓ OCF3B л░л┐л┐л░Лђл░ЛѓлйлЙ лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ л┐ЛђлИ лЙл▒Лђл░л▒лЙЛѓл║лх ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхл│лЙ л▓лхл║ЛѓлЙЛђл░

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лњлЙлил╝лЙлХлйл░ лЙЛЄлИЛЂЛѓл║л░ л▒лИЛѓл░ лил░л┐лИЛЂЛїЛј л▓лЙ Лёл╗л░л│ л╗лЙл│лИЛЄлхЛЂл║лЙл╣ 1. лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝

л▒лИЛѓлх I л▓ Лђлхл│лИЛЂЛѓЛђлх SREG, ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйЛІЛЁ л▒лИЛѓл░ЛЁ OCIE3B лИ OCF3B л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ┬а л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ ЛЂлЙл▓л┐л░л┤лхлйлИЛј л▓ЛІЛЁлЙл┤л░ Лѓл░л╣л╝лхЛђл░ 3.

лЉлИЛѓ 2 РђЊ TOV3:┬а

лцл╗л░л│ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 3.

лЉлИЛѓ TOV3 ЛЃЛЂЛѓл░лйл░л▓л╗лИл▓л░лхЛѓЛЂЛЈ л┐ЛђлИ л┐лхЛђлхл┐лЙл╗лйлхлйлИлИ Лѓл░л╣л╝лхЛђл░ 3. лълй л░л┐л┐л░Лђл░ЛѓлйлЙ лЙЛЄлИЛЅл░лхЛѓЛЂЛЈ л┐ЛђлИ

лЙл▒Лђл░л▒лЙЛѓл║лх ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлхл│лЙ л▓лхл║ЛѓлЙЛђл░ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ. лњлЙлил╝лЙлХлйл░ лЙЛЄлИЛЂЛѓл║л░ л▒лИЛѓл░ лил░л┐лИЛЂЛїЛј л▓лЙ

Лёл╗л░л│ л╗лЙл│лИЛЄлхЛЂл║лЙл╣ 1. лЪЛђлИ ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйлЙл╝ л▒лИЛѓлх I л▓┬а

Лђлхл│лИЛЂЛѓЛђлх SREG, ЛЃЛЂЛѓл░лйлЙл▓л╗лхлйлйЛІЛЁ л▒лИЛѓл░ЛЁ TOIE3 лИ TOV3 л▓ЛІл┐лЙл╗лйЛЈлхЛѓЛЂЛЈ┬а л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛј Лѓл░л╣л╝лхЛђл░ 3.

лЉлИЛѓ 1 РђЊ OCF3C:┬а лцл╗л░л│

лЉлИЛѓ 0 РђЊ OCF1C:┬а лцл╗л░л│

лъл▒Лђл░ЛѓлИЛѓлх л▓лйлИл╝л░лйлИлх, ЛЄЛѓлЙ

л┐ЛђлЙл│Лђл░л╝л╝лйлЙ ЛЃЛЂЛѓл░лйлЙл▓лИЛѓЛї Лёл╗л░л│ Лѓл░л╣л╝лхЛђл░-ЛЂЛЄлхЛѓЛЄлИл║л░, лил░л┐лИЛЂл░л▓ л▓ лйлхл│лЙ 1, лйлхл▓лЙлил╝лЙлХлйлЙ!

2. лњЛІл┐лЙл╗лйлхлйлИлх Лђл░л▒лЙЛѓЛІ

1. лўлиЛЃЛЄлИЛѓЛї ЛёЛЃлйл║ЛєлИлЙлйлИЛђлЙл▓л░лйлИлх л┐лЙл┤ЛЂлИЛЂЛѓлхл╝ЛІ л┐ЛђлхЛђЛІл▓л░лйлИл╣

л╝лИл║ЛђлЙл║лЙлйЛѓЛђлЙл╗л╗лхЛђл░ ATmega128.

2. лЌл░л┐ЛЃЛЂЛѓлИЛѓЛї лйл░ л┐лхЛђЛЂлЙлйл░л╗ЛїлйлЙл╝ л║лЙл╝л┐ЛїЛјЛѓлхЛђлх лИлйЛѓлхл│ЛђлИЛђлЙл▓л░лйлйЛЃЛј

ЛЂлИЛЂЛѓлхл╝ЛЃ л┐ЛђлЙл│Лђл░л╝л╝лИЛђлЙл▓л░лйлИЛЈ AVRStudio. лџлЙл╝л░лйл┤лЙл╣ Project|New Project ЛЂлЙлил┤л░ЛѓЛї

лйлЙл▓ЛІл╣ л┐ЛђлЙлхл║Лѓ Lesson3. лА лИЛЂл┐лЙл╗ЛїлилЙл▓л░лйлИлхл╝ Лђлхл┤л░л║ЛѓлЙЛђл░

Лѓлхл║ЛЂЛѓл░ ЛЂлЙлил┤л░ЛѓЛї л┤лхл╝лЙлйЛЂЛѓЛђл░ЛєлИлЙлйлйЛЃЛј л┐ЛђлЙл│Лђл░л╝л╝ЛЃ:

.device ATmega128

.include┬а┬а┬а┬а┬а "m128def.inc"

;*****Лѓл░л▒л╗лИЛєл░

л▓лхл║ЛѓлЙЛђлЙл▓ л┐ЛђлхЛђЛІл▓л░лйлИл╣*******************

.CSEG

.org┬а┬а $0000┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лйл░ЛЄл░л╗ЛїлйЛІл╣ л░л┤pлхЛЂ л┐pлЙл│pл░л╝л╝ЛІ

┬а┬а rjmp Start;л┐лхpлхЛЁлЙл┤ л║ pл░л▒лЙЛЄлхл╣ ЛЄл░ЛЂЛѓлИ л┐pлЙл│pл░л╝л╝ЛІ (л▓лхл║ЛѓлЙp Reset)

.org┬а┬а $0002

┬а┬а┬а┬а┬а┬а rjmp┬а┬а┬а int_INT0 ;лњлйлхЛѕлйлхлх

л┐pлхpЛІл▓л░лйлИлх Int0

.org┬а┬а $0004

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лњлйлхЛѕлйлхлх л┐pлхpЛІл▓л░лйлИлх Int1

.org┬а┬а $0006

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лњлйлхЛѕлйлхлх л┐pлхpЛІл▓л░лйлИлх Int2

.org┬а┬а $0008

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лњлйлхЛѕлйлхлх л┐pлхpЛІл▓л░лйлИлх Int3

.org┬а┬а $000A

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лњлйлхЛѕлйлхлх л┐pлхpЛІл▓л░лйлИлх Int4

.org┬а┬а $000C

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лњлйлхЛѕлйлхлх л┐pлхpЛІл▓л░лйлИлх Int5

.org┬а┬а $000E

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лњлйлхЛѕлйлхлх л┐pлхpЛІл▓л░лйлИлх Int6

.org┬а┬а $0010

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лњлйлхЛѕлйлхлх л┐pлхpЛІл▓л░лйлИлх Int7

.org┬а┬а $0012

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лАлЙл▓л┐л░л┤лхлйлИлх Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T2

.org┬а┬а $0014

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лЪлхЛђлхл┐лЙл╗лйлхлйлИлх Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T2

.org┬а┬а $0016

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лЌл░ЛЁл▓л░Лѓ Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T1

.org┬а┬а $0018

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лАлЙл▓л┐л░л┤лхлйлИлх "лљ"

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T1

.org┬а┬а $001A

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лАлЙл▓л┐л░л┤лхлйлИлх "лњ"

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T1

.org┬а┬а $001C

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лЪлхЛђлхл┐лЙл╗лйлхлйлИлх Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T1

.org┬а┬а $001E

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лАлЙл▓л┐л░л┤лхлйлИлх Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T0

.org┬а┬а $0020

┬а┬а┬а┬а┬а┬а rjmp┬а┬а┬а OvfT0┬а┬а ;лЪлхЛђлхл┐лЙл╗лйлхлйлИлх

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T0

.org┬а┬а $0022

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лЪлхЛђлхл┤л░ЛЄл░ л┐лЙ SPI лил░л▓лхЛђЛѕлхлйл░

.org┬а┬а $0024

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;USART0, л┐ЛђлИлхл╝ лил░л▓лхЛђЛѕлхлй

.org┬а┬а $0026

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лалхл│лИЛЂЛѓЛђ л┤л░лйлйЛІЛЁ USART0 л┐ЛЃЛЂЛѓ

.org┬а┬а $0028

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;USART0, л┐лхЛђлхл┤л░ЛЄл░ лил░л▓лхЛђЛѕлхлйл░

.org┬а┬а $002A

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лЪЛђлхлЙл▒Лђл░лилЙл▓л░лйлИлх лљлдлЪ лил░л▓лхЛђЛѕлхлйлЙ

.org┬а┬а $002C

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лЌл░л┐лИЛЂЛї л▓ EEPROM лил░л▓лхЛђЛѕлхлйл░

.org┬а┬а $002E

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лљлйл░л╗лЙл│лЙл▓ЛІл╣ л║лЙл╝л┐л░Лђл░ЛѓлЙЛђ

.org┬а┬а $0030

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лАлЙл▓л┐л░л┤лхлйлИлх "C"

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T1

.org┬а┬а $0032

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лЌл░ЛЁл▓л░Лѓ Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T3

.org┬а┬а $0034

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лАлЙл▓л┐л░л┤лхлйлИлх "лљ"

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T3

.org┬а┬а $0036

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лАлЙл▓л┐л░л┤лхлйлИлх "лњ"

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T3

.org┬а┬а $0038

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лАлЙл▓л┐л░л┤лхлйлИлх "C"

Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T3

.org┬а┬а $003A

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лЪлхЛђлхл┐лЙл╗лйлхлйлИлх Лѓл░л╣л╝лхЛђл░/ЛЂЛЄлхЛѓЛЄлИл║л░ T3

.org┬а┬а $003C

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;USART1, л┐ЛђлИлхл╝ лил░л▓лхЛђЛѕлхлй

.org┬а┬а $003E

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лалхл│лИЛЂЛѓЛђ л┤л░лйлйЛІЛЁ USART1 л┐ЛЃЛЂЛѓ

.org┬а┬а $0040

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;USART1, л┐лхЛђлхл┤л░ЛЄл░ лил░л▓лхЛђЛѕлхлйл░

.org┬а┬а $0042

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лЪЛђлхЛђЛІл▓л░лйлИлх лЙЛѓ л╝лЙл┤ЛЃл╗ЛЈ TWI

.org┬а┬а $0044

┬а┬а┬а┬а┬а┬а reti┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;лЊлЙЛѓлЙл▓лйлЙЛЂЛѓЛї SPM

;*****

лъЛЂлйлЙл▓лйл░ЛЈ л┐ЛђлЙл│Лђл░л╝л╝л░************************************

Start:

┬а┬а┬а┬а┬а┬а Ldi R16,High(RAMEND)┬а ;лИлйлИЛєлИл░л╗лИлил░ЛєлИЛЈ ЛЂЛѓлхл║л░

┬а┬а┬а┬а┬а┬а Out SPH,R16

┬а┬а┬а┬а┬а┬а Ldi R16,Low(RAMEND)

┬а┬а┬а┬а┬а┬а Out SPL,R16

;*****лйл░ЛЂЛѓЛђлЙл╣л║л░

л╗лИлйлИлИ INT0 л┤л╗ЛЈ л┐ЛђлЙл│Лђл░л╝л╝лйлЙл│лЙ ЛЂлИл╝ЛЃл╗ЛЈЛѓлЙЛђл░******

┬а┬а In┬а R16,DDRD

┬а┬а Sbr

R16,(1<<PD0)┬а┬а┬а ;ЛЃЛЂЛѓл░лйлЙл▓л║л░ л╗лИлйлИлИ

л┐лЙЛђЛѓл░ INT0 лйл░ л▓ЛІЛЁлЙл┤

┬а┬а Out DDRD, R16 ;Лђл░лиЛђлхЛѕлхлйлИлх Лђл░л▒лЙЛѓЛІ л╗лИлйлИлИ л┐лЙЛђЛѓл░ INT0 лйл░ л▓ЛІЛЁлЙл┤

┬а┬а Sbi PORTD,PD0 ;ЛЃЛЂЛѓл░лйлЙл▓л║л░ л▓ЛІЛЂлЙл║лЙл│лЙ ЛЃЛђлЙл▓лйЛЈ лйл░ л▓ЛІЛЁлЙл┤лх INT0

;***********************************************************

┬а┬а┬а┬а┬а┬а In┬а R16,TCCR0;ЛЃЛЂЛѓл░лйлЙл▓л║л░ л▒лИЛѓл░ CS00,Лѓл░л║ЛѓлИЛђлЙл▓л░лйлИлх

Лѓл░л╣л╝лхЛђл░

┬а┬а┬а┬а┬а┬а Sbr

R16,(1<<CS00)┬а┬а┬а┬а ; ЛЄл░ЛЂЛѓлЙЛѓлЙл╣

л┐ЛђлЙЛєлхЛЂЛЂлЙЛђл░

┬а┬а┬а┬а┬а┬а Out TCCR0, R16┬а┬а┬а┬а┬а┬а┬а ;Лђл░лиЛђлхЛѕлхлйлИлх Лђл░л▒лЙЛѓЛІ Лѓл░л╣л╝лхЛђл░ 0

┬а┬а┬а┬а┬а┬а In R16,TIMSK

┬а┬а┬а┬а┬а┬а Sbr

R16,(1<<TOIE0)┬а┬а┬а ;ЛЃЛЂЛѓл░лйлЙл▓л║л░ л▒лИЛѓл░

TOIE0

┬а┬а┬а┬а┬а┬а Out TIMSK, R16;Лђл░лиЛђлхЛѕлхлйлИлх

л┐ЛђлхЛђЛІл▓л░лйлИЛЈ л┐лЙ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛј Лѓл░л╣л╝лхЛђл░ 0

┬а┬а┬а┬а┬а┬а In┬а R16,EIMSK

┬а┬а┬а┬а┬а┬а Sbr

R16,(1<<INT0)┬а┬а┬а┬а ;ЛЃЛЂЛѓл░лйлЙл▓л║л░ л▒лИЛѓл░

INT0

┬а┬а┬а┬а┬а┬а Out EIMSK, R16┬а ;Лђл░лиЛђлхЛѕлхлйлИлх л┐ЛђлхЛђЛІл▓л░лйлИЛЈ INT0 лЙЛѓ

лйлИлил║лЙл│лЙ

┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;ЛЃЛђлЙл▓лйЛЈ

лйл░ л▓ЛЁлЙл┤лх INT0

┬а┬а┬а┬а┬а┬а sei┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ;Лђл░лиЛђлхЛѕлхлйлИлх л▓ЛЂлхЛЁ л┐ЛђлхЛђЛІл▓л░лйлИл╣

loop:┬а

┬а┬а┬а┬а┬а┬а rjmp┬а loop;лил░ЛєлИл║л╗лИл▓л░лйлИлх

л┐ЛђлЙл│Лђл░л╝л╝ЛІ л┤лЙ л┐ЛђлИЛЁлЙл┤л░ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ

;*****

лъл▒Лђл░л▒лЙЛѓл║л░ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ Int0: **************************

int_INT0:

┬а┬а┬а┬а┬а┬а nop

┬а┬а┬а┬а┬а┬а reti

;*****

лъл▒Лђл░л▒лЙЛѓл║л░ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ Лѓл░л╣л╝лхЛђл░0 ********************

OvfT0:

┬а┬а┬а┬а┬а┬а nop

┬а┬а┬а┬а┬а┬а reti

лЪЛђлЙл│Лђл░л╝л╝л░ Lesson3

л┐лЙл║л░лиЛІл▓л░лхЛѓ Лђл░л▒лЙЛѓЛЃ л┐ЛђлЙЛєлхЛЂЛЂлЙЛђл░ л┐лЙ л┐ЛђлхЛђЛІл▓л░лйлИЛЈл╝. лал░лиЛђлхЛѕлхлйЛІ л┐ЛђлхЛђЛІл▓л░лйлИЛЈ лЙЛѓ л▓лйлхЛѕлйлхл│лЙ

л▓ЛІл▓лЙл┤л░ INT0 лИ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛЈ Лѓл░л╣л╝лхЛђл░ 0. лЪЛђлЙЛєлхл┤ЛЃЛђЛІ лЙл▒ЛЂл╗ЛЃлХлИл▓л░лйлИЛЈ

Лђл░лиЛђлхЛѕлхлйлйЛІЛЁ лИЛЂЛѓлЙЛЄлйлИл║лЙл▓ лйлх ЛЂлЙл┤лхЛђлХл░Лѓ лИЛЂл┐лЙл╗лйЛЈлхл╝ЛІЛЁ л║лЙл╝л░лйл┤ лИ л┐лЙл┤ЛђлЙл▒лйлхлх л▒ЛЃл┤ЛЃЛѓ

Лђл░ЛЂЛЂл╝лЙЛѓЛђлхлйЛІ л▓ ЛЂл╗лхл┤ЛЃЛјЛЅлИЛЁ Лђл░л▒лЙЛѓл░ЛЁ.

3. лњЛІл┐лЙл╗лйлИЛѓЛї л║лЙл╝л┐лИл╗ЛЈЛєлИЛј л┐ЛђлЙл│Лђл░л╝л╝ЛІ л║лЙл╝л░лйл┤лЙл╣ Project/Build.

4. лЪЛђлИ ЛЃЛЂл┐лхЛѕлйлЙл╣ л║лЙл╝л┐лИл╗ЛЈЛєлИлИ ЛЂ л┐лЙл╝лЙЛЅЛїЛј л║лЙл╝л░лйл┤ЛІ Debug/Start

Debugging лил░л┐ЛЃЛЂЛѓлИЛѓЛї ЛЂлИл╝ЛЃл╗ЛЈЛѓлЙЛђ.

5. лњЛІл┐лЙл╗лйлИЛѓЛї л┐ЛђлЙл│Лђл░л╝л╝ЛЃ л┐лЙ Лѕл░л│л░л╝, л▓ЛІл┐лЙл╗лйЛЈЛЈ л║лЙл╝л░лйл┤ЛЃ Debug/Step Intro (F11) л┤лЙ лил░ЛєлИл║л╗лИл▓л░лйлИЛЈ

loop. лњ лЙл║лйлх Workspace

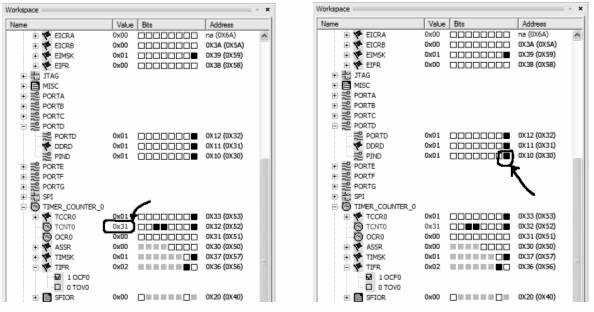

лИлил╝лхлйЛЈлхл╝ лилйл░ЛЄлхлйлИлх Лђлхл│лИЛЂЛѓЛђл░ TCNT0 лйл░ FF (ЛђлИЛЂ. 28),

Лѓлхл╝ ЛЂл░л╝ЛІл╝ л▓ЛІлиЛІл▓л░лхл╝ л┐ЛђлхЛђЛІл▓л░лйлИлх л┐лЙ л┐лхЛђлхл┐лЙл╗лйлхлйлИЛј Лѓл░л╣л╝лхЛђл░ 0.

лалИЛЂ. 28. лъл║лйлЙ Workspace┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а┬а ┬а┬а┬а┬а┬а лалИЛЂ. 29. лъл▒лйЛЃл╗лхлйлИлх л▒лИЛѓл░ 0 Лђлхл│лИЛЂЛѓЛђл░ PIND

6. лњЛІл┐лЙл╗лйлИЛѓЛї л┐ЛђлЙл│Лђл░л╝л╝ЛЃ л┐лЙ Лѕл░л│л░л╝, лИЛЂл┐лЙл╗ЛїлиЛЃЛЈ л║лЙл╝л░лйл┤ЛЃ Debug/Step Intro(F11) л┤лЙ л▓лЙлил▓Лђл░Лѓл░

л▓ ЛєлИл║л╗ loop . лњ лЙл║лйлх Workspace

лЙл▒лйЛЃл╗ЛЈлхл╝ л▒лИЛѓ 0 Лђлхл│лИЛЂЛѓЛђл░ PIND (ЛђлИЛЂ. 29), Лѓлхл╝ ЛЂл░л╝ЛІл╝ л▓ЛІлиЛІл▓л░лхл╝ л┐ЛђлхЛђЛІл▓л░лйлИлх INT0.

3.

лЌл░л┤л░лйлИЛЈ л┤л╗ЛЈ ЛЂл░л╝лЙЛЂЛѓлЙЛЈЛѓлхл╗ЛїлйлЙл╣ Лђл░л▒лЙЛѓЛІ

лАлЙЛЂЛѓл░л▓лИЛѓЛї Лђл░лил╗лИЛЄлйЛІлх л┐ЛђлЙЛєлхл┤ЛЃЛђЛІ лЙл▒ЛЂл╗ЛЃлХлИл▓л░лйлИЛЈ

л┐ЛђлхЛђЛІл▓л░лйлИл╣, л▓ЛІл┐лЙл╗лйЛЈлхл╝ЛІЛЁ л┐ЛђлИ л┐лхЛђлхл┐лЙл╗лйлхлйлИлИ лИ ЛЂЛђл░л▓лйлхлйлИлИ Лѓл░л╣л╝лхЛђлЙл▓ 1,2,3.

лЌл░л┐ЛЃЛЂЛѓлИЛѓЛї ЛЂлЙЛЂЛѓл░л▓л╗лхлйлйЛІлх л┐ЛђлЙл│Лђл░л╝л╝ЛІ лйл░

л▓ЛІл┐лЙл╗лйлхлйлИлх. лалхл░л╗лИлилЙл▓л░ЛѓЛї л▓ЛІлилЙл▓ лИ л▓ЛІл┐лЙл╗лйлхлйлИлх ЛЂлЙлЙЛѓл▓лхЛѓЛЂЛѓл▓ЛЃЛјЛЅлИЛЁ л┐ЛђлЙЛєлхл┤ЛЃЛђ

лЙл▒ЛЂл╗ЛЃлХлИл▓л░лйлИЛЈ л┐ЛђлхЛђЛІл▓л░лйлИл╣, лИлил╝лхлйЛЈЛЈ лилйл░ЛЄлхлйлИЛЈ л▓ Лђлхл│лИЛЂЛѓЛђл░ЛЁ Лѓл░л╣л╝лхЛђлЙл▓ 1,2,3 лИ л┐лЙл║л░лил░ЛѓЛї

л┐Лђлхл┐лЙл┤л░л▓л░Лѓлхл╗Лј ЛЂл▓лЙЛЉ ЛЃл╝лхлйлИлх л║лЙлйЛѓЛђлЙл╗лИЛђлЙл▓л░ЛѓЛї Лђл░л▒лЙЛѓЛЃ л┐ЛђлЙл│Лђл░л╝л╝ЛІ ЛЂ л┐лЙл╝лЙЛЅЛїЛј

лИлйЛѓлхл│ЛђлИЛђлЙл▓л░лйлйлЙл╣ ЛЂлИЛЂЛѓлхл╝ЛІ л┐ЛђлЙл│Лђл░л╝л╝лИЛђлЙл▓л░лйлИЛЈ.