–Ы–µ–Ї—Ж–Є—П.

–Ь–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Л –њ–Њ–і–≥—А—Г–њ–њ—Л PIC16F8X

–Я–Ы–Р–Э

–Ы–Х–Ъ–¶–Ш–Ш

1.

–Ю—Б–љ–Њ–≤–љ—Л–µ —Е–∞—А–∞–Ї—В–µ—А–Є—Б—В–Є–Ї–Є

2.

–Ю—Б–Њ–±–µ–љ–љ–Њ—Б—В–Є –∞—А—Е–Є—В–µ–Ї—В—Г—А—Л

3.

–°—Е–µ–Љ–∞ —В–∞–Ї—В–Є—А–Њ–≤–∞–љ–Є—П –Є —Ж–Є–Ї–ї –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –Ї–Њ–Љ–∞–љ–і—Л

4.

–Ю—А–≥–∞–љ–Є–Ј–∞—Ж–Є—П –њ–∞–Љ—П—В–Є –њ—А–Њ–≥—А–∞–Љ–Љ –Є —Б—В–µ–Ї–∞

5.

–Ю—А–≥–∞–љ–Є–Ј–∞—Ж–Є—П –њ–∞–Љ—П—В–Є –і–∞–љ–љ—Л—Е

6.

–†–µ–≥–Є—Б—В—А—Л —Б–њ–µ—Ж–Є–∞–ї—М–љ–Њ–≥–Њ –љ–∞–Ј–љ–∞—З–µ–љ–Є—П

7.

–°—З–µ—В—З–Є–Ї –Ї–Њ–Љ–∞–љ–і

8.

–Я—А—П–Љ–∞—П –Є –Ї–Њ—Б–≤–µ–љ–љ–∞—П –∞–і—А–µ—Б–∞—Ж–Є–Є

9.

–Я–Њ—А—В—Л –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞

10.

–Ь–Њ–і—Г–ї—М —В–∞–є–Љ–µ—А–∞ –Є —А–µ–≥–Є—Б—В—А —В–∞–є–Љ–µ—А–∞

11.

–Я–∞–Љ—П—В—М –і–∞–љ–љ—Л—Е –≤ –†–Я–Ч–£ (EEPROM)

12.

–Ю—А–≥–∞–љ–Є–Ј–∞—Ж–Є—П –њ—А–µ—А—Л–≤–∞–љ–Є–є

1. –Ю—Б–љ–Њ–≤–љ—Л–µ —Е–∞—А–∞–Ї—В–µ—А–Є—Б—В–Є–Ї–Є

–Ь–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Л –њ–Њ–і–≥—А—Г–њ–њ—Л PIC16F8X

–Њ—В–љ–Њ—Б—П—В—Б—П –Ї —Б–µ–Љ–µ–є—Б—В–≤—Г 8-—А–∞–Ј—А—П–і–љ—Л—Е –Ъ–Ь–Ю–Я –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–Њ–≤ –≥—А—Г–њ–њ—Л PIC16CXXX, –і–ї—П

–Ї–Њ—В–Њ—А—Л—Е —Е–∞—А–∞–Ї—В–µ—А–љ—Л –љ–Є–Ј–Ї–∞—П —Б—В–Њ–Є–Љ–Њ—Б—В—М, –њ–Њ–ї–љ–Њ—Б—В—М—О —Б—В–∞—В–Є—З–µ—Б–Ї–∞—П –Ъ–Ь–Ю–Я-—В–µ—Е–љ–Њ–ї–Њ–≥–Є—П –Є

–≤—Л—Б–Њ–Ї–∞—П –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї—М–љ–Њ—Б—В—М.

–Т —Б–Њ—Б—В–∞–≤ –њ–Њ–і–≥—А—Г–њ–њ—Л –≤—Е–Њ–і—П—В –Ь–Ъ PIC16F83,

PIC16CR83, PIC16F84 –Є PIC16CR84. –Ю—Б–љ–Њ–≤–љ—Л–µ —Е–∞—А–∞–Ї—В–µ—А–Є—Б—В–Є–Ї–Є –Ь–Ъ –њ–Њ–і–≥—А—Г–њ–њ—Л PIC16F8X

–њ—А–Є–≤–µ–і–µ–љ—Л –≤ —В–∞–±–ї. 1.

–Т—Б–µ –Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Л –њ–Њ–і–≥—А—Г–њ–њ—Л PIC16F8X

–Є—Б–њ–Њ–ї—М–Ј—Г—О—В –≥–∞—А–≤–∞—А–і—Б–Ї—Г—О –∞—А—Е–Є—В–µ–Ї—В—Г—А—Г —Б RISC-–њ—А–Њ—Ж–µ—Б—Б–Њ—А–Њ–Љ, –Њ–±–ї–∞–і–∞—О—Й—Г—О —Б–ї–µ–і—Г—О—Й–Є–Љ–Є

–Њ—Б–љ–Њ–≤–љ—Л–Љ–Є –Њ—Б–Њ–±–µ–љ–љ–Њ—Б—В—П–Љ–Є:

¬Ј

–Є—Б–њ–Њ–ї—М–Ј—Г—О—В—Б—П —В–Њ–ї—М–Ї–Њ 35 –њ—А–Њ—Б—В—Л—Е –Ї–Њ–Љ–∞–љ–і;

¬Ј

–≤—Б–µ –Ї–Њ–Љ–∞–љ–і—Л –≤—Л–њ–Њ–ї–љ—П—О—В—Б—П –Ј–∞ –Њ–і–Є–љ —Ж–Є–Ї–ї (400 –љ—Б –њ—А–Є

—З–∞—Б—В–Њ—В–µ 10 –Ь–У—Ж), –Ї—А–Њ–Љ–µ –Ї–Њ–Љ–∞–љ–і –њ–µ—А–µ—Е–Њ–і–∞, –Ї–Њ—В–Њ—А—Л–µ —В—А–µ–±—Г—О—В 2 —Ж–Є–Ї–ї–∞;

¬Ј

—А–∞–±–Њ—З–∞—П —З–∞—Б—В–Њ—В–∞ 0 –У—Ж ... 10 –Ь–У—Ж;

¬Ј

—А–∞–Ј–і–µ–ї—М–љ—Л–µ —И–Є–љ—Л –і–∞–љ–љ—Л—Е (8 –±–Є—В) –Є –Ї–Њ–Љ–∞–љ–і (14

–±–Є—В);

¬Ј

512 —Е 14 –Є–ї–Є 1024 —Е 14 –њ–∞–Љ—П—В—М –њ—А–Њ–≥—А–∞–Љ–Љ,

–≤—Л–њ–Њ–ї–љ–µ–љ–љ–∞—П –љ–∞ –Я–Ч–£ –Є–ї–Є —Н–ї–µ–Ї—В—А–Є—З–µ—Б–Ї–Є –њ–µ—А–µ–њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ–Њ–є Flash- –њ–∞–Љ—П—В–Є;

¬Ј

15 –≤–Њ—Б—М–Љ–Є—А–∞–Ј—А—П–і–љ—Л—Е —А–µ–≥–Є—Б—В—А–Њ–≤

—Б–њ–µ—Ж–Є–∞–ї—М–љ—Л—Е —Д—Г–љ–Ї—Ж–Є–є (SFR);

¬Ј

–≤–Њ—Б—М–Љ–Є—Г—А–Њ–≤–љ–µ–≤—Л–є –∞–њ–њ–∞—А–∞—В–љ—Л–є —Б—В–µ–Ї;

¬Ј

–њ—А—П–Љ–∞—П, –Ї–Њ—Б–≤–µ–љ–љ–∞—П –Є –Њ—В–љ–Њ—Б–Є—В–µ–ї—М–љ–∞—П –∞–і—А–µ—Б–∞—Ж–Є—П –і–∞–љ–љ—Л—Е –Є –Ї–Њ–Љ–∞–љ–і;

¬Ј

36 –Є–ї–Є 68 –≤–Њ—Б—М–Љ–Є—А–∞–Ј—А—П–і–љ—Л—Е —А–µ–≥–Є—Б—В—А–Њ–≤

–Њ–±—Й–µ–≥–Њ –љ–∞–Ј–љ–∞—З–µ–љ–Є—П (GPR) –Є–ї–Є –Ю–Ч–£;

¬Ј

—З–µ—В—Л—А–µ –Є—Б—В–Њ—З–љ–Є–Ї–∞ –њ—А–µ—А—Л–≤–∞–љ–Є—П:

o

–≤–љ–µ—И–љ–Є–є –≤—Е–Њ–і RB0/INT;

o

–њ–µ—А–µ–њ–Њ–ї–љ–µ–љ–Є–µ —В–∞–є–Љ–µ—А–∞

TMR0;

o

–Є–Ј–Љ–µ–љ–µ–љ–Є–µ —Б–Є–≥–љ–∞–ї–Њ–≤ –љ–∞ –ї–Є–љ–Є—П—Е –њ–Њ—А—В–∞ B;

o

–Ј–∞–≤–µ—А—И–µ–љ–Є–µ –Ј–∞–њ–Є—Б–Є –і–∞–љ–љ—Л—Е –≤ –њ–∞–Љ—П—В—М EEPROM;

¬Ј

64 x 8 —Н–ї–µ–Ї—В—А–Є—З–µ—Б–Ї–Є –њ–µ—А–µ–њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ–∞—П EEPROM –њ–∞–Љ—П—В—М

–і–∞–љ–љ—Л—Е —Б –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В—М—О –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П 1000000 —Ж–Є–Ї–ї–Њ–≤ —Б—В–Є—А–∞–љ–Є—П/–Ј–∞–њ–Є—Б–Є;

¬Ј

—Б–Њ—Е—А–∞–љ–µ–љ–Є–µ –і–∞–љ–љ—Л—Е –≤ EEPROM –≤

—В–µ—З–µ–љ–Є–µ –Ї–∞–Ї –Љ–Є–љ–Є–Љ—Г–Љ 40 –ї–µ—В.

–Ь–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Л –њ–Њ–і–≥—А—Г–њ–њ—Л PIC16F8X

–Њ–±–ї–∞–і–∞—О—В —А–∞–Ј–≤–Є—В—Л–Љ–Є –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В—П–Љ–Є –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞:

¬Ј

13 –ї–Є–љ–Є–є –≤–≤–Њ–і–∞-–≤—Л–≤–Њ–і–∞ —Б –Є–љ–і–Є–≤–Є–і—Г–∞–ї—М–љ–Њ–є

—Г—Б—В–∞–љ–Њ–≤–Ї–Њ–є –љ–∞–њ—А–∞–≤–ї–µ–љ–Є—П –Њ–±–Љ–µ–љ–∞;

¬Ј

–≤—Л—Б–Њ–Ї–Є–є –≤—В–µ–Ї–∞—О—Й–Є–є/–≤—Л—В–µ–Ї–∞—О—Й–Є–є —В–Њ–Ї, –і–Њ—Б—В–∞—В–Њ—З–љ—Л–є

–і–ї—П —Г–њ—А–∞–≤–ї–µ–љ–Є—П —Б–≤–µ—В–Њ–і–Є–Њ–і–∞–Љ–Є:

¬Ј

–Љ–∞–Ї—Б–Є–Љ–∞–ї—М–љ—Л–є –≤—В–µ–Ї–∞—О—Й–Є–є —В–Њ–Ї вАУ 25 –Љ–Р;

¬Ј

–Љ–∞–Ї—Б–Є–Љ–∞–ї—М–љ—Л–є –≤—Л—В–µ–Ї–∞—О—Й–Є–є —В–Њ–Ї вАУ 20 –Љ–Р;

¬Ј

8-–±–Є—В–љ—Л–є —В–∞–є–Љ–µ—А/—Б—З–µ—В—З–Є–Ї

TMR0 —Б

8-–±–Є—В–љ—Л–Љ –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ—Л–Љ –њ—А–µ–і–≤–∞—А–Є—В–µ–ї—М–љ—Л–Љ –і–µ–ї–Є—В–µ–ї–µ–Љ.

–°–њ–µ—Ж–Є–∞–ї–Є–Ј–Є—А–Њ–≤–∞–љ–љ—Л–µ

–Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–љ—Л–µ —Д—Г–љ–Ї—Ж–Є–Є –≤–Ї–ї—О—З–∞—О—В —Б–ї–µ–і—Г—О—Й–Є–µ –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В–Є:

¬Ј

–∞–≤—В–Њ–Љ–∞—В–Є—З–µ—Б–Ї–Є–є —Б–±—А–Њ—Б –њ—А–Є –≤–Ї–ї—О—З–µ–љ–Є–Є

(Power-on-Reset);

¬Ј

—В–∞–є–Љ–µ—А

–≤–Ї–ї—О—З–µ–љ–Є—П –њ—А–Є —Б–±—А–Њ—Б–µ (Power-up Timer);

¬Ј

—В–∞–є–Љ–µ—А

–Ј–∞–њ—Г—Б–Ї–∞ –≥–µ–љ–µ—А–∞—В–Њ—А–∞ (Oscillator Start-up Timer);

¬Ј

—Б—В–Њ—А–Њ–ґ–µ–≤–Њ–є (Watchdog) —В–∞–є–Љ–µ—А

WDT —Б —Б–Њ–±—Б—В–≤–µ–љ–љ—Л–Љ –≤—Б—В—А–Њ–µ–љ–љ—Л–Љ –≥–µ–љ–µ—А–∞—В–Њ—А–Њ–Љ,

–Њ–±–µ—Б–њ–µ—З–Є–≤–∞—О—Й–Є–Љ –њ–Њ–≤—Л—И–µ–љ–љ—Г—О –љ–∞–і–µ–ґ–љ–Њ—Б—В—М;

¬Ј

EEPROM –±–Є—В —Б–µ–Ї—А–µ—В–љ–Њ—Б—В–Є –і–ї—П

–Ј–∞—Й–Є—В—Л –Ї–Њ–і–∞;

¬Ј

—Н–Ї–Њ–љ–Њ–Љ–Є—З–љ—Л–є —А–µ–ґ–Є–Љ SLEEP;

¬Ј

–≤—Л–±–Є—А–∞–µ–Љ—Л–µ –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї–µ–Љ –±–Є—В—Л –і–ї—П —Г—Б—В–∞–љ–Њ–≤–Ї–Є

—А–µ–ґ–Є–Љ–∞ –≤–Њ–Ј–±—Г–ґ–і–µ–љ–Є—П –≤—Б—В—А–Њ–µ–љ–љ–Њ–≥–Њ –≥–µ–љ–µ—А–∞—В–Њ—А–∞;

¬Ј

–њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ–µ –≤—Б—В—А–Њ–µ–љ–љ–Њ–µ —Г—Б—В—А–Њ–є—Б—В–≤–Њ

–њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П Flash/EEPROM –њ–∞–Љ—П—В–Є

–њ—А–Њ–≥—А–∞–Љ–Љ –Є –і–∞–љ–љ—Л—Е —Б –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ–Љ —В–Њ–ї—М–Ї–Њ –і–≤—Г—Е –≤—Л–≤–Њ–і–Њ–≤.

–Ъ–Ь–Ю–Я —В–µ—Е–љ–Њ–ї–Њ–≥–Є—П –Њ–±–µ—Б–њ–µ—З–Є–≤–∞–µ—В –Ь–Ъ –њ–Њ–і–≥—А—Г–њ–њ—Л

PIC16F8X –і–Њ–њ–Њ–ї–љ–Є—В–µ–ї—М–љ—Л–µ –њ—А–µ–Є–Љ—Г—Й–µ—Б—В–≤–∞:

¬Ј

—Б—В–∞—В–Є—З–µ—Б–Ї–Є–є –њ—А–Є–љ—Ж–Є–њ —А–∞–±–Њ—В—Л;

¬Ј

—И–Є—А–Њ–Ї–Є–є –і–Є–∞–њ–∞–Ј–Њ–љ –љ–∞–њ—А—П–ґ–µ–љ–Є–є –њ–Є—В–∞–љ–Є—П: 2,0 ... 6,0

–Т;

¬Ј

–љ–Є–Ј–Ї–Њ–µ —Н–љ–µ—А–≥–Њ–њ–Њ—В—А–µ–±–ї–µ–љ–Є–µ:

¬Ј

–Љ–µ–љ–µ–µ 2 –Љ–Р –њ—А–Є 5–Т –Є 4–Ь–У—Ж;

¬Ј

–њ–Њ—А—П–і–Ї–∞ 15 –Љ–Ї–Р –њ—А–Є 2–Т –Є 32–Ъ–У—Ж;

¬Ј

–Љ–µ–љ–µ–µ 1 –Љ–Ї–Р –і–ї—П SLEEP-—А–µ–ґ–Є–Љ–∞

–њ—А–Є 2–Т.

–Ь–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Л –њ–Њ–і–≥—А—Г–њ–њ—Л PIC16F8X

—А–∞–Ј–ї–Є—З–∞—О—В—Б—П –Љ–µ–ґ–і—Г —Б–Њ–±–Њ–є —В–Њ–ї—М–Ї–Њ –Њ–±—К–µ–Љ–Њ–Љ –Ю–Ч–£ –і–∞–љ–љ—Л—Е, –∞ —В–∞–Ї–ґ–µ –Њ–±—К–µ–Љ–Њ–Љ –Є —В–Є–њ–Њ–Љ

–њ–∞–Љ—П—В–Є –њ—А–Њ–≥—А–∞–Љ–Љ. –Э–∞–ї–Є—З–Є–µ –≤ —Б–Њ—Б—В–∞–≤–µ –њ–Њ–і–≥—А—Г–њ–њ—Л –Ь–Ъ —Б Flash-–њ–∞–Љ—П—В—М—О –њ—А–Њ–≥—А–∞–Љ–Љ

–Њ–±–ї–µ–≥—З–∞–µ—В —Б–Њ–Ј–і–∞–љ–Є–µ –Є –Њ—В–ї–∞–і–Ї—Г –њ—А–Њ—В–Њ—В–Є–њ–Њ–≤ –њ—А–Њ–Љ—Л—И–ї–µ–љ–љ—Л—Е –Њ–±—А–∞–Ј—Ж–Њ–≤ –Є–Ј–і–µ–ї–Є–є.

2. –Ю—Б–Њ–±–µ–љ–љ–Њ—Б—В–Є –∞—А—Е–Є—В–µ–Ї—В—Г—А—Л

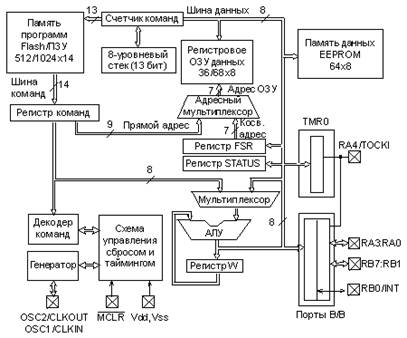

–£–њ—А–Њ—Й–µ–љ–љ–∞—П —Б—В—А—Г–Ї—В—Г—А–љ–∞—П —Б—Е–µ–Љ–∞ –Ь–Ъ –њ–Њ–і–≥—А—Г–њ–њ—Л

PIC16F8X –њ—А–Є–≤–µ–і–µ–љ–∞ –љ–∞ —А–Є—Б. 1.

–†–Є—Б. 1. –°—В—А—Г–Ї—В—Г—А–љ–∞—П —Б—Е–µ–Љ–∞

–Ь–Ъ –њ–Њ–і–≥—А—Г–њ–њ—Л PIC16F8X

–Р—А—Е–Є—В–µ–Ї—В—Г—А–∞ –Њ—Б–љ–Њ–≤–∞–љ–∞ –љ–∞ –Ї–Њ–љ—Ж–µ–њ—Ж–Є–Є

—А–∞–Ј–і–µ–ї—М–љ—Л—Е —И–Є–љ –Є –Њ–±–ї–∞—Б—В–µ–є –њ–∞–Љ—П—В–Є –і–ї—П –і–∞–љ–љ—Л—Е –Є –і–ї—П –Ї–Њ–Љ–∞–љ–і (–≥–∞—А–≤–∞—А–і—Б–Ї–∞—П

–∞—А—Е–Є—В–µ–Ї—В—Г—А–∞). –®–Є–љ–∞ –і–∞–љ–љ—Л—Е –Є –њ–∞–Љ—П—В—М –і–∞–љ–љ—Л—Е (–Ю–Ч–£) вАУ –Є–Љ–µ—О—В —И–Є—А–Є–љ—Г 8 –±–Є—В, –∞

–њ—А–Њ–≥—А–∞–Љ–Љ–љ–∞—П —И–Є–љ–∞ –Є –њ—А–Њ–≥—А–∞–Љ–Љ–љ–∞—П –њ–∞–Љ—П—В—М (–Я–Ч–£) –Є–Љ–µ—О—В —И–Є—А–Є–љ—Г 14 –±–Є—В. –Ґ–∞–Ї–∞—П

–Ї–Њ–љ—Ж–µ–њ—Ж–Є—П –Њ–±–µ—Б–њ–µ—З–Є–≤–∞–µ—В –њ—А–Њ—Б—В—Г—О, –љ–Њ –Љ–Њ—Й–љ—Г—О —Б–Є—Б—В–µ–Љ—Г –Ї–Њ–Љ–∞–љ–і, —А–∞–Ј—А–∞–±–Њ—В–∞–љ–љ—Г—О —В–∞–Ї,

—З—В–Њ –±–Є—В–Њ–≤—Л–µ, –±–∞–є—В–Њ–≤—Л–µ –Є —А–µ–≥–Є—Б—В—А–Њ–≤—Л–µ –Њ–њ–µ—А–∞—Ж–Є–Є —А–∞–±–Њ—В–∞—О—В —Б –≤—Л—Б–Њ–Ї–Њ–є —Б–Ї–Њ—А–Њ—Б—В—М—О –Є —Б

–њ–µ—А–µ–Ї—А—Л—В–Є–µ–Љ –њ–Њ –≤—А–µ–Љ–µ–љ–Є –≤—Л–±–Њ—А–Њ–Ї –Ї–Њ–Љ–∞–љ–і –Є —Ж–Є–Ї–ї–Њ–≤ –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П. 14-–±–Є—В–Њ–≤–∞—П —И–Є—А–Є–љ–∞ –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–є

–њ–∞–Љ—П—В–Є –Њ–±–µ—Б–њ–µ—З–Є–≤–∞–µ—В –≤—Л–±–Њ—А–Ї—Г 14-–±–Є—В–Њ–≤–Њ–є –Ї–Њ–Љ–∞–љ–і—Л –≤ –Њ–і–Є–љ —Ж–Є–Ї–ї. –Ф–≤—Г—Е—Б—В—Г–њ–µ–љ—З–∞—В—Л–є

–Ї–Њ–љ–≤–µ–є–µ—А –Њ–±–µ—Б–њ–µ—З–Є–≤–∞–µ—В –Њ–і–љ–Њ–≤—А–µ–Љ–µ–љ–љ—Г—О –≤—Л–±–Њ—А–Ї—Г –Є –Є—Б–њ–Њ–ї–љ–µ–љ–Є–µ –Ї–Њ–Љ–∞–љ–і—Л. –Т—Б–µ –Ї–Њ–Љ–∞–љ–і—Л

–≤—Л–њ–Њ–ї–љ—П—О—В—Б—П –Ј–∞ –Њ–і–Є–љ —Ж–Є–Ї–ї, –Є—Б–Ї–ї—О—З–∞—П –Ї–Њ–Љ–∞–љ–і—Л –њ–µ—А–µ—Е–Њ–і–Њ–≤.

–Ь–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Л PIC16F83 –Є PIC16CR83

–∞–і—А–µ—Б—Г—О—В 512—Е14 –њ–∞–Љ—П—В–Є –њ—А–Њ–≥—А–∞–Љ–Љ, –∞ PIC16F84 –Є PIC16CR84 вАУ 1–Ъ—Е14 –њ–∞–Љ—П—В–Є

–њ—А–Њ–≥—А–∞–Љ–Љ. –Т—Б—П –њ–∞–Љ—П—В—М –њ—А–Њ–≥—А–∞–Љ–Љ —П–≤–ї—П–µ—В—Б—П –≤–љ—Г—В—А–µ–љ–љ–µ–є.

–Ь–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А –Љ–Њ–ґ–µ—В –њ—А—П–Љ–Њ –Є–ї–Є –Ї–Њ—Б–≤–µ–љ–љ–Њ

–Њ–±—А–∞—Й–∞—В—М—Б—П –Ї —А–µ–≥–Є—Б—В—А–∞–Љ –Є–ї–Є –њ–∞–Љ—П—В–Є –і–∞–љ–љ—Л—Е. –Т—Б–µ —А–µ–≥–Є—Б—В—А—Л —Б–њ–µ—Ж–Є–∞–ї—М–љ—Л—Е —Д—Г–љ–Ї—Ж–Є–є, –≤–Ї–ї—О—З–∞—П —Б—З–µ—В—З–Є–Ї –Ї–Њ–Љ–∞–љ–і,

–Њ—В–Њ–±—А–∞–ґ–∞—О—В—Б—П –љ–∞ –њ–∞–Љ—П—В—М –і–∞–љ–љ—Л—Е. –Ю—А—В–Њ–≥–Њ–љ–∞–ї—М–љ–∞—П (—Б–Є–Љ–Љ–µ—В—А–Є—З–љ–∞—П) —Б–Є—Б—В–µ–Љ–∞ –Ї–Њ–Љ–∞–љ–і

–њ–Њ–Ј–≤–Њ–ї—П–µ—В –≤—Л–њ–Њ–ї–љ—П—В—М –ї—О–±—Г—О –Ї–Њ–Љ–∞–љ–і—Г –љ–∞–і –ї—О–±—Л–Љ —А–µ–≥–Є—Б—В—А–Њ–Љ

—Б –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ–Љ –њ—А–Њ–Є–Ј–≤–Њ–ї—М–љ–Њ–≥–Њ –Љ–µ—В–Њ–і–∞ –∞–і—А–µ—Б–∞—Ж–Є–Є.

–Ю—А—В–Њ–≥–Њ–љ–∞–ї—М–љ–∞—П –∞—А—Е–Є—В–µ–Ї—В—Г—А–∞ –Є –Њ—В—Б—Г—В—Б—В–≤–Є–µ —Б–њ–µ—Ж–Є–∞–ї—М–љ—Л—Е –Є—Б–Ї–ї—О—З–µ–љ–Є–є –і–µ–ї–∞–µ—В

–њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є–µ –Ь–Ъ –≥—А—Г–њ–њ—Л PIC16F8X –њ—А–Њ—Б—В—Л–Љ –Є —Н—Д—Д–µ–Ї—В–Є–≤–љ—Л–Љ.

–Э–∞–Ј–љ–∞—З–µ–љ–Є–µ –≤—Л–≤–Њ–і–Њ–≤ –Ь–Ъ –њ–Њ–і–≥—А—Г–њ–њ—Л PIC16F8X

–њ—А–Є–≤–µ–і–µ–љ–Њ –≤ —В–∞–±–ї. 2.

|

–Ґ–∞–±–ї–Є—Ж–∞ 2. –Э–∞–Ј–љ–∞—З–µ–љ–Є–µ

–≤—Л–≤–Њ–і–Њ–≤ –Ь–Ъ –њ–Њ–і–≥—А—Г–њ–њ—Л PIC16F8X |

|||||

|

–Ю–±–Њ–Ј–љ–∞—З–µ–љ–Є–µ |

–Ґ–Є–њ |

–С—Г—Д–µ—А |

–Ю–њ–Є—Б–∞–љ–Є–µ |

||

|

OSC1/CLKIN |

I |

–Ґ–®/–Ъ–Ь–Ю–Я1) |

–Т—Е–Њ–і –Ї—А–Є—Б—В–∞–ї–ї–∞ –≥–µ–љ–µ—А–∞—В–Њ—А–∞, RC-—Ж–µ–њ–Њ—З–Ї–Є –Є–ї–Є –≤—Е–Њ–і

–≤–љ–µ—И–љ–µ–≥–Њ —В–∞–Ї—В–Њ–≤–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ |

||

|

OSC2/CLKOUT |

O |

- |

–Т—Л—Е–Њ–і –Ї—А–Є—Б—В–∞–ї–ї–∞ –≥–µ–љ–µ—А–∞—В–Њ—А–∞. –Т RC-—А–µ–ґ–Є–Љ–µ вАУ

–≤—Л—Е–Њ–і 1/4 —З–∞—Б—В–Њ—В—Л OSC1 |

||

|

/MCLR |

I/P |

–Ґ–® |

–°–Є–≥–љ–∞–ї —Б–±—А–Њ—Б–∞/–≤—Е–Њ–і –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г—О—Й–µ–≥–Њ

–љ–∞–њ—А—П–ґ–µ–љ–Є—П. –°–±—А–Њ—Б –љ–Є–Ј–Ї–Є–Љ —Г—А–Њ–≤–љ–µ–Љ. |

||

|

RA0 |

I/O |

–Ґ–Ґ–Ы |

PORTA вАУ –і–≤—Г–љ–∞–њ—А–∞–≤–ї–µ–љ–љ—Л–є –њ–Њ—А—В –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞ RA4/T0CKI –Љ–Њ–ґ–µ—В –±—Л—В—М –≤—Л–±—А–∞–љ –Ї–∞–Ї

—В–∞–Ї—В–Њ–≤—Л–є –≤—Е–Њ–і —В–∞–є–Љ–µ—А–∞/—Б—З–µ—В—З–Є–Ї–∞ TMR0. –Т—Л—Е–Њ–і —Б –Њ—В–Ї—А—Л—В—Л–Љ —Б—В–Њ–Ї–Њ–Љ. |

||

|

RA1 |

I/O |

–Ґ–Ґ–Ы |

|||

|

RA2 |

I/O |

–Ґ–Ґ–Ы |

|||

|

RA3 |

I/O |

–Ґ–Ґ–Ы |

|||

|

RA4 |

I/O |

–Ґ–® |

|||

|

/T0CKI |

|

|

|||

|

RB0/INT |

I/O |

–Ґ–Ґ–Ы/–Ґ–®2) |

PORTB вАУ –і–≤—Г–љ–∞–њ—А–∞–≤–ї–µ–љ–љ—Л–є –њ–Њ—А—В –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞. –Ь–Њ–ґ–µ—В –±—Л—В—М –Ј–∞–њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ –≤ —А–µ–ґ–Є–Љ–µ

–≤–љ—Г—В—А–µ–љ–љ–Є—Е –∞–Ї—В–Є–≤–љ—Л—Е –љ–∞–≥—А—Г–Ј–Њ–Ї –љ–∞ –ї–Є–љ–Є—О –њ–Є—В–∞–љ–Є—П –њ–Њ –≤—Б–µ–Љ –≤—Л–≤–Њ–і–∞–Љ. –Т—Л–≤–Њ–і RB0/INT –Љ–Њ–ґ–µ—В –±—Л—В—М –≤—Л–±—А–∞–љ –Ї–∞–Ї

–≤–љ–µ—И–љ–Є–є –≤—Е–Њ–і –њ—А–µ—А—Л–≤–∞–љ–Є—П. –Т—Л–≤–Њ–і—Л RB4...RB7 –Љ–Њ–≥—Г—В –±—Л—В—М –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ

–љ–∞—Б—В—А–Њ–µ–љ—Л –Ї–∞–Ї –≤—Е–Њ–і—Л –њ—А–µ—А—Л–≤–∞–љ–Є—П –њ–Њ –Є–Ј–Љ–µ–љ–µ–љ–Є—О

—Б–Њ—Б—В–Њ—П–љ–Є—П –љ–∞ –ї—О–±–Њ–Љ –Є–Ј –≤—Е–Њ–і–Њ–≤. –Я—А–Є –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є–Є –Ь–Ъ RB6 –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –Ї–∞–Ї

—В–∞–Ї—В–Њ–≤—Л–є, –∞ RB7 –Ї–∞–Ї –≤—Е–Њ–і/–≤—Л—Е–Њ–і –і–∞–љ–љ—Л—Е. |

||

|

RB1 |

I/O |

–Ґ–Ґ–Ы |

|||

|

RB2 |

I/O |

–Ґ–Ґ–Ы |

|||

|

RB3 |

I/O |

–Ґ–Ґ–Ы |

|||

|

RB4 |

I/O |

–Ґ–Ґ–Ы |

|||

|

RB5 |

I/O |

–Ґ–Ґ–Ы |

|||

|

RB6 |

I/O |

–Ґ–Ґ–Ы/–Ґ–®3) |

|||

|

RB7 |

I/O |

–Ґ–Ґ–Ы/–Ґ–®4) |

|||

|

|

|||||

|

|

|

|

|

||

|

Vdd |

P |

- |

–Я–Њ–ї–Њ–ґ–Є—В–µ–ї—М–љ–Њ–µ –љ–∞–њ—А—П–ґ–µ–љ–Є–µ –њ–Є—В–∞–љ–Є—П |

||

|

Vss |

P |

- |

–Ю–±—Й–Є–є –њ—А–Њ–≤–Њ–і (–Ј–µ–Љ–ї—П) |

||

|

–Т

—В–∞–±–ї–Є—Ж–µ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ—Л —Б–ї–µ–і—Г—О—Й–Є–µ –Њ–±–Њ–Ј–љ–∞—З–µ–љ–Є—П: I вАФ –≤—Е–Њ–і; O вАФ –≤—Л—Е–Њ–і; I/O вАФ

–≤—Е–Њ–і/–≤—Л—Е–Њ–і; P вАФ –њ–Є—В–∞–љ–Є–µ; вАУ вАФ –љ–µ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П; –Ґ–Ґ–Ы вАФ –Ґ–Ґ–Ы –≤—Е–Њ–і; –Ґ–® вАФ –≤—Е–Њ–і

—В—А–Є–≥–≥–µ—А–∞ –®–Љ–Є—В—В–∞. |

|||||

–Ь–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А —Б–Њ–і–µ—А–ґ–Є—В 8-—А–∞–Ј—А—П–і–љ–Њ–µ –Р–Ы–£ –Є

—А–∞–±–Њ—З–Є–є —А–µ–≥–Є—Б—В—А W. –Р–Ы–£ —П–≤–ї—П–µ—В—Б—П –∞—А–Є—Д–Љ–µ—В–Є—З–µ—Б–Ї–Є–Љ –Љ–Њ–і—Г–ї–µ–Љ –Њ–±—Й–µ–≥–Њ –љ–∞–Ј–љ–∞—З–µ–љ–Є—П –Є

–≤—Л–њ–Њ–ї–љ—П–µ—В –∞—А–Є—Д–Љ–µ—В–Є—З–µ—Б–Ї–Є–µ –Є –ї–Њ–≥–Є—З–µ—Б–Ї–Є–µ —Д—Г–љ–Ї—Ж–Є–Є –љ–∞–і —Б–Њ–і–µ—А–ґ–Є–Љ—Л–Љ —А–∞–±–Њ—З–µ–≥–Њ —А–µ–≥–Є—Б—В—А–∞ –Є –ї—О–±–Њ–≥–Њ –Є–Ј —А–µ–≥–Є—Б—В—А–Њ–≤

–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞. –Р–Ы–£ –Љ–Њ–ґ–µ—В –≤—Л–њ–Њ–ї–љ—П—В—М –Њ–њ–µ—А–∞—Ж–Є–Є —Б–ї–Њ–ґ–µ–љ–Є—П, –≤—Л—З–Є—В–∞–љ–Є—П, —Б–і–≤–Є–≥–∞ –Є

–ї–Њ–≥–Є—З–µ—Б–Ї–Є–µ –Њ–њ–µ—А–∞—Ж–Є–Є. –Х—Б–ї–Є –љ–µ —Г–Ї–∞–Ј–∞–љ–Њ –Є–љ–Њ–µ, —В–Њ –∞—А–Є—Д–Љ–µ—В–Є—З–µ—Б–Ї–Є–µ –Њ–њ–µ—А–∞—Ж–Є–Є

–≤—Л–њ–Њ–ї–љ—П—О—В—Б—П –≤ –і–Њ–њ–Њ–ї–љ–Є—В–µ–ї—М–љ–Њ–Љ –і–≤–Њ–Є—З–љ–Њ–Љ –Ї–Њ–і–µ.

–Т –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В —А–µ–Ј—Г–ї—М—В–∞—В–∞ –Њ–њ–µ—А–∞—Ж–Є–Є, –Р–Ы–£

–Љ–Њ–ґ–µ—В –Є–Ј–Љ–µ–љ—П—В—М –Ј–љ–∞—З–µ–љ–Є—П –±–Є—В —А–µ–≥–Є—Б—В—А–∞ STATUS: C (Carry), DC (Digit carry) –Є Z (Zero).

3. –°—Е–µ–Љ–∞ —В–∞–Ї—В–Є—А–Њ–≤–∞–љ–Є—П –Є —Ж–Є–Ї–ї –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –Ї–Њ–Љ–∞–љ–і—Л

–Т—Е–Њ–і–љ–∞—П —В–∞–Ї—В–Њ–≤–∞—П —З–∞—Б—В–Њ—В–∞, –њ–Њ—Б—В—Г–њ–∞—О—Й–∞—П —Б

–≤—Л–≤–Њ–і–∞ OSC1/CLKIN, –і–µ–ї–Є—В—Б—П

–≤–љ—Г—В—А–Є –љ–∞ —З–µ—В—Л—А–µ, –Є –Є–Ј –љ–µ–µ —Д–Њ—А–Љ–Є—А—Г—О—В—Б—П —З–µ—В—Л—А–µ —Ж–Є–Ї–ї–Є—З–µ—Б–Ї–Є–µ –љ–µ –њ–µ—А–µ–Ї—А—Л–≤–∞—О—Й–Є–µ—Б—П

—В–∞–Ї—В–Њ–≤—Л–µ –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ—Б—В–Є Q1, Q2, Q3 –Є Q4. –°—З–µ—В—З–Є–Ї –Ї–Њ–Љ–∞–љ–і —Г–≤–µ–ї–Є—З–Є–≤–∞–µ—В—Б—П

–≤ —В–∞–Ї—В–µ Q1, –Ї–Њ–Љ–∞–љ–і–∞ —Б—З–Є—В—Л–≤–∞–µ—В—Б—П –Є–Ј

–њ–∞–Љ—П—В–Є –њ—А–Њ–≥—А–∞–Љ–Љ—Л –Є –Ј–∞—Й–µ–ї–Ї–Є–≤–∞–µ—В—Б—П –≤ —А–µ–≥–Є—Б—В—А–µ –Ї–Њ–Љ–∞–љ–і

–≤ —В–∞–Ї—В–µ Q4. –Ъ–Њ–Љ–∞–љ–і–∞ –і–µ–Ї–Њ–і–Є—А—Г–µ—В—Б—П –Є

–≤—Л–њ–Њ–ї–љ—П–µ—В—Б—П –≤ —В–µ—З–µ–љ–Є–µ –њ–Њ—Б–ї–µ–і—Г—О—Й–µ–≥–Њ —Ж–Є–Ї–ї–∞ –≤ —В–∞–Ї—В–∞—Е Q1...Q4. –°—Е–µ–Љ–∞ —В–∞–Ї—В–Є—А–Њ–≤–∞–љ–Є—П –Є –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –Ї–Њ–Љ–∞–љ–і—Л –Є–Ј–Њ–±—А–∞–ґ–µ–љ–∞ –љ–∞ —А–Є—Б.

2.

–¶–Є–Ї–ї

–≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –Ї–Њ–Љ–∞–љ–і—Л —Б–Њ—Б—В–Њ–Є—В –Є–Ј —З–µ—В—Л—А–µ—Е —В–∞–Ї—В–Њ–≤: Q1...Q4. –Т—Л–±–Њ—А–Ї–∞ –Ї–Њ–Љ–∞–љ–і—Л –Є –µ–µ –≤—Л–њ–Њ–ї–љ–µ–љ–Є–µ —Б–Њ–≤–Љ–µ—Й–µ–љ—Л –њ–Њ –≤—А–µ–Љ–µ–љ–Є —В–∞–Ї–Є–Љ

–Њ–±—А–∞–Ј–Њ–Љ, —З—В–Њ –≤—Л–±–Њ—А–Ї–∞ –Ї–Њ–Љ–∞–љ–і—Л –Ј–∞–љ–Є–Љ–∞–µ—В –Њ–і–Є–љ —Ж–Є–Ї–ї, –∞ –≤—Л–њ–Њ–ї–љ–µ–љ–Є–µ вАУ —Б–ї–µ–і—Г—О—Й–Є–є —Ж–Є–Ї–ї.

–≠—Д—Д–µ–Ї—В–Є–≤–љ–Њ–µ –≤—А–µ–Љ—П –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –Ї–Њ–Љ–∞–љ–і—Л —Б–Њ—Б—В–∞–≤–ї—П–µ—В –Њ–і–Є–љ —Ж–Є–Ї–ї. –Х—Б–ї–Є –Ї–Њ–Љ–∞–љ–і–∞

–Є–Ј–Љ–µ–љ—П–µ—В —Б—З–µ—В—З–Є–Ї –Ї–Њ–Љ–∞–љ–і (–љ–∞–њ—А–Є–Љ–µ—А, –Ї–Њ–Љ–∞–љ–і–∞ GOTO), —В–Њ –і–ї—П –µ–µ –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –њ–Њ—В—А–µ–±—Г–µ—В—Б—П –і–≤–∞ —Ж–Є–Ї–ї–∞, –Ї–∞–Ї –њ–Њ–Ї–∞–Ј–∞–љ–Њ

–љ–∞ —А–Є—Б. 5.3.

–†–Є—Б. 2. –°—Е–µ–Љ–∞ —В–∞–Ї—В–Є—А–Њ–≤–∞–љ–Є—П –Є –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –Ї–Њ–Љ–∞–љ–і—Л

–†–Є—Б. 3. –Т—Л–±–Њ—А–Ї–∞ –Ї–Њ–Љ–∞–љ–і

–¶–Є–Ї–ї –≤—Л–±–Њ—А–Ї–Є –љ–∞—З–Є–љ–∞–µ—В—Б—П —Б —Г–≤–µ–ї–Є—З–µ–љ–Є—П

—Б—З–µ—В—З–Є–Ї–∞ –Ї–Њ–Љ–∞–љ–і –≤ —В–∞–Ї—В–µ Q1. –Т —Ж–Є–Ї–ї–µ –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –Ї–Њ–Љ–∞–љ–і—Л –≤—Л–±—А–∞–љ–љ–∞—П –Ї–Њ–Љ–∞–љ–і–∞ –Ј–∞—Й–µ–ї–Ї–Є–≤–∞–µ—В—Б—П

–≤ —А–µ–≥–Є—Б—В—А –Ї–Њ–Љ–∞–љ–і –≤ —В–∞–Ї—В–µ Q1. –Т —В–µ—З–µ–љ–Є–µ —В–∞–Ї—В–Њ–≤ Q2, Q3 –Є Q4 –њ—А–Њ–Є—Б—Е–Њ–і–Є—В –і–µ–Ї–Њ–і–Є—А–Њ–≤–∞–љ–Є–µ –Є –≤—Л–њ–Њ–ї–љ–µ–љ–Є–µ –Ї–Њ–Љ–∞–љ–і—Л. –Т —В–∞–Ї—В–µ Q2 —Б—З–Є—В—Л–≤–∞–µ—В—Б—П –њ–∞–Љ—П—В—М –і–∞–љ–љ—Л—Е (—З—В–µ–љ–Є–µ –Њ–њ–µ—А–∞–љ–і–∞), –∞ –Ј–∞–њ–Є—Б—М

–њ—А–Њ–Є—Б—Е–Њ–і–Є—В –≤ —В–∞–Ї—В–µ Q4.

4. –Ю—А–≥–∞–љ–Є–Ј–∞—Ж–Є—П –њ–∞–Љ—П—В–Є –њ—А–Њ–≥—А–∞–Љ–Љ –Є —Б—В–µ–Ї–∞

–°—З–µ—В—З–Є–Ї –Ї–Њ–Љ–∞–љ–і –≤ –Ь–Ъ PIC16F8–• –Є–Љ–µ–µ—В —И–Є—А–Є–љ—Г

13 –±–Є—В –Є —Б–њ–Њ—Б–Њ–±–µ–љ –∞–і—А–µ—Б–Њ–≤–∞—В—М 8–Ъ—Е14–±–Є—В –Њ–±—К–µ–Љ–∞ –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–є –њ–∞–Љ—П—В–Є. –Ю–і–љ–∞–Ї–Њ

—Д–Є–Ј–Є—З–µ—Б–Ї–Є –љ–∞ –Ї—А–Є—Б—В–∞–ї–ї–∞—Е PIC16F83 –Є PIC16CR83 –Є–Љ–µ–µ—В—Б—П —В–Њ–ї—М–Ї–Њ 512—Е14 –њ–∞–Љ—П—В–Є

(–∞–і—А–µ—Б–∞ 0000h-01FFh), –∞ –≤ –Ь–Ъ

PIC16F84 –Є PIC16CR84 вАУ 1–Ъ—Е14 –њ–∞–Љ—П—В–Є (–∞–і—А–µ—Б–∞ 0000h-03FFh). –Ю–±—А–∞—Й–µ–љ–Є–µ –Ї –∞–і—А–µ—Б–∞–Љ –≤—Л—И–µ 1FFh (3FFh) —Д–∞–Ї—В–Є—З–µ—Б–Ї–Є –µ—Б—В—М –∞–і—А–µ—Б–∞—Ж–Є—П –≤ —В–µ –ґ–µ –њ–µ—А–≤—Л–µ 512 –∞–і—А–µ—Б–Њ–≤ (–њ–µ—А–≤—Л–µ 1–Ъ –∞–і—А–µ—Б–Њ–≤).

–Ю—А–≥–∞–љ–Є–Ј–∞—Ж–Є—П –њ–∞–Љ—П—В–Є –њ—А–Њ–≥—А–∞–Љ–Љ –Є —Б—В–µ–Ї–∞

–њ—А–Є–≤–µ–і–µ–љ–∞ –љ–∞ —А–Є—Б. 4.

–Т –њ–∞–Љ—П—В–Є –њ—А–Њ–≥—А–∞–Љ–Љ –µ—Б—В—М –≤—Л–і–µ–ї–µ–љ–љ—Л–µ –∞–і—А–µ—Б–∞.

–Т–µ–Ї—В–Њ—А —Б–±—А–Њ—Б–∞ –љ–∞—Е–Њ–і–Є—В—Б—П –њ–Њ –∞–і—А–µ—Б—Г 0000h, –≤–µ–Ї—В–Њ—А –њ—А–µ—А—Л–≤–∞–љ–Є—П вАУ –њ–Њ –∞–і—А–µ—Б—Г 0004h. –Ю–±—Л—З–љ–Њ –њ–Њ –∞–і—А–µ—Б—Г 0004h —А–∞—Б–њ–Њ–ї–∞–≥–∞–µ—В—Б—П –њ–Њ–і–њ—А–Њ–≥—А–∞–Љ–Љ–∞ –Є–і–µ–љ—В–Є—Д–Є–Ї–∞—Ж–Є–Є –Є –Њ–±—А–∞–±–Њ—В–Ї–Є –њ—А–µ—А—Л–≤–∞–љ–Є–є, –∞ –њ–Њ –∞–і—А–µ—Б—Г 0000h вАУ –Ї–Њ–Љ–∞–љ–і–∞ –њ–µ—А–µ—Е–Њ–і–∞ –љ–∞ –Љ–µ—В–Ї—Г, —А–∞—Б–њ–Њ–ї–Њ–ґ–µ–љ–љ—Г—О –Ј–∞ –њ–Њ–і–њ—А–Њ–≥—А–∞–Љ–Љ–Њ–є

–Њ–±—А–∞–±–Њ—В–Ї–Є –њ—А–µ—А—Л–≤–∞–љ–Є–є.

–†–Є—Б. 4. –Ю—А–≥–∞–љ–Є–Ј–∞—Ж–Є—П –њ–∞–Љ—П—В–Є –њ—А–Њ–≥—А–∞–Љ–Љ –Є —Б—В–µ–Ї–∞

5. –Ю—А–≥–∞–љ–Є–Ј–∞—Ж–Є—П –њ–∞–Љ—П—В–Є –і–∞–љ–љ—Л—Е

–Я–∞–Љ—П—В—М –і–∞–љ–љ—Л—Е –Ь–Ъ —А–∞–Ј–±–Є—В–∞ –љ–∞ –і–≤–µ –Њ–±–ї–∞—Б—В–Є.

–Я–µ—А–≤—Л–µ 12 –∞–і—А–µ—Б–Њ–≤ вАУ —Н—В–Њ –Њ–±–ї–∞—Б—В—М —А–µ–≥–Є—Б—В—А–Њ–≤

—Б–њ–µ—Ж–Є–∞–ї—М–љ—Л—Е —Д—Г–љ–Ї—Ж–Є–є (SFR), –∞ –≤—В–Њ—А–∞—П вАУ –Њ–±–ї–∞—Б—В—М —А–µ–≥–Є—Б—В—А–Њ–≤

–Њ–±—Й–µ–≥–Њ –љ–∞–Ј–љ–∞—З–µ–љ–Є—П (GPR). –Ю–±–ї–∞—Б—В—М SFR —Г–њ—А–∞–≤–ї—П–µ—В —А–∞–±–Њ—В–Њ–є –њ—А–Є–±–Њ—А–∞.

–Ю–±–µ –Њ–±–ї–∞—Б—В–Є —А–∞–Ј–±–Є—В—Л –≤ —Б–≤–Њ—О –Њ—З–µ—А–µ–і—М –љ–∞ –±–∞–љ–Ї–Є

0 –Є 1. –С–∞–љ–Ї 0 –≤—Л–±–Є—А–∞–µ—В—Б—П –Њ–±–љ—Г–ї–µ–љ–Є–µ–Љ –±–Є—В–∞ RP0 —А–µ–≥–Є—Б—В—А–∞ —Б—В–∞—В—Г—Б–∞ (STATUS). –£—Б—В–∞–љ–Њ–≤–Ї–∞ –±–Є—В–∞ RP0 –≤ –µ–і–Є–љ–Є—Ж—Г –≤—Л–±–Є—А–∞–µ—В –±–∞–љ–Ї 1. –Ъ–∞–ґ–і—Л–є –±–∞–љ–Ї –Є–Љ–µ–µ—В –њ—А–Њ—В—П–ґ–µ–љ–љ–Њ—Б—В—М

128 –±–∞–є—В. –Ю–і–љ–∞–Ї–Њ –і–ї—П PIC16F83 –Є PIC16CR83 –њ–∞–Љ—П—В—М –і–∞–љ–љ—Л—Е —Б—Г—Й–µ—Б—В–≤—Г–µ—В —В–Њ–ї—М–Ї–Њ –і–Њ

–∞–і—А–µ—Б–∞ 02Fh, –∞ –і–ї—П PIC16F84 –Є

PIC16CR84 вАУ –і–Њ –∞–і—А–µ—Б–∞ 04Fh.

–Э–∞ —А–Є—Б. 5 –Є–Ј–Њ–±—А–∞–ґ–µ–љ–∞ –Њ—А–≥–∞–љ–Є–Ј–∞—Ж–Є—П –њ–∞–Љ—П—В–Є

–і–∞–љ–љ—Л—Е.

–†–Є—Б. 5. –Ю—А–≥–∞–љ–Є–Ј–∞—Ж–Є—П –њ–∞–Љ—П—В–Є –і–∞–љ–љ—Л—Е

–Э–µ–Ї–Њ—В–Њ—А—Л–µ —А–µ–≥–Є—Б—В—А—Л

—Б–њ–µ—Ж–Є–∞–ї—М–љ–Њ–≥–Њ –љ–∞–Ј–љ–∞—З–µ–љ–Є—П –њ—А–Њ–і—Г–±–ї–Є—А–Њ–≤–∞–љ—Л –≤ –Њ–±–Њ–Є—Е –±–∞–љ–Ї–∞—Е, –∞ –љ–µ–Ї–Њ—В–Њ—А—Л–µ —А–∞—Б–њ–Њ–ї–Њ–ґ–µ–љ—Л

–≤ –±–∞–љ–Ї–µ 1 –Њ—В–і–µ–ї—М–љ–Њ.

–†–µ–≥–Є—Б—В—А—Л —Б –∞–і—А–µ—Б–∞–Љ–Є 0Ch-4Fh –Љ–Њ–≥—Г—В –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М—Б—П –Ї–∞–Ї —А–µ–≥–Є—Б—В—А—Л –Њ–±—Й–µ–≥–Њ –љ–∞–Ј–љ–∞—З–µ–љ–Є—П, –Ї–Њ—В–Њ—А—Л–µ –њ—А–µ–і—Б—В–∞–≤–ї—П—О—В —Б–Њ–±–Њ–є

—Б—В–∞—В–Є—З–µ—Б–Ї–Њ–µ –Ю–Ч–£. –Р–і—А–µ—Б–∞ —А–µ–≥–Є—Б—В—А–Њ–≤ –Њ–±—Й–µ–≥–Њ –љ–∞–Ј–љ–∞—З–µ–љ–Є—П

–±–∞–љ–Ї–∞ 1 –Њ—В–Њ–±—А–∞–ґ–∞—О—В—Б—П –љ–∞ –±–∞–љ–Ї 0. –°–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ, –Ї–Њ–≥–і–∞ —Г—Б—В–∞–љ–Њ–≤–ї–µ–љ –±–∞–љ–Ї 1, —В–Њ

–Њ–±—А–∞—Й–µ–љ–Є–µ –Ї –∞–і—А–µ—Б–∞–Љ 8Ch-CFh —Д–∞–Ї—В–Є—З–µ—Б–Ї–Є –∞–і—А–µ—Б—Г–µ—В –±–∞–љ–Ї 0.

–Т —А–µ–≥–Є—Б—В—А–µ

—Б—В–∞—В—Г—Б–∞ –њ–Њ–Љ–Є–Љ–Њ –±–Є—В–∞ RP0 –µ—Б—В—М –µ—Й–µ –±–Є—В RB1, —З—В–Њ –њ–Њ–Ј–≤–Њ–ї—П–µ—В –Њ–±—А–∞—Й–∞—В—М—Б—П –Ї —З–µ—В—Л—А–µ–Љ —Б—В—А–∞–љ–Є—Ж–∞–Љ (–±–∞–љ–Ї–∞–Љ)

–±—Г–і—Г—Й–Є—Е –Љ–Њ–і–Є—Д–Є–Ї–∞—Ж–Є–є —Н—В–Њ–≥–Њ –Ї—А–Є—Б—В–∞–ї–ї–∞.

–Ъ —П—З–µ–є–Ї–∞–Љ –Ю–Ч–£ –Љ–Њ–ґ–љ–Њ –∞–і—А–µ—Б–Њ–≤–∞—В—М—Б—П –њ—А—П–Љ–Њ,

–Є—Б–њ–Њ–ї—М–Ј—Г—П –∞–±—Б–Њ–ї—О—В–љ—Л–є –∞–і—А–µ—Б –Ї–∞–ґ–і–Њ–≥–Њ —А–µ–≥–Є—Б—В—А–∞, –Є–ї–Є

–Ї–Њ—Б–≤–µ–љ–љ–Њ, —З–µ—А–µ–Ј —А–µ–≥–Є—Б—В—А —Г–Ї–∞–Ј–∞—В–µ–ї—М FSR. –Ъ–Њ—Б–≤–µ–љ–љ–∞—П –∞–і—А–µ—Б–∞—Ж–Є—П –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В

—В–µ–Ї—Г—Й–µ–µ –Ј–љ–∞—З–µ–љ–Є–µ —А–∞–Ј—А—П–і–Њ–≤ RP1:RP0 –і–ї—П

–і–Њ—Б—В—Г–њ–∞ –Ї –±–∞–љ–Ї–∞–Љ. –≠—В–Њ –Њ—В–љ–Њ—Б–Є—В—Б—П –Є –Ї EEPROM –њ–∞–Љ—П—В–Є –і–∞–љ–љ—Л—Е. –Т –Њ–±–Њ–Є—Е —Б–ї—Г—З–∞—П—Е –Љ–Њ–ґ–љ–Њ –∞–і—А–µ—Б–Њ–≤–∞—В—М –і–Њ 512 —А–µ–≥–Є—Б—В—А–Њ–≤.

6. –†–µ–≥–Є—Б—В—А—Л —Б–њ–µ—Ж–Є–∞–ї—М–љ–Њ–≥–Њ –љ–∞–Ј–љ–∞—З–µ–љ–Є—П

–†–µ–≥–Є—Б—В—А —Б—В–∞—В—Г—Б–∞ (STATUS) —Б–Њ–і–µ—А–ґ–Є—В –њ—А–Є–Ј–љ–∞–Ї–Є –Њ–њ–µ—А–∞—Ж–Є–Є (–∞—А–Є—Д–Љ–µ—В–Є—З–µ—Б–Ї–Є–µ —Д–ї–∞–≥–Є) –Р–Ы–£,

—Б–Њ—Б—В–Њ—П–љ–Є–µ –Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –њ—А–Є —Б–±—А–Њ—Б–µ –Є –±–Є—В—Л –≤—Л–±–Њ—А–∞ —Б—В—А–∞–љ–Є—Ж –і–ї—П –њ–∞–Љ—П—В–Є –і–∞–љ–љ—Л—Е.

–Ч–і–µ—Б—М –Є –і–∞–ї–µ–µ:

R вАФ —З–Є—В–∞–µ–Љ—Л–є –±–Є—В; W вАФ –Ј–∞–њ–Є—Б—Л–≤–∞–µ–Љ—Л–є –±–Є—В; S вАФ —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞–µ–Љ—Л–є –±–Є—В; U вАФ

–љ–µ–Є—Б–њ–Њ–ї—М–Ј—Г–µ–Љ—Л–є –±–Є—В (—З–Є—В–∞–µ—В—Б—П –Ї–∞–Ї "0"); -n = 0 –Є–ї–Є 1 вАФ –Ј–љ–∞—З–µ–љ–Є–µ –±–Є—В–∞

–њ–Њ—Б–ї–µ —Б–±—А–Њ—Б–∞.

–†–µ–≥–Є—Б—В—А —Б—В–∞—В—Г—Б–∞ –і–Њ—Б—В—Г–њ–µ–љ –і–ї—П –ї—О–±–Њ–є –Ї–Њ–Љ–∞–љ–і—Л —В–∞–Ї –ґ–µ, –Ї–∞–Ї –ї—О–±–Њ–є –і—А—Г–≥–Њ–є —А–µ–≥–Є—Б—В—А. –Ю–і–љ–∞–Ї–Њ –µ—Б–ї–Є —А–µ–≥–Є—Б—В—А

STATUS —П–≤–ї—П–µ—В—Б—П —А–µ–≥–Є—Б—В—А–Њ–Љ –љ–∞–Ј–љ–∞—З–µ–љ–Є—П –і–ї—П –Ї–Њ–Љ–∞–љ–і—Л, –≤–ї–Є—П—О—Й–µ–є –љ–∞ –±–Є—В—Л Z, DC –Є–ї–Є C, —В–Њ –Ј–∞–њ–Є—Б—М –≤ —Н—В–Є —В—А–Є –±–Є—В–∞ –Ј–∞–њ—А–µ—Й–∞–µ—В—Б—П. –Ъ—А–Њ–Љ–µ —В–Њ–≥–Њ, –±–Є—В—Л /TO –Є /PD —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞—О—В—Б—П –∞–њ–њ–∞—А–∞—В–љ–Њ

–Є –љ–µ –Љ–Њ–≥—Г—В –±—Л—В—М –Ј–∞–њ–Є—Б–∞–љ—Л –≤ —Б—В–∞—В—Г—Б –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ. –≠—В–Њ —Б–ї–µ–і—Г–µ—В –Є–Љ–µ—В—М –≤ –≤–Є–і—Г –њ—А–Є –≤—Л–њ–Њ–ї–љ–µ–љ–Є–Є

–Ї–Њ–Љ–∞–љ–і—Л —Б –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–µ–Љ —А–µ–≥–Є—Б—В—А–∞ —Б—В–∞—В—Г—Б–∞.

–Э–∞–њ—А–Є–Љ–µ—А, –Ї–Њ–Љ–∞–љ–і–∞ CLRF STATUS –Њ–±–љ—Г–ї–Є—В –≤—Б–µ

–±–Є—В—Л, –Ї—А–Њ–Љ–µ –±–Є—В–Њ–≤ /TO –Є /PD, –∞ –Ј–∞—В–µ–Љ —Г—Б—В–∞–љ–Њ–≤–Є—В –±–Є—В Z=1. –Я–Њ—Б–ї–µ –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П —Н—В–Њ–є –Ї–Њ–Љ–∞–љ–і—Л —А–µ–≥–Є—Б—В—А

—Б—В–∞—В—Г—Б–∞ –Љ–Њ–ґ–µ—В –Є –љ–µ –Є–Љ–µ—В—М –љ—Г–ї–µ–≤–Њ–≥–Њ –Ј–љ–∞—З–µ–љ–Є—П (–Є–Ј-–Ј–∞ –±–Є—В–Њ–≤ /TO –Є /PD) STATUS=000uu1uu, –≥–і–µ u вАУ –љ–µ–Є–Ј–Љ–µ–љ—П–µ–Љ–Њ–µ

—Б–Њ—Б—В–Њ—П–љ–Є–µ. –Я–Њ—Н—В–Њ–Љ—Г —А–µ–Ї–Њ–Љ–µ–љ–і—Г–µ—В—Б—П –і–ї—П –Є–Ј–Љ–µ–љ–µ–љ–Є—П —А–µ–≥–Є—Б—В—А–∞

—Б—В–∞—В—Г—Б–∞ –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М —В–Њ–ї—М–Ї–Њ –Ї–Њ–Љ–∞–љ–і—Л –±–Є—В–Њ–≤–Њ–є —Г—Б—В–∞–љ–Њ–≤–Ї–Є BCF, BSF, MOVWF, –Ї–Њ—В–Њ—А—Л–µ –љ–µ –Є–Ј–Љ–µ–љ—П—О—В –Њ—Б—В–∞–ї—М–љ—Л–µ –±–Є—В—Л —Б—В–∞—В—Г—Б–∞. –Т–Њ–Ј–і–µ–є—Б—В–≤–Є–µ

–≤—Б–µ—Е –Ї–Њ–Љ–∞–љ–і –љ–∞ –±–Є—В—Л —Б—В–∞—В—Г—Б–∞ —А–∞—Б—Б–Љ–∞—В—А–Є–≤–∞–µ—В—Б—П –≤ —А–∞–Ј–і–µ–ї–µ "–Ю–њ–Є—Б–∞–љ–Є–µ —Б–Є—Б—В–µ–Љ—Л

–Ї–Њ–Љ–∞–љ–і".

–†–µ–≥–Є—Б—В—А –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є (OPTION) —П–≤–ї—П–µ—В—Б—П –і–Њ—Б—В—Г–њ–љ—Л–Љ –њ–Њ —З—В–µ–љ–Є—О –Є –Ј–∞–њ–Є—Б–Є —А–µ–≥–Є—Б—В—А–Њ–Љ,

–Ї–Њ—В–Њ—А—Л–є —Б–Њ–і–µ—А–ґ–Є—В —Г–њ—А–∞–≤–ї—П—О—Й–Є–µ –±–Є—В—Л –і–ї—П –Ї–Њ–љ—Д–Є–≥—Г—А–∞—Ж–Є–Є –њ—А–µ–і–≤–∞—А–Є—В–µ–ї—М–љ–Њ–≥–Њ –і–µ–ї–Є—В–µ–ї—П

(–њ—А–µ–і–µ–ї–Є—В–µ–ї—П), –≤–љ–µ—И–љ–Є—Е –њ—А–µ—А—Л–≤–∞–љ–Є–є, —В–∞–є–Љ–µ—А–∞, –∞ —В–∞–Ї–ґ–µ —А–µ–Ј–Є—Б—В–Њ—А–Њ–≤ "pull-up" –љ–∞

–≤—Л–≤–Њ–і–∞—Е PORTB.

–Т —В–Њ–Љ —Б–ї—Г—З–∞–µ,

–Ї–Њ–≥–і–∞ –њ—А–µ–і–і–µ–ї–Є—В–µ–ї—М –Њ–±—Б–ї—Г–ґ–Є–≤–∞–µ—В —Б—В–Њ—А–Њ–ґ–µ–≤–Њ–є —В–∞–є–Љ–µ—А

WDT, —В–∞–є–Љ–µ—А—Г

TMR0 –љ–∞–Ј–љ–∞—З–∞–µ—В—Б—П –Ї–Њ—Н—Д—Д–Є—Ж–Є–µ–љ—В

–њ—А–µ–і–≤–∞—А–Є—В–µ–ї—М–љ–Њ–≥–Њ –і–µ–ї–µ–љ–Є—П 1:1.

–†–µ–≥–Є—Б—В—А —Г—Б–ї–Њ–≤–Є–є –њ—А–µ—А—Л–≤–∞–љ–Є—П (INTCON) —П–≤–ї—П–µ—В—Б—П –і–Њ—Б—В—Г–њ–љ—Л–Љ –њ–Њ —З—В–µ–љ–Є—О –Є –Ј–∞–њ–Є—Б–Є —А–µ–≥–Є—Б—В—А–Њ–Љ,

–Ї–Њ—В–Њ—А—Л–є —Б–Њ–і–µ—А–ґ–Є—В –±–Є—В—Л –і–Њ—Б—В—Г–њ–∞ –і–ї—П –≤—Б–µ—Е –Є—Б—В–Њ—З–љ–Є–Ї–Њ–≤ –њ—А–µ—А—Л–≤–∞–љ–Є–є.

–С–Є—В —А–∞–Ј—А–µ—И–µ–љ–Є—П –≤—Б–µ—Е –њ—А–µ—А—Л–≤–∞–љ–Є–є

GIE —Б–±—А–∞—Б—Л–≤–∞–µ—В—Б—П –∞–≤—В–Њ–Љ–∞—В–Є—З–µ—Б–Ї–Є

–њ—А–Є —Б–ї–µ–і—Г—О—Й–Є—Е –Њ–±—Б—В–Њ—П—В–µ–ї—М—Б—В–≤–∞—Е:

¬Ј

–њ–Њ –≤–Ї–ї—О—З–µ–љ–Є—О –њ–Є—В–∞–љ–Є—П;

¬Ј

–њ–Њ –≤–љ–µ—И–љ–µ–Љ—Г —Б–Є–≥–љ–∞–ї—Г /MCLR –њ—А–Є

–љ–Њ—А–Љ–∞–ї—М–љ–Њ–є —А–∞–±–Њ—В–µ;

¬Ј

–њ–Њ –≤–љ–µ—И–љ–µ–Љ—Г —Б–Є–≥–љ–∞–ї—Г /MCLR –≤

—А–µ–ґ–Є–Љ–µ SLEEP;

¬Ј

–њ–Њ –Њ–Ї–Њ–љ—З–∞–љ–Є—О –Ј–∞–і–µ—А–ґ–Ї–Є —В–∞–є–Љ–µ—А–∞

WDT –њ—А–Є –љ–Њ—А–Љ–∞–ї—М–љ–Њ–є —А–∞–±–Њ—В–µ;

¬Ј

–њ–Њ –Њ–Ї–Њ–љ—З–∞–љ–Є—О –Ј–∞–і–µ—А–ґ–Ї–Є —В–∞–є–Љ–µ—А–∞

WDT –≤ —А–µ–ґ–Є–Љ–µ SLEEP.

–Я—А–µ—А—Л–≤–∞–љ–Є–µ INT –Љ–Њ–ґ–µ—В –≤—Л–≤–µ—Б—В–Є

–њ—А–Њ—Ж–µ—Б—Б–Њ—А –Є–Ј —А–µ–ґ–Є–Љ–∞ SLEEP, –µ—Б–ї–Є –њ–µ—А–µ–і –≤—Е–Њ–і–Њ–Љ –≤ —Н—В–Њ—В

—А–µ–ґ–Є–Љ –±–Є—В INTE –±—Л–ї —Г—Б—В–∞–љ–Њ–≤–ї–µ–љ –≤ –µ–і–Є–љ–Є—Ж—Г.

–°–Њ—Б—В–Њ—П–љ–Є–µ –±–Є—В–∞ GIE —В–∞–Ї–ґ–µ –Њ–њ—А–µ–і–µ–ї—П–µ—В: –±—Г–і–µ—В

–ї–Є –њ—А–Њ—Ж–µ—Б—Б–Њ—А –њ–µ—А–µ—Е–Њ–і–Є—В—М –љ–∞ –њ–Њ–і–њ—А–Њ–≥—А–∞–Љ–Љ—Г –њ—А–µ—А—Л–≤–∞–љ–Є—П

–њ–Њ—Б–ї–µ –≤—Л—Е–Њ–і–∞ –Є–Ј —А–µ–ґ–Є–Љ–∞ SLEEP.

–°–±—А–Њ—Б –±–Є—В–Њ–≤ вАУ –Ј–∞–њ—А–Њ—Б–Њ–≤ –њ—А–µ—А—Л–≤–∞–љ–Є–є вАУ –і–Њ–ї–ґ–µ–љ –Њ—Б—Г—Й–µ—Б—В–≤–ї—П—В—М—Б—П —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–µ–є –њ—А–Њ–≥—А–∞–Љ–Љ–Њ–є

–Њ–±—А–∞–±–Њ—В–Ї–Є.

7. –°—З–µ—В—З–Є–Ї –Ї–Њ–Љ–∞–љ–і

–°—З–µ—В—З–Є–Ї –Ї–Њ–Љ–∞–љ–і PCL –Є PCLATH –Є–Љ–µ–µ—В —А–∞–Ј—А—П–і–љ–Њ—Б—В—М 13 –±–Є—В.

–Ь–ї–∞–і—И–Є–є –±–∞–є—В —Б—З–µ—В—З–Є–Ї–∞ (PCL) –і–Њ—Б—В—Г–њ–µ–љ –і–ї—П

—З—В–µ–љ–Є—П –Є –Ј–∞–њ–Є—Б–Є –Є –љ–∞—Е–Њ–і–Є—В—Б—П –≤ —А–µ–≥–Є—Б—В—А–µ 02h. –°—В–∞—А—И–Є–є –±–∞–є—В —Б—З–µ—В—З–Є–Ї–∞ –Ї–Њ–Љ–∞–љ–і –љ–µ –Љ–Њ–ґ–µ—В –±—Л—В—М –љ–∞–њ—А—П–Љ—Г—О –Ј–∞–њ–Є—Б–∞–љ

–Є–ї–Є —Б—З–Є—В–∞–љ –Є –±–µ—А–µ—В—Б—П –Є–Ј —А–µ–≥–Є—Б—В—А–∞ PCLATH (PC latch high), –∞–і—А–µ—Б –Ї–Њ—В–Њ—А–Њ–≥–Њ 0Ah. –°–Њ–і–µ—А–ґ–Є–Љ–Њ–µ PCLATH –њ–µ—А–µ–і–∞–µ—В—Б—П –≤ —Б—В–∞—А—И–Є–є –±–∞–є—В —Б—З–µ—В—З–Є–Ї–∞ –Ї–Њ–Љ–∞–љ–і, –Ї–Њ–≥–і–∞ –Њ–љ –Ј–∞–≥—А—Г–ґ–∞–µ—В—Б—П

–љ–Њ–≤—Л–Љ –Ј–љ–∞—З–µ–љ–Є–µ–Љ.

–Т –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В —В–Њ–≥–Њ, –Ј–∞–≥—А—Г–ґ–∞–µ—В—Б—П –ї–Є –≤

—Б—З–µ—В—З–Є–Ї –Ї–Њ–Љ–∞–љ–і –љ–Њ–≤–Њ–µ –Ј–љ–∞—З–µ–љ–Є–µ –≤–Њ –≤—А–µ–Љ—П –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –Ї–Њ–Љ–∞–љ–і CALL, GOTO, –Є–ї–Є –≤ –Љ–ї–∞–і—И–Є–є –±–∞–є—В

—Б—З–µ—В—З–Є–Ї–∞ –Ї–Њ–Љ–∞–љ–і (PCL) –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В—Б—П –Ј–∞–њ–Є—Б—М, вАУ

—Б—В–∞—А—И–Є–µ –±–Є—В—Л —Б—З–µ—В—З–Є–Ї–∞ –Ї–Њ–Љ–∞–љ–і –Ј–∞–≥—А—Г–ґ–∞—О—В—Б—П –Є–Ј PCLATH —А–∞–Ј–љ—Л–Љ–Є —Б–њ–Њ—Б–Њ–±–∞–Љ–Є, –Ї–∞–Ї –њ–Њ–Ї–∞–Ј–∞–љ–Њ –љ–∞ —А–Є—Б. 6.

–†–Є—Б. 5.6. –Ч–∞–≥—А—Г–Ј–Ї–∞ —Б—В–∞—А—И–Є—Е –±–Є—В —Б—З–µ—В—З–Є–Ї–∞ –Ї–Њ–Љ–∞–љ–і

–Ъ–Њ–Љ–∞–љ–і—Л CALL –Є GOTO –Њ–њ–µ—А–Є—А—Г—О—В 11-—А–∞–Ј—А—П–і–љ—Л–Љ

–∞–і—А–µ—Б–љ—Л–Љ –і–Є–∞–њ–∞–Ј–Њ–љ–Њ–Љ, –і–Њ—Б—В–∞—В–Њ—З–љ—Л–Љ –і–ї—П —Б–Љ–µ—Й–µ–љ–Є—П –≤ –њ—А–µ–і–µ–ї–∞—Е —Б—В—А–∞–љ–Є—Ж—Л –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–є

–њ–∞–Љ—П—В–Є –Њ–±—К–µ–Љ–Њ–Љ 2–Ъ —Б–ї–Њ–≤. –Ф–ї—П –Ь–Ъ –њ–Њ–і–≥—А—Г–њ–њ—Л PIC16F8X —Н—В–Њ–≥–Њ —Е–≤–∞—В–∞–µ—В. –° —Ж–µ–ї—М—О

–Њ–±–µ—Б–њ–µ—З–µ–љ–Є—П –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В–Є —А–∞—Б—И–Є—А–µ–љ–Є—П –њ–∞–Љ—П—В–Є –Ї–Њ–Љ–∞–љ–і –і–ї—П –±—Г–і—Г—Й–Є—Е –Љ–Њ–і–µ–ї–µ–є –Ь–Ъ

–њ—А–µ–і—Г—Б–Љ–Њ—В—А–µ–љ–∞ –Ј–∞–≥—А—Г–Ј–Ї–∞ –і–≤—Г—Е —Б—В–∞—А—И–Є—Е –±–Є—В —Б—З–µ—В—З–Є–Ї–∞ –Ї–Њ–Љ–∞–љ–і –Є–Ј —А–µ–≥–Є—Б—В—А–∞ PCLATH<4:3>. –Я—А–Є –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–Є –Ї–Њ–Љ–∞–љ–і CALL –Є GOTO –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—М –і–Њ–ї–ґ–µ–љ —Г–±–µ–і–Є—В—М—Б—П

–≤ —В–Њ–Љ, —З—В–Њ —Н—В–Є —Б—В—А–∞–љ–Є—З–љ—Л–µ –±–Є—В—Л –Ј–∞–њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ—Л –і–ї—П –≤—Л—Е–Њ–і–∞ –љ–∞ –љ—Г–ґ–љ—Г—О —Б—В—А–∞–љ–Є—Ж—Г.

–Я—А–Є –≤—Л–њ–Њ–ї–љ–µ–љ–Є–Є –Ї–Њ–Љ–∞–љ–і—Л CALL –Є–ї–Є –≤—Л–њ–Њ–ї–љ–µ–љ–Є–Є

–њ—А–µ—А—Л–≤–∞–љ–Є—П –≤–µ—Б—М 13-–±–Є—В–љ—Л–є —Б—З–µ—В—З–Є–Ї –Ї–Њ–Љ–∞–љ–і –њ–Њ–Љ–µ—Й–∞–µ—В—Б—П

–≤ —Б—В–µ–Ї, –њ–Њ—Н—В–Њ–Љ—Г –і–ї—П –≤–Њ–Ј–≤—А–∞—Й–µ–љ–Є—П –Є–Ј –њ–Њ–і–њ—А–Њ–≥—А–∞–Љ–Љ—Л –љ–µ –љ—Г–ґ–љ—Л –Љ–∞–љ–Є–њ—Г–ї—П—Ж–Є–Є —Б —А–∞–Ј—А—П–і–∞–Љ–Є

PCLATH<4:3>.

–Ь–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Л –њ–Њ–і–≥—А—Г–њ–њ—Л PIC16F8X

–Є–≥–љ–Њ—А–Є—А—Г—О—В –Ј–љ–∞—З–µ–љ–Є—П –±–Є—В PCLATH<4:3>, –Ї–Њ—В–Њ—А—Л–µ –Є—Б–њ–Њ–ї—М–Ј—Г—О—В—Б—П –і–ї—П –Њ–±—А–∞—Й–µ–љ–Є—П –Ї —Б—В—А–∞–љ–Є—Ж–∞–Љ 1, 2 –Є 3 –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–є

–њ–∞–Љ—П—В–Є. –Ю–і–љ–∞–Ї–Њ –њ—А–Є–Љ–µ–љ—П—В—М –±–Є—В—Л PCLATH<4:3> –≤ –Ї–∞—З–µ—Б—В–≤–µ —П—З–µ–µ–Ї –њ–∞–Љ—П—В–Є –Њ–±—Й–µ–≥–Њ –љ–∞–Ј–љ–∞—З–µ–љ–Є—П –љ–µ —А–µ–Ї–Њ–Љ–µ–љ–і—Г–µ—В—Б—П,

—В–∞–Ї –Ї–∞–Ї —Н—В–Њ –Љ–Њ–ґ–µ—В –њ–Њ–≤–ї–Є—П—В—М –љ–∞ —Б–Њ–≤–Љ–µ—Б—В–Є–Љ–Њ—Б—В—М —Б –±—Г–і—Г—Й–Є–Љ–Є –њ–Њ–Ї–Њ–ї–µ–љ–Є—П–Љ–Є –Є–Ј–і–µ–ї–Є–є.

–Т–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В—М –≤—Л–њ–Њ–ї–љ—П—В—М –∞—А–Є—Д–Љ–µ—В–Є—З–µ—Б–Ї–Є–µ

–Њ–њ–µ—А–∞—Ж–Є–Є –љ–µ–њ–Њ—Б—А–µ–і—Б—В–≤–µ–љ–љ–Њ –љ–∞–і —Б—З–µ—В—З–Є–Ї–Њ–Љ –Ї–Њ–Љ–∞–љ–і –њ–Њ–Ј–≤–Њ–ї—П–µ—В –Њ—З–µ–љ—М –±—Л—Б—В—А–Њ –Є

—Н—Д—Д–µ–Ї—В–Є–≤–љ–Њ –Њ—Б—Г—Й–µ—Б—В–≤–ї—П—В—М —В–∞–±–ї–Є—З–љ—Л–µ –њ—А–µ–Њ–±—А–∞–Ј–Њ–≤–∞–љ–Є—П –≤ PIC-–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞—Е.

–Ь–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Л –њ–Њ–і–≥—А—Г–њ–њ—Л PIC16F8X –Є–Љ–µ—О—В

–≤–Њ—Б—М–Љ–Є—Г—А–Њ–≤–љ–µ–≤—Л–є –∞–њ–њ–∞—А–∞—В–љ—Л–є —Б—В–µ–Ї —И–Є—А–Є–љ–Њ–є 13 –±–Є—В (—Б–Љ. —А–Є—Б. 4). –Ю–±–ї–∞—Б—В—М —Б—В–µ–Ї–∞ –љ–µ

–њ—А–Є–љ–∞–і–ї–µ–ґ–Є—В –љ–Є –Ї –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–є –Њ–±–ї–∞—Б—В–Є, –љ–Є –Ї –Њ–±–ї–∞—Б—В–Є –і–∞–љ–љ—Л—Е, –∞ —Г–Ї–∞–Ј–∞—В–µ–ї—М —Б—В–µ–Ї–∞

–њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—О –љ–µ–і–Њ—Б—В—Г–њ–µ–љ. –Ґ–µ–Ї—Г—Й–µ–µ –Ј–љ–∞—З–µ–љ–Є–µ —Б—З–µ—В—З–Є–Ї–∞ –Ї–Њ–Љ–∞–љ–і –њ–Њ—Б—Л–ї–∞–µ—В—Б—П –≤ —Б—В–µ–Ї, –Ї–Њ–≥–і–∞

–≤—Л–њ–Њ–ї–љ—П–µ—В—Б—П –Ї–Њ–Љ–∞–љ–і–∞ CALL –Є–ї–Є –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В—Б—П

–Њ–±—А–∞–±–Њ—В–Ї–∞ –њ—А–µ—А—Л–≤–∞–љ–Є—П. –Я—А–Є –≤—Л–њ–Њ–ї–љ–µ–љ–Є–Є –њ—А–Њ—Ж–µ–і—Г—А—Л

–≤–Њ–Ј–≤—А–∞—В–∞ –Є–Ј –њ–Њ–і–њ—А–Њ–≥—А–∞–Љ–Љ—Л (–Ї–Њ–Љ–∞–љ–і—Л RETLW, RETFIE –Є–ї–Є RETURN) —Б–Њ–і–µ—А–ґ–Є–Љ–Њ–µ —Б—З–µ—В—З–Є–Ї–∞ –Ї–Њ–Љ–∞–љ–і –≤–Њ—Б—Б—В–∞–љ–∞–≤–ї–Є–≤–∞–µ—В—Б—П –Є–Ј —Б—В–µ–Ї–∞. –†–µ–≥–Є—Б—В—А PCLATH –њ—А–Є –Њ–њ–µ—А–∞—Ж–Є—П—Е —Б–Њ —Б—В–µ–Ї–Њ–Љ –љ–µ –Є–Ј–Љ–µ–љ—П–µ—В—Б—П.

–°—В–µ–Ї —А–∞–±–Њ—В–∞–µ—В –Ї–∞–Ї —Ж–Є–Ї–ї–Є—З–µ—Б–Ї–Є–є –±—Г—Д–µ—А.

–°–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ, –њ–Њ—Б–ї–µ —В–Њ–≥–Њ –Ї–∞–Ї —Б—В–µ–Ї –±—Л–ї –Ј–∞–≥—А—Г–ґ–µ–љ 8 —А–∞–Ј, –і–µ–≤—П—В–∞—П –Ј–∞–≥—А—Г–Ј–Ї–∞

–њ–µ—А–µ–њ–Є—И–µ—В –Ј–љ–∞—З–µ–љ–Є–µ –њ–µ—А–≤–Њ–є. –Ф–µ—Б—П—В–∞—П –Ј–∞–≥—А—Г–Ј–Ї–∞ –њ–µ—А–µ–њ–Є—И–µ—В –≤—В–Њ—А—Г—О –Є —В.–і. –Х—Б–ї–Є —Б—В–µ–Ї

–±—Л–ї –≤—Л–≥—А—Г–ґ–µ–љ 9 —А–∞–Ј, —Б—З–µ—В—З–Є–Ї –Ї–Њ–Љ–∞–љ–і —Б—В–∞–љ–Њ–≤–Є—В—Б—П —В–∞–Ї–Є–Љ –ґ–µ, –Ї–∞–Ї –њ–Њ—Б–ї–µ –њ–µ—А–≤–Њ–є –≤—Л–≥—А—Г–Ј–Ї–Є.

–Я—А–Є–Ј–љ–∞–Ї–Њ–≤ –њ–Њ–ї–Њ–ґ–µ–љ–Є—П —Б—В–µ–Ї–∞ –≤ –Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–µ –љ–µ

–њ—А–µ–і—Г—Б–Љ–Њ—В—А–µ–љ–Њ, –њ–Њ—Н—В–Њ–Љ—Г –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—М –і–Њ–ї–ґ–µ–љ —Б–∞–Љ–Њ—Б—В–Њ—П—В–µ–ї—М–љ–Њ —Б–ї–µ–і–Є—В—М –Ј–∞ —Г—А–Њ–≤–љ–µ–Љ

–≤–ї–Њ–ґ–µ–љ–Є—П –њ–Њ–і–њ—А–Њ–≥—А–∞–Љ–Љ.

8. –Я—А—П–Љ–∞—П –Є –Ї–Њ—Б–≤–µ–љ–љ–∞—П –∞–і—А–µ—Б–∞—Ж–Є–Є

–Ъ–Њ–≥–і–∞ –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В—Б—П –њ—А—П–Љ–∞—П 9-–±–Є—В–љ–∞—П –∞–і—А–µ—Б–∞—Ж–Є—П, –Љ–ї–∞–і—И–Є–µ 7 –±–Є—В –±–µ—А—Г—В—Б—П –Ї–∞–Ї –њ—А—П–Љ–Њ–є –∞–і—А–µ—Б –Є–Ј –Ї–Њ–і–∞

–Њ–њ–µ—А–∞—Ж–Є–Є, –∞ –і–≤–∞ –±–Є—В–∞ —Г–Ї–∞–Ј–∞—В–µ–ї—П —Б—В—А–∞–љ–Є—Ж (RP1, RP0) –Є–Ј —А–µ–≥–Є—Б—В—А–∞

—Б—В–∞—В—Г—Б–∞, –Ї–∞–Ї –њ–Њ–Ї–∞–Ј–∞–љ–Њ –љ–∞ —А–Є—Б. 7.

–†–Є—Б. 5.7. –Ь–µ—В–Њ–і—Л –∞–і—А–µ—Б–∞—Ж–Є–Є

–і–∞–љ–љ—Л—Е

–Я—А–Є–Ј–љ–∞–Ї–Њ–Љ –Ї–Њ—Б–≤–µ–љ–љ–Њ–є –∞–і—А–µ—Б–∞—Ж–Є–Є

—П–≤–ї—П–µ—В—Б—П –Њ–±—А–∞—Й–µ–љ–Є–µ –Ї —А–µ–≥–Є—Б—В—А—Г INDF. –Ы—О–±–∞—П –Ї–Њ–Љ–∞–љ–і–∞, –Ї–Њ—В–Њ—А–∞—П –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В INDF (–∞–і—А–µ—Б 00h) –≤ –Ї–∞—З–µ—Б—В–≤–µ —А–µ–≥–Є—Б—В—А–∞ —Д–∞–Ї—В–Є—З–µ—Б–Ї–Є –Њ–±—А–∞—Й–∞–µ—В—Б—П –Ї —Г–Ї–∞–Ј–∞—В–µ–ї—О, –Ї–Њ—В–Њ—А—Л–є

—Е—А–∞–љ–Є—В—Б—П –≤ FSR (–∞–і—А–µ—Б 04h). –І—В–µ–љ–Є–µ –Ї–Њ—Б–≤–µ–љ–љ—Л–Љ –Њ–±—А–∞–Ј–Њ–Љ —Б–∞–Љ–Њ–≥–Њ —А–µ–≥–Є—Б—В—А–∞

INDF –і–∞—Б—В —А–µ–Ј—Г–ї—М—В–∞—В 00h. –Ч–∞–њ–Є—Б—М –≤ —А–µ–≥–Є—Б—В—А INDF –Ї–Њ—Б–≤–µ–љ–љ—Л–Љ –Њ–±—А–∞–Ј–Њ–Љ –±—Г–і–µ—В –≤—Л–≥–ї—П–і–µ—В—М –Ї–∞–Ї NOP, –љ–Њ –±–Є—В—Л —Б—В–∞—В—Г—Б–∞ –Љ–Њ–≥—Г—В –±—Л—В—М –Є–Ј–Љ–µ–љ–µ–љ—Л. –Э–µ–Њ–±—Е–Њ–і–Є–Љ—Л–є 9-–±–Є—В–љ—Л–є

–∞–і—А–µ—Б —Д–Њ—А–Љ–Є—А—Г–µ—В—Б—П –Њ–±—К–µ–і–Є–љ–µ–љ–Є–µ–Љ —Б–Њ–і–µ—А–ґ–Є–Љ–Њ–≥–Њ 8-–±–Є—В–љ–Њ–≥–Њ FSR —А–µ–≥–Є—Б—В—А–∞ –Є –±–Є—В–∞ IRP –Є–Ј —А–µ–≥–Є—Б—В—А–∞ —Б—В–∞—В—Г—Б–∞ (—Б–Љ. —А–Є—Б. 5.7).

–Ю–±—А–∞—В–Є—В–µ –≤–љ–Є–Љ–∞–љ–Є–µ, —З—В–Њ –љ–µ–Ї–Њ—В–Њ—А—Л–µ —А–µ–≥–Є—Б—В—А—Л —Б–њ–µ—Ж–Є–∞–ї—М–љ—Л—Е —Д—Г–љ–Ї—Ж–Є–є —А–∞—Б–њ–Њ–ї–∞–≥–∞—О—В—Б—П –≤ –±–∞–љ–Ї–µ 1.

–І—В–Њ–±—Л –∞–і—А–µ—Б–Њ–≤–∞—В—М—Б—П –Ї –љ–Є–Љ, –љ—Г–ґ–љ–Њ –і–Њ–њ–Њ–ї–љ–Є—В–µ–ї—М–љ–Њ —Г—Б—В–∞–љ–Њ–≤–Є—В—М –≤ –µ–і–Є–љ–Є—Ж—Г –±–Є—В RP0 –≤ —А–µ–≥–Є—Б—В—А–µ —Б—В–∞—В—Г—Б–∞.

9. –Я–Њ—А—В—Л –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞

–Ъ–Њ–љ—В—А–Њ–ї–ї–µ—А—Л –њ–Њ–і–≥—А—Г–њ–њ—Л PIC16F8X –Є–Љ–µ—О—В –і–≤–∞ –њ–Њ—А—В–∞: PORTA (5 –±–Є—В) –Є PORTB (8 –±–Є—В) —Б –њ–Њ–±–Є—В–Њ–≤–Њ–є –Є–љ–і–Є–≤–Є–і—Г–∞–ї—М–љ–Њ–є –љ–∞—Б—В—А–Њ–є–Ї–Њ–є –љ–∞ –≤–≤–Њ–і –Є–ї–Є –љ–∞

–≤—Л–≤–Њ–і.

–Я–Њ—А—В A (PORTA) –њ—А–µ–і—Б—В–∞–≤–ї—П–µ—В —Б–Њ–±–Њ–є 5-–±–Є—В–Њ–≤—Л–є —Д–Є–Ї—Б–∞—В–Њ—А, —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–Є–є –≤—Л–≤–Њ–і–∞–Љ

–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ RA<4:0>. –Ы–Є–љ–Є—П RA4 –Є–Љ–µ–µ—В –≤—Е–Њ–і —В—А–Є–≥–≥–µ—А–∞ –®–Љ–Є—В—В–∞ –Є –≤—Л—Е–Њ–і —Б –Њ—В–Ї—А—Л—В—Л–Љ —Б—В–Њ–Ї–Њ–Љ. –Т—Б–µ

–Њ—Б—В–∞–ї—М–љ—Л–µ –ї–Є–љ–Є–Є –њ–Њ—А—В–∞ –Є–Љ–µ—О—В –Ґ–Ґ–Ы –≤—Е–Њ–і–љ—Л–µ —Г—А–Њ–≤–љ–Є –Є

–Ъ–Ь–Ю–Я –≤—Л—Е–Њ–і–љ—Л–µ –±—Г—Д–µ—А—Л. –Р–і—А–µ—Б —А–µ–≥–Є—Б—В—А–∞ –њ–Њ—А—В–∞ –Р вАУ 05h.

–Ъ–∞–ґ–і–Њ–є –ї–Є–љ–Є–Є –њ–Њ—А—В–∞

–њ–Њ—Б—В–∞–≤–ї–µ–љ –≤ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤–Є–µ –±–Є—В –љ–∞–њ—А–∞–≤–ї–µ–љ–Є—П –њ–µ—А–µ–і–∞—З–Є –і–∞–љ–љ—Л—Е, –Ї–Њ—В–Њ—А—Л–є —Е—А–∞–љ–Є—В—Б—П –≤

—Г–њ—А–∞–≤–ї—П—О—Й–µ–Љ —А–µ–≥–Є—Б—В—А–µ TRISA, —А–∞—Б–њ–Њ–ї–Њ–ґ–µ–љ–љ–Њ–Љ –њ–Њ –∞–і—А–µ—Б—Г 85h. –Х—Б–ї–Є –±–Є—В —Г–њ—А–∞–≤–ї—П—О—Й–µ–≥–Њ TRISA —А–µ–≥–Є—Б—В—А–∞ –Є–Љ–µ–µ—В –Ј–љ–∞—З–µ–љ–Є–µ

1, —В–Њ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–∞—П –ї–Є–љ–Є—П –±—Г–і–µ—В —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞—В—М—Б—П –љ–∞ –≤–≤–Њ–і. –Э–Њ–ї—М –њ–µ—А–µ–Ї–ї—О—З–∞–µ—В –ї–Є–љ–Є—О

–љ–∞ –≤—Л–≤–Њ–і –Є –Њ–і–љ–Њ–≤—А–µ–Љ–µ–љ–љ–Њ –≤—Л–≤–Њ–і–Є—В –љ–∞ –љ–µ–µ —Б–Њ–і–µ—А–ґ–Є–Љ–Њ–µ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–µ–≥–Њ —А–µ–≥–Є—Б—В—А–∞-—Д–Є–Ї—Б–∞—В–Њ—А–∞ –њ–Њ—А—В–∞. –Я—А–Є

–≤–Ї–ї—О—З–µ–љ–Є–Є –њ–Є—В–∞–љ–Є—П –≤—Б–µ –ї–Є–љ–Є–Є –њ–Њ—А—В–∞ –њ–Њ —Г–Љ–Њ–ї—З–∞–љ–Є—О

–љ–∞—Б—В—А–Њ–µ–љ—Л –љ–∞ –≤–≤–Њ–і.

–Э–∞ —А–Є—Б. 8 –і–∞–љ–∞ —Б—Е–µ–Љ–∞ –ї–Є–љ–Є–є RA<3:0> –њ–Њ—А—В–∞ A.

–†–Є—Б. 8. –°—Е–µ–Љ–∞ –ї–Є–љ–Є–є RA

<3:0 –њ–Њ—А—В–∞ –Р. –Т—Л–≤–Њ–і—Л –њ–Њ—А—В–∞ –Є–Љ–µ—О—В –Ј–∞—Й–Є—В–љ—Л–µ –і–Є–Њ–і—Л –Ї Vdd –Є Vss

–Ю–њ–µ—А–∞—Ж–Є—П —З—В–µ–љ–Є—П –њ–Њ—А—В–∞

–Р —Б—З–Є—В—Л–≤–∞–µ—В —Б–Њ—Б—В–Њ—П–љ–Є–µ

–≤—Л–≤–Њ–і–Њ–≤ –њ–Њ—А—В–∞, –≤ —В–Њ –≤—А–µ–Љ—П –Ї–∞–Ї –Ј–∞–њ–Є—Б—М –≤ –љ–µ–≥–Њ

–Є–Ј–Љ–µ–љ—П–µ—В —Б–Њ—Б—В–Њ—П–љ–Є–µ —В—А–Є–≥–≥–µ—А–Њ–≤ –њ–Њ—А—В–∞. –Т—Б–µ –Њ–њ–µ—А–∞—Ж–Є–Є —Б –њ–Њ—А—В–Њ–Љ —П–≤–ї—П—О—В—Б—П –Њ–њ–µ—А–∞—Ж–Є—П–Љ–Є —В–Є–њ–∞

"—З—В–µ–љ–Є–µ-–Љ–Њ–і–Є—Д–Є–Ї–∞—Ж–Є—П-–Ј–∞–њ–Є—Б—М". –Я–Њ—Н—В–Њ–Љ—Г –Ј–∞–њ–Є—Б—М –≤ –њ–Њ—А—В

–њ—А–µ–і–њ–Њ–ї–∞–≥–∞–µ—В, —З—В–Њ —Б–Њ—Б—В–Њ—П–љ–Є–µ –≤—Л–≤–Њ–і–Њ–≤ –њ–Њ—А—В–∞ –≤–љ–∞—З–∞–ї–µ

—Б—З–Є—В—Л–≤–∞–µ—В—Б—П, –Ј–∞—В–µ–Љ –Љ–Њ–і–Є—Д–Є—Ж–Є—А—Г–µ—В—Б—П –Є –Ј–∞–њ–Є—Б—Л–≤–∞–µ—В—Б—П –≤ —В—А–Є–≥–≥–µ—А-—Д–Є–Ї—Б–∞—В–Њ—А. –Т—Л–≤–Њ–і RA4 –Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Є—А–Њ–≤–∞–љ —Б —В–∞–Ї—В–Њ–≤—Л–Љ –≤—Е–Њ–і–Њ–Љ —В–∞–є–Љ–µ—А–∞

TMR0. –°—Е–µ–Љ–∞ –ї–Є–љ–Є–Є RA4 –њ–Њ—А—В–∞ –Р –њ—А–Є–≤–µ–і–µ–љ–∞ –љ–∞ —А–Є—Б. 9.

–Я–Њ—А—В –Т (PORTB) вАУ —Н—В–Њ –і–≤—Г–љ–∞–њ—А–∞–≤–ї–µ–љ–љ—Л–є 8-–±–Є—В–Њ–≤—Л–є –њ–Њ—А—В,

—Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–Є–є –≤—Л–≤–Њ–і–∞–Љ RB<7:0> –Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –Є —А–∞—Б–њ–Њ–ї–Њ–ґ–µ–љ–љ—Л–є –њ–Њ –∞–і—А–µ—Б—Г 06h. –Ю—В–љ–Њ—Б—П—Й–Є–є—Б—П –Ї –њ–Њ—А—В—Г –Т —Г–њ—А–∞–≤–ї—П—О—Й–Є–є

—А–µ–≥–Є—Б—В—А TRISB —А–∞—Б–њ–Њ–ї–Њ–ґ–µ–љ –љ–∞ –њ–µ—А–≤–Њ–є —Б—В—А–∞–љ–Є—Ж–µ —А–µ–≥–Є—Б—В—А–Њ–≤

–њ–Њ –∞–і—А–µ—Б—Г 86h. –Х—Б–ї–Є –±–Є—В —Г–њ—А–∞–≤–ї—П—О—Й–µ–≥–Њ TRISB —А–µ–≥–Є—Б—В—А–∞ –Є–Љ–µ–µ—В –Ј–љ–∞—З–µ–љ–Є–µ

1, —В–Њ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–∞—П –ї–Є–љ–Є—П –±—Г–і–µ—В —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞—В—М—Б—П –љ–∞ –≤–≤–Њ–і. –Э–Њ–ї—М –њ–µ—А–µ–Ї–ї—О—З–∞–µ—В

–ї–Є–љ–Є—О –љ–∞ –≤—Л–≤–Њ–і –Є –Њ–і–љ–Њ–≤—А–µ–Љ–µ–љ–љ–Њ –≤—Л–≤–Њ–і–Є—В –љ–∞ –љ–µ–µ —Б–Њ–і–µ—А–ґ–Є–Љ–Њ–µ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–µ–≥–Њ —А–µ–≥–Є—Б—В—А–∞ –Ј–∞—Й–µ–ї–Ї–Є. –Я—А–Є –≤–Ї–ї—О—З–µ–љ–Є–Є –њ–Є—В–∞–љ–Є—П –≤—Б–µ –ї–Є–љ–Є–Є –њ–Њ—А—В–∞ –њ–Њ —Г–Љ–Њ–ї—З–∞–љ–Є—О –љ–∞—Б—В—А–Њ–µ–љ—Л –љ–∞ –≤–≤–Њ–і.

–†–Є—Б. 9. –°—Е–µ–Љ–∞ –ї–Є–љ–Є–Є RA4 –њ–Њ—А—В–∞ –Р. –Т—Л–≤–Њ–і –њ–Њ—А—В–∞ –Є–Љ–µ–µ—В –Ј–∞—Й–Є—В–љ—Л–є –і–Є–Њ–і

—В–Њ–ї—М–Ї–Њ –Ї Vss

–£ –Ї–∞–ґ–і–Њ–є –љ–Њ–ґ–Ї–Є –њ–Њ—А—В–∞

–Т –Є–Љ–µ–µ—В—Б—П –љ–µ–±–Њ–ї—М—И–∞—П

–∞–Ї—В–Є–≤–љ–∞—П –љ–∞–≥—А—Г–Ј–Ї–∞ (–Њ–Ї–Њ–ї–Њ 100–Љ–Ї–Р) –љ–∞ –ї–Є–љ–Є—О –њ–Є—В–∞–љ–Є—П (pull-up). –Ю–љ–∞ –∞–≤—В–Њ–Љ–∞—В–Є—З–µ—Б–Ї–Є

–Њ—В–Ї–ї—О—З–∞–µ—В—Б—П, –µ—Б–ї–Є —Н—В–∞ –љ–Њ–ґ–Ї–∞ –Ј–∞–њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–∞ –Ї–∞–Ї –≤—Л–≤–Њ–і. –С–Њ–ї–µ–µ —В–Њ–≥–Њ,

—Г–њ—А–∞–≤–ї—П—О—Й–Є–є –±–Є—В /RBPU —А–µ–≥–Є—Б—В—А–∞ OPTION<7> –Љ–Њ–ґ–µ—В –Њ—В–Ї–ї—О—З–Є—В—М (–њ—А–Є RBPU=1) –≤—Б–µ –љ–∞–≥—А—Г–Ј–Ї–Є. –°–±—А–Њ—Б –њ—А–Є –≤–Ї–ї—О—З–µ–љ–Є–Є –њ–Є—В–∞–љ–Є—П —В–∞–Ї–ґ–µ –Њ—В–Ї–ї—О—З–∞–µ—В

–≤—Б–µ –љ–∞–≥—А—Г–Ј–Ї–Є.

–І–µ—В—Л—А–µ –ї–Є–љ–Є–Є –њ–Њ—А—В–∞

–Т (RB<7:4>) –Љ–Њ–≥—Г—В –≤—Л–Ј–≤–∞—В—М –њ—А–µ—А—Л–≤–∞–љ–Є–µ –њ—А–Є

–Є–Ј–Љ–µ–љ–µ–љ–Є–Є –Ј–љ–∞—З–µ–љ–Є—П —Б–Є–≥–љ–∞–ї–∞ –љ–∞ –ї—О–±–Њ–є –Є–Ј –љ–Є—Е. –Х—Б–ї–Є —Н—В–Є –ї–Є–љ–Є–Є –љ–∞—Б—В—А–Њ–µ–љ—Л –љ–∞ –≤–≤–Њ–і,

—В–Њ –Њ–љ–Є –Њ–њ—А–∞—И–Є–≤–∞—О—В—Б—П –Є –Ј–∞—Й–µ–ї–Ї–Є–≤–∞—О—В—Б—П –≤ —Ж–Є–Ї–ї–µ —З—В–µ–љ–Є—П Q1. –Э–Њ–≤–∞—П –≤–µ–ї–Є—З–Є–љ–∞ –≤—Е–Њ–і–љ–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ —Б—А–∞–≤–љ–Є–≤–∞–µ—В—Б—П —Б–Њ —Б—В–∞—А–Њ–є –≤

–Ї–∞–ґ–і–Њ–Љ –Ї–Њ–Љ–∞–љ–і–љ–Њ–Љ —Ж–Є–Ї–ї–µ. –Я—А–Є –љ–µ—Б–Њ–≤–њ–∞–і–µ–љ–Є–Є –Ј–љ–∞—З–µ–љ–Є—П —Б–Є–≥–љ–∞–ї–∞ –љ–∞ –љ–Њ–ґ–Ї–µ –Є –≤ —Д–Є–Ї—Б–∞—В–Њ—А–µ

–≥–µ–љ–µ—А–Є—А—Г–µ—В—Б—П –≤—Л—Б–Њ–Ї–Є–є —Г—А–Њ–≤–µ–љ—М. –Т—Л—Е–Њ–і—Л –і–µ—В–µ–Ї—В–Њ—А–Њ–≤ "–љ–µ—Б–Њ–≤–њ–∞–і–µ–љ–Є–є" RB4, RB5, RB6, RB7 –Њ–±—К–µ–і–Є–љ—П—О—В—Б—П –њ–Њ –Ш–Ы–Ш –Є

–≥–µ–љ–µ—А–Є—А—Г—О—В –њ—А–µ—А—Л–≤–∞–љ–Є–µ RBIF (–Ј–∞–њ–Њ–Љ–Є–љ–∞–µ–Љ–Њ–µ –≤ —А–µ–≥–Є—Б—В—А–µ INTCON<0>). –Ы—О–±–∞—П –ї–Є–љ–Є—П, –љ–∞—Б—В—А–Њ–µ–љ–љ–∞—П –Ї–∞–Ї –≤—Л–≤–Њ–і, –≤ —Н—В–Њ–Љ —Б—А–∞–≤–љ–µ–љ–Є–Є –љ–µ

—Г—З–∞—Б—В–≤—Г–µ—В. –Я—А–µ—А—Л–≤–∞–љ–Є–µ –Љ–Њ–ґ–µ—В –≤—Л–≤–µ—Б—В–Є –Ї—А–Є—Б—В–∞–ї–ї –Є–Ј

—А–µ–ґ–Є–Љ–∞ SLEEP. –Т –њ–Њ–і–њ—А–Њ–≥—А–∞–Љ–Љ–µ –Њ–±—А–∞–±–Њ—В–Ї–Є

–њ—А–µ—А—Л–≤–∞–љ–Є—П —Б–ї–µ–і—Г–µ—В —Б–±—А–Њ—Б–Є—В—М –Ј–∞–њ—А–Њ—Б –њ—А–µ—А—Л–≤–∞–љ–Є—П –Њ–і–љ–Є–Љ –Є–Ј —Б–ї–µ–і—Г—О—Й–Є—Е —Б–њ–Њ—Б–Њ–±–Њ–≤:

¬Ј

–њ—А–Њ—З–Є—В–∞—В—М (–Є–ї–Є –Ј–∞–њ–Є—Б–∞—В—М –≤) –њ–Њ—А—В

–Т. –≠—В–Њ –Ј–∞–≤–µ—А—И–Є—В —Б–Њ—Б—В–Њ—П–љ–Є–µ —Б—А–∞–≤–љ–µ–љ–Є—П;

¬Ј

–Њ–±–љ—Г–ї–Є—В—М –±–Є—В RBIF

—А–µ–≥–Є—Б—В—А–∞ INTCON<0>.

–Я—А–Є —Н—В–Њ–Љ –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ –Є–Љ–µ—В—М –≤ –≤–Є–і—Г, —З—В–Њ

—Г—Б–ї–Њ–≤–Є–µ "–љ–µ—Б–Њ–≤–њ–∞–і–µ–љ–Є—П" –±—Г–і–µ—В –њ—А–Њ–і–Њ–ї–ґ–∞—В—М —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞—В—М –њ—А–Є–Ј–љ–∞–Ї RBIF. –Ґ–Њ–ї—М–Ї–Њ —З—В–µ–љ–Є–µ –њ–Њ—А—В–∞ –Т –Љ–Њ–ґ–µ—В —Г—Б—В—А–∞–љ–Є—В—М "–љ–µ—Б–Њ–≤–њ–∞–і–µ–љ–Є–µ" –Є –њ–Њ–Ј–≤–Њ–ї–Є—В –Њ–±–љ—Г–ї–Є—В—М

–±–Є—В RBIF.

–Я—А–µ—А—Л–≤–∞–љ–Є–µ –њ–Њ –љ–µ—Б–Њ–≤–њ–∞–і–µ–љ–Є—О –Є –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞–µ–Љ—Л–µ –≤–љ—Г—В—А–µ–љ–љ–Є–µ

–∞–Ї—В–Є–≤–љ—Л–µ –љ–∞–≥—А—Г–Ј–Ї–Є –љ–∞ —Н—В–Є—Е —З–µ—В—Л—А–µ—Е –ї–Є–љ–Є—П—Е –Љ–Њ–≥—Г—В –Њ–±–µ—Б–њ–µ—З–Є—В—М –њ—А–Њ—Б—В–Њ–є –Є–љ—В–µ—А—Д–µ–є—Б,

–љ–∞–њ—А–Є–Љ–µ—А, —Б –Ї–ї–∞–≤–Є–∞—В—Г—А–Њ–є, —Б –≤—Л—Е–Њ–і–Њ–Љ –Є–Ј —А–µ–ґ–Є–Љ–∞ SLEEP –њ–Њ –љ–∞–ґ–∞—В–Є—О –Ї–ї–∞–≤–Є—И.

–°—Е–µ–Љ—Л –ї–Є–љ–Є–є –њ–Њ—А—В–∞

B –њ—А–Є–≤–µ–і–µ–љ—Л –љ–∞ —А–Є—Б. 10 –Є 11.

–†–Є—Б. 10. –°—Е–µ–Љ–∞ –ї–Є–љ–Є–є RB <7:4 –њ–Њ—А—В–∞ B. –Т—Л–≤–Њ–і—Л –њ–Њ—А—В–∞ –Є–Љ–µ—О—В

–Ј–∞—Й–Є—В–љ—Л–µ –і–Є–Њ–і—Л –Ї Vdd –Є Vss

–†–Є—Б. 11. –°—Е–µ–Љ–∞ –ї–Є–љ–Є–є RB

<3:0 –њ–Њ—А—В–∞ B. –Т—Л–≤–Њ–і—Л –њ–Њ—А—В–∞ –Є–Љ–µ—О—В –Ј–∞—Й–Є—В–љ—Л–µ –і–Є–Њ–і—Л –Ї Vdd –Є Vss

–Я—А–Є –Њ—А–≥–∞–љ–Є–Ј–∞—Ж–Є–Є –і–≤—Г–љ–∞–њ—А–∞–≤–ї–µ–љ–љ—Л—Е –њ–Њ—А—В–Њ–≤ –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ —Г—З–Є—В—Л–≤–∞—В—М –Њ—Б–Њ–±–µ–љ–љ–Њ—Б—В–Є –Њ—А–≥–∞–љ–Є–Ј–∞—Ж–Є–Є

–≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞ –і–∞–љ–љ—Л—Е –Ь–Ъ. –Ы—О–±–∞—П –Ї–Њ–Љ–∞–љ–і–∞, –Ї–Њ—В–Њ—А–∞—П –Њ—Б—Г—Й–µ—Б—В–≤–ї—П–µ—В –Ј–∞–њ–Є—Б—М, –≤—Л–њ–Њ–ї–љ—П–µ—В

–µ–µ –≤–љ—Г—В—А–Є –Ї–∞–Ї "—З—В–µ–љ–Є–µ-–Љ–Њ–і–Є—Д–Є–Ї–∞—Ж–Є—П-–Ј–∞–њ–Є—Б—М". –Э–∞–њ—А–Є–Љ–µ—А, –Ї–Њ–Љ–∞–љ–і—Л BCF –Є BSF —Б—З–Є—В—Л–≤–∞—О—В –њ–Њ—А—В —Ж–µ–ї–Є–Ї–Њ–Љ, –Љ–Њ–і–Є—Д–Є—Ж–Є—А—Г—О—В –Њ–і–Є–љ –±–Є—В –Є –≤—Л–≤–Њ–і—П—В —А–µ–Ј—Г–ї—М—В–∞—В

–Њ–±—А–∞—В–љ–Њ. –Ч–і–µ—Б—М –љ–µ–Њ–±—Е–Њ–і–Є–Љ–∞ –Њ—Б—В–Њ—А–Њ–ґ–љ–Њ—Б—В—М. –Т —З–∞—Б—В–љ–Њ—Б—В–Є, –Ї–Њ–Љ–∞–љ–і–∞ BSF

PORTB, 5 (—Г—Б—В–∞–љ–Њ–≤–Є—В—М –≤ –µ–і–Є–љ–Є—Ж—Г –±–Є—В 5 –њ–Њ—А—В–∞ B) —Б–љ–∞—З–∞–ї–∞ —Б—З–Є—В—Л–≤–∞–µ—В –≤—Б–µ —А–µ–∞–ї—М–љ—Л–µ –Ј–љ–∞—З–µ–љ–Є—П —Б–Є–≥–љ–∞–ї–Њ–≤, –њ—А–Є—Б—Г—В—Б—В–≤—Г—О—Й–Є–µ

–≤ –і–∞–љ–љ—Л–є –Љ–Њ–Љ–µ–љ—В –љ–∞ –≤—Л–≤–Њ–і–∞—Е –њ–Њ—А—В–∞. –Ч–∞—В–µ–Љ –≤—Л–њ–Њ–ї–љ—П—О—В—Б—П

–і–µ–є—Б—В–≤–Є—П –љ–∞–і –±–Є—В–Њ–Љ 5, –Є –љ–Њ–≤–Њ–µ –Ј–љ–∞—З–µ–љ–Є–µ –±–∞–є—В–∞ —Ж–µ–ї–Є–Ї–Њ–Љ –Ј–∞–њ–Є—Б—Л–≤–∞–µ—В—Б—П –≤ –≤—Л—Е–Њ–і–љ—Л–µ —Д–Є–Ї—Б–∞—В–Њ—А—Л.

–Х—Б–ї–Є –і—А—Г–≥–Њ–є –±–Є—В —А–µ–≥–Є—Б—В—А–∞ PORTB –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –≤ –Ї–∞—З–µ—Б—В–≤–µ –і–≤—Г–љ–∞–њ—А–∞–≤–ї–µ–љ–љ–Њ–≥–Њ –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞ (—Б–Ї–∞–ґ–µ–Љ,

–±–Є—В 0), –Є –≤ –і–∞–љ–љ—Л–є –Љ–Њ–Љ–µ–љ—В –Њ–љ –Њ–њ—А–µ–і–µ–ї–µ–љ –Ї–∞–Ї –≤—Е–Њ–і–љ–Њ–є, —В–Њ –≤—Е–Њ–і–љ–Њ–є —Б–Є–≥–љ–∞–ї –љ–∞ —Н—В–Њ–Љ

–≤—Л–≤–Њ–і–µ –±—Г–і–µ—В —Б—З–Є—В–∞–љ –Є –Ј–∞–њ–Є—Б–∞–љ –Њ–±—А–∞—В–љ–Њ –≤ –≤—Л—Е–Њ–і–љ–Њ–є —В—А–Є–≥–≥–µ—А-—Д–Є–Ї—Б–∞—В–Њ—А —Н—В–Њ–≥–Њ –ґ–µ

–≤—Л–≤–Њ–і–∞, —Б—В–Є—А–∞—П –њ—А–µ–і—Л–і—Г—Й–µ–µ —Б–Њ—Б—В–Њ—П–љ–Є–µ. –Ф–Њ —В–µ—Е –њ–Њ—А, –њ–Њ–Ї–∞ —Н—В–∞ –љ–Њ–ґ–Ї–∞ –Њ—Б—В–∞–µ—В—Б—П –≤

—А–µ–ґ–Є–Љ–µ –≤–≤–Њ–і–∞, –љ–Є–Ї–∞–Ї–Є—Е –њ—А–Њ–±–ї–µ–Љ –љ–µ –≤–Њ–Ј–љ–Є–Ї–∞–µ—В. –Ю–і–љ–∞–Ї–Њ –µ—Б–ї–Є –њ–Њ–Ј–і–љ–µ–µ –ї–Є–љ–Є—П 0 –њ–µ—А–µ–Ї–ї—О—З–Є—В—Б—П

–≤ —А–µ–ґ–Є–Љ –≤—Л–≤–Њ–і–∞, –µ–µ —Б–Њ—Б—В–Њ—П–љ–Є–µ –±—Г–і–µ—В –љ–µ–Њ–њ—А–µ–і–µ–ї–µ–љ–љ—Л–Љ.

–Э–∞ –љ–Њ–ґ–Ї—Г, —А–∞–±–Њ—В–∞—О—Й—Г—О –≤ —А–µ–ґ–Є–Љ–µ –≤—Л–≤–Њ–і–∞, –љ–µ

–і–Њ–ї–ґ–љ—Л –љ–∞–≥—А—Г–ґ–∞—В—М—Б—П –≤–љ–µ—И–љ–Є–µ –Є—Б—В–Њ—З–љ–Є–Ї–Є —В–Њ–Ї–Њ–≤ ("–Љ–Њ–љ—В–∞–ґ–љ–Њ–µ –Ш",

"–Љ–Њ–љ—В–∞–ґ–љ–Њ–µ –Ш–Ы–Ш"). –С–Њ–ї—М—И–Є–µ —А–µ–Ј—Г–ї—М—В–Є—А—Г—О—Й–Є–µ —В–Њ–Ї–Є –Љ–Њ–≥—Г—В –њ–Њ–≤—А–µ–і–Є—В—М

–Ї—А–Є—Б—В–∞–ї–ї.

–Э–µ–Њ–±—Е–Њ–і–Є–Љ–Њ –≤—Л–і–µ—А–ґ–Є–≤–∞—В—М –Њ–њ—А–µ–і–µ–ї–µ–љ–љ—Г—О

–њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ—Б—В—М –Њ–±—А–∞—Й–µ–љ–Є—П –Ї –њ–Њ—А—В–∞–Љ –≤–≤–Њ–і–∞/–≤—Л–≤–Њ–і–∞.

–Ч–∞–њ–Є—Б—М –≤ –њ–Њ—А—В –≤—Л–≤–Њ–і–∞ –њ—А–Њ–Є—Б—Е–Њ–і–Є—В –≤ –Ї–Њ–љ—Ж–µ –Ї–Њ–Љ–∞–љ–і–љ–Њ–≥–Њ

—Ж–Є–Ї–ї–∞. –Э–Њ –њ—А–Є —З—В–µ–љ–Є–Є –і–∞–љ–љ—Л–µ –і–Њ–ї–ґ–љ—Л –±—Л—В—М —Б—В–∞–±–Є–ї—М–љ—Л –≤ –љ–∞—З–∞–ї–µ –Ї–Њ–Љ–∞–љ–і–љ–Њ–≥–Њ —Ж–Є–Ї–ї–∞.

–С—Г–і—М—В–µ –≤–љ–Є–Љ–∞—В–µ–ї—М–љ—Л –≤ –Њ–њ–µ—А–∞—Ж–Є—П—Е —З—В–µ–љ–Є—П, —Б–ї–µ–і—Г—О—Й–Є—Е —Б—А–∞–Ј—Г –Ј–∞ –Ј–∞–њ–Є—Б—М—О –≤ —В–Њ—В –ґ–µ –њ–Њ—А—В. –Ч–і–µ—Б—М –љ–∞–і–Њ —Г—З–Є—В—Л–≤–∞—В—М –Є–љ–µ—А—Ж–Є–Њ–љ–љ–Њ—Б—В—М —Г—Б—В–∞–љ–Њ–≤–ї–µ–љ–Є—П

–љ–∞–њ—А—П–ґ–µ–љ–Є—П –љ–∞ –≤—Л–≤–Њ–і–∞—Е. –Ь–Њ–ґ–µ—В –њ–Њ—В—А–µ–±–Њ–≤–∞—В—М—Б—П –њ—А–Њ–≥—А–∞–Љ–Љ–љ–∞—П –Ј–∞–і–µ—А–ґ–Ї–∞, —З—В–Њ–±—Л

–љ–∞–њ—А—П–ґ–µ–љ–Є–µ –љ–∞ –љ–Њ–ґ–Ї–µ (–Ї–Њ—В–Њ—А–Њ–µ –Ј–∞–≤–Є—Б–Є—В –Њ—В –љ–∞–≥—А—Г–Ј–Ї–Є) —Г—Б–њ–µ–ї–Њ —Б—В–∞–±–Є–ї–Є–Ј–Є—А–Њ–≤–∞—В—М—Б—П –і–Њ

–љ–∞—З–∞–ї–∞ –Є—Б–њ–Њ–ї–љ–µ–љ–Є—П —Б–ї–µ–і—Г—О—Й–µ–є –Ї–Њ–Љ–∞–љ–і—Л —З—В–µ–љ–Є—П.

10. –Ь–Њ–і—Г–ї—М —В–∞–є–Љ–µ—А–∞ –Є —А–µ–≥–Є—Б—В—А —В–∞–є–Љ–µ—А–∞

–°—В—А—Г–Ї—В—Г—А–∞ –Љ–Њ–і—Г–ї—П —В–∞–є–Љ–µ—А–∞/—Б—З–µ—В—З–Є–Ї–∞ TIMER0 –Є –µ–≥–Њ –≤–Ј–∞–Є–Љ–Њ—Б–≤—П–Ј—М —Б —А–µ–≥–Є—Б—В—А–∞–Љ–Є

TMR0 –Є OPTION –њ–Њ–Ї–∞–Ј–∞–љ—Л –љ–∞ —А–Є—Б. 12. TIMER0 —П–≤–ї—П–µ—В—Б—П –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ–Љ—Л–Љ –Љ–Њ–і—Г–ї–µ–Љ –Є —Б–Њ–і–µ—А–ґ–Є—В —Б–ї–µ–і—Г—О—Й–Є–µ

–Ї–Њ–Љ–њ–Њ–љ–µ–љ—В—Л:

¬Ј

8-—А–∞–Ј—А—П–і–љ—Л–є —В–∞–є–Љ–µ—А/—Б—З–µ—В—З–Є–Ї

TMR0 —Б

–≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В—М—О —З—В–µ–љ–Є—П –Є –Ј–∞–њ–Є—Б–Є –Ї–∞–Ї —А–µ–≥–Є—Б—В—А;

¬Ј

8-—А–∞–Ј—А—П–і–љ—Л–є –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ —Г–њ—А–∞–≤–ї—П–µ–Љ—Л–є

–њ—А–µ–і–≤–∞—А–Є—В–µ–ї—М–љ—Л–є –і–µ–ї–Є—В–µ–ї—М (–њ—А–µ–і–і–µ–ї–Є—В–µ–ї—М);

¬Ј

–Љ—Г–ї—М—В–Є–њ–ї–µ–Ї—Б–Њ—А –≤—Е–Њ–і–љ–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ –і–ї—П –≤—Л–±–Њ—А–∞

–≤–љ—Г—В—А–µ–љ–љ–µ–≥–Њ –Є–ї–Є –≤–љ–µ—И–љ–µ–≥–Њ —В–∞–Ї—В–Њ–≤–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞;

¬Ј

—Б—Е–µ–Љ—Г –≤—Л–±–Њ—А–∞ —Д—А–Њ–љ—В–∞ –≤–љ–µ—И–љ–µ–≥–Њ —В–∞–Ї—В–Њ–≤–Њ–≥–Њ —Б–Є–≥–љ–∞–ї–∞;

¬Ј

—Д–Њ—А–Љ–Є—А–Њ–≤–∞—В–µ–ї—М –Ј–∞–њ—А–Њ—Б–∞ –њ—А–µ—А—Л–≤–∞–љ–Є—П

–њ–Њ –њ–µ—А–µ–њ–Њ–ї–љ–µ–љ–Є—О —А–µ–≥–Є—Б—В—А–∞ TMR0 —Б FFh –і–Њ 00h.

–†–µ–ґ–Є–Љ —В–∞–є–Љ–µ—А–∞

–≤—Л–±–Є—А–∞–µ—В—Б—П –њ—Г—В–µ–Љ —Б–±—А–∞—Б—Л–≤–∞–љ–Є—П –≤ –љ–Њ–ї—М –±–Є—В–∞ T0CS —А–µ–≥–Є—Б—В—А–∞ OPTION

<5>. –Т —А–µ–ґ–Є–Љ–µ —В–∞–є–Љ–µ—А–∞ TMR0 –Є–љ–Ї—А–µ–Љ–µ–љ—В–Є—А—Г–µ—В—Б—П –Ї–∞–ґ–і—Л–є –Ї–Њ–Љ–∞–љ–і–љ—Л–є —Ж–Є–Ї–ї (–±–µ–Ј –њ—А–µ–і–µ–ї–Є—В–µ–ї—П).

–Я–Њ—Б–ї–µ –Ј–∞–њ–Є—Б–Є –Є–љ—Д–Њ—А–Љ–∞—Ж–Є–Є –≤ TMR0 –Є–љ–Ї—А–µ–Љ–µ–љ—В–Є—А–Њ–≤–∞–љ–Є–µ

–µ–≥–Њ –љ–∞—З–љ–µ—В—Б—П –њ–Њ—Б–ї–µ –і–≤—Г—Е –Ї–Њ–Љ–∞–љ–і–љ—Л—Е —Ж–Є–Ї–ї–Њ–≤. –≠—В–Њ –њ—А–Њ–Є—Б—Е–Њ–і–Є—В —Б–Њ –≤—Б–µ–Љ–Є –Ї–Њ–Љ–∞–љ–і–∞–Љ–Є,

–Ї–Њ—В–Њ—А—Л–µ –њ—А–Њ–Є–Ј–≤–Њ–і—П—В –Ј–∞–њ–Є—Б—М –Є–ї–Є —З—В–µ–љ–Є–µ-–Љ–Њ–і–Є—Д–Є–Ї–∞—Ж–Є—О-–Ј–∞–њ–Є—Б—М TMR0 (–љ–∞–њ—А–Є–Љ–µ—А, MOVF TMR0, CLRF TMR0). –Ш–Ј–±–µ–ґ–∞—В—М

—Н—В–Њ–≥–Њ –Љ–Њ–ґ–љ–Њ –њ—А–Є –њ–Њ–Љ–Њ—Й–Є –Ј–∞–њ–Є—Б–Є –≤ TMR0 —Б–Ї–Њ—А—А–µ–Ї—В–Є—А–Њ–≤–∞–љ–љ–Њ–≥–Њ –Ј–љ–∞—З–µ–љ–Є—П. –Х—Б–ї–Є TMR0 –љ—Г–ґ–љ–Њ –њ—А–Њ–≤–µ—А–Є—В—М –љ–∞ —А–∞–≤–µ–љ—Б—В–≤–Њ –љ—Г–ї—О –±–µ–Ј –Њ—Б—В–∞–љ–Њ–≤–∞ —Б—З–µ—В–∞,

—Б–ї–µ–і—Г–µ—В –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М –Є–љ—Б—В—А—Г–Ї—Ж–Є—О MOVF TMR0,W.

–†–µ–ґ–Є–Љ —Б—З–µ—В—З–Є–Ї–∞ –≤—Л–±–Є—А–∞–µ—В—Б—П –њ—Г—В–µ–Љ —Г—Б—В–∞–љ–Њ–≤–Ї–Є –≤

–µ–і–Є–љ–Є—Ж—Г –±–Є—В–∞ T0CS —А–µ–≥–Є—Б—В—А–∞ OPTION<5>. –Т —Н—В–Њ–Љ —А–µ–ґ–Є–Љ–µ —А–µ–≥–Є—Б—В—А TMR0 –±—Г–і–µ—В –Є–љ–Ї—А–µ–Љ–µ–љ—В–Є—А–Њ–≤–∞—В—М—Б—П –ї–Є–±–Њ –љ–∞—А–∞—Б—В–∞—О—Й–Є–Љ, –ї–Є–±–Њ —Б–њ–∞–і–∞—О—Й–Є–Љ

—Д—А–Њ–љ—В–Њ–Љ –љ–∞ –≤—Л–≤–Њ–і–µ RA4/T0CKI –Њ—В –≤–љ–µ—И–љ–Є—Е

—Б–Њ–±—Л—В–Є–є. –Э–∞–њ—А–∞–≤–ї–µ–љ–Є–µ —Д—А–Њ–љ—В–∞ –Њ–њ—А–µ–і–µ–ї—П–µ—В—Б—П —Г–њ—А–∞–≤–ї—П—О—Й–Є–Љ –±–Є—В–Њ–Љ T0SE –≤ —А–µ–≥–Є—Б—В—А–µ OPTION<4>. –Я—А–Є T0SE = 0 –±—Г–і–µ—В

–≤—Л–±—А–∞–љ –љ–∞—А–∞—Б—В–∞—О—Й–Є–є —Д—А–Њ–љ—В.

–Я—А–µ–і–і–µ–ї–Є—В–µ–ї—М –Љ–Њ–ґ–µ—В –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М—Б—П –Є–ї–Є

—Б–Њ–≤–Љ–µ—Б—В–љ–Њ —Б TMR0, –Є–ї–Є —Б–Њ —Б—В–Њ—А–Њ–ґ–µ–≤—Л–Љ

(Watchdog) —В–∞–є–Љ–µ—А–Њ–Љ. –Т–∞—А–Є–∞–љ—В –њ–Њ–і–Ї–ї—О—З–µ–љ–Є—П –і–µ–ї–Є—В–µ–ї—П

–Ї–Њ–љ—В—А–Њ–ї–Є—А—Г–µ—В—Б—П –±–Є—В–Њ–Љ PSA —А–µ–≥–Є—Б—В—А–∞ OPTION<3>. –Я—А–Є PSA=0 –і–µ–ї–Є—В–µ–ї—М

–±—Г–і–µ—В –њ–Њ–і—Б–Њ–µ–і–Є–љ–µ–љ –Ї TMR0. –°–Њ–і–µ—А–ґ–Є–Љ–Њ–µ –і–µ–ї–Є—В–µ–ї—П

–њ—А–Њ–≥—А–∞–Љ–Љ–µ –љ–µ–і–Њ—Б—В—Г–њ–љ–Њ. –Ъ–Њ—Н—Д—Д–Є—Ж–Є–µ–љ—В –і–µ–ї–µ–љ–Є—П –њ—А–µ–і–µ–ї–Є—В–µ–ї—П –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А—Г–µ—В—Б—П –±–Є—В–∞–Љ–Є PS2вА¶PS0 —А–µ–≥–Є—Б—В—А–∞ OPTION<2:0>.

–†–Є—Б. 12. –°—В—А—Г–Ї—В—Г—А–љ–∞—П —Б—Е–µ–Љ–∞

—В–∞–є–Љ–µ—А–∞/—Б—З–µ—В—З–Є–Ї–∞ TMR0

–Я—А–µ—А—Л–≤–∞–љ–Є–µ –њ–Њ TMR0 –≤—Л—А–∞–±–∞—В—Л–≤–∞–µ—В—Б—П —В–Њ–≥–і–∞,

–Ї–Њ–≥–і–∞ –њ—А–Њ–Є—Б—Е–Њ–і–Є—В –њ–µ—А–µ–њ–Њ–ї–љ–µ–љ–Є–µ —А–µ–≥–Є—Б—В—А–∞ —В–∞–є–Љ–µ—А–∞/—Б—З–µ—В—З–Є–Ї–∞ –њ—А–Є –њ–µ—А–µ—Е–Њ–і–µ –Њ—В FFh –Ї 00h. –Ґ–Њ–≥–і–∞ —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞–µ—В—Б—П

–±–Є—В –Ј–∞–њ—А–Њ—Б–∞ T0IF –≤ —А–µ–≥–Є—Б—В—А–µ

INTCON<2>. –Ф–∞–љ–љ–Њ–µ –њ—А–µ—А—Л–≤–∞–љ–Є–µ –Љ–Њ–ґ–љ–Њ –Ј–∞–Љ–∞—Б–Ї–Є—А–Њ–≤–∞—В—М –±–Є—В–Њ–Љ T0IE –≤ —А–µ–≥–Є—Б—В—А–µ INTCON<5>. –С–Є—В –Ј–∞–њ—А–Њ—Б–∞ T0IF –і–Њ–ї–ґ–µ–љ –±—Л—В—М —Б–±—А–Њ—И–µ–љ –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ –њ—А–Є –Њ–±—А–∞–±–Њ—В–Ї–µ –њ—А–µ—А—Л–≤–∞–љ–Є—П. –Я—А–µ—А—Л–≤–∞–љ–Є–µ –њ–Њ TMR0 –љ–µ –Љ–Њ–ґ–µ—В –≤—Л–≤–µ—Б—В–Є –њ—А–Њ—Ж–µ—Б—Б–Њ—А –Є–Ј —А–µ–ґ–Є–Љ–∞ SLEEP –њ–Њ—В–Њ–Љ—Г, —З—В–Њ —В–∞–є–Љ–µ—А –≤ —Н—В–Њ–Љ —А–µ–ґ–Є–Љ–µ

–љ–µ —Д—Г–љ–Ї—Ж–Є–Њ–љ–Є—А—Г–µ—В.

–Я—А–Є PSA=1 –і–µ–ї–Є—В–µ–ї—М –±—Г–і–µ—В –њ–Њ–і—Б–Њ–µ–і–Є–љ–µ–љ –Ї —Б—В–Њ—А–Њ–ґ–µ–≤–Њ–Љ—Г —В–∞–є–Љ–µ—А—Г –Ї–∞–Ї –њ–Њ—Б—В–і–µ–ї–Є—В–µ–ї—М (–і–µ–ї–Є—В–µ–ї—М –љ–∞ –≤—Л—Е–Њ–і–µ). –Т–Њ–Ј–Љ–Њ–ґ–љ—Л–µ

–≤–∞—А–Є–∞–љ—В—Л –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є—П –њ—А–µ–і–µ–ї–Є—В–µ–ї—П –њ–Њ–Ї–∞–Ј–∞–љ—Л –љ–∞ —А–Є—Б. 13.

–Я—А–Є –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–Є –њ—А–µ–і–µ–ї–Є—В–µ–ї—П —Б–Њ–≤–Љ–µ—Б—В–љ–Њ —Б TMR0, –≤—Б–µ –Ї–Њ–Љ–∞–љ–і—Л, –Є–Ј–Љ–µ–љ—П—О—Й–Є–µ —Б–Њ–і–µ—А–ґ–Є–Љ–Њ–µ TMR0, –Њ–±–љ—Г–ї—П—О—В –њ—А–µ–і–і–µ–ї–Є—В–µ–ї—М. –Х—Б–ї–Є –њ—А–µ–і–і–µ–ї–Є—В–µ–ї—М –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П

—Б–Њ–≤–Љ–µ—Б—В–љ–Њ —Б WDT, –Ї–Њ–Љ–∞–љ–і–∞ CLRWDT –Њ–±–љ—Г–ї—П–µ—В —Б–Њ–і–µ—А–ґ–Є–Љ–Њ–µ –њ—А–µ–і–µ–ї–Є—В–µ–ї—П –≤–Љ–µ—Б—В–µ —Б WDT.

–Я—А–Є –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–Є –Љ–Њ–і—Г–ї—П TIMER0 –≤ —А–µ–ґ–Є–Љ–µ —Б—З–µ—В—З–Є–Ї–∞ –≤–љ–µ—И–љ–Є—Е —Б–Њ–±—Л—В–Є–є –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ —Г—З–Є—В—Л–≤–∞—В—М —В–Њ,

—З—В–Њ –≤–љ–µ—И–љ–Є–є —В–∞–Ї—В–Њ–≤—Л–є —Б–Є–≥–љ–∞–ї —Б–Є–љ—Е—А–Њ–љ–Є–Ј–Є—А—Г–µ—В—Б—П –≤–љ—Г—В—А–µ–љ–љ–µ–є —З–∞—Б—В–Њ—В–Њ–є Fosc. –≠—В–Њ

–њ—А–Є–≤–Њ–і–Є—В –Ї –њ–Њ—П–≤–ї–µ–љ–Є—О –Ј–∞–і–µ—А–ґ–Ї–Є –≤–Њ –≤—А–µ–Љ–µ–љ–Є —Д–∞–Ї—В–Є—З–µ—Б–Ї–Њ–≥–Њ –Є–љ–Ї—А–µ–Љ–µ–љ—В–Є—А–Њ–≤–∞–љ–Є—П

—Б–Њ–і–µ—А–ґ–Є–Љ–Њ–≥–Њ TMR0.

–°–Є–љ—Е—А–Њ–љ–Є–Ј–∞—Ж–Є—П –њ—А–Њ–Є—Б—Е–Њ–і–Є—В –њ–Њ –Њ–Ї–Њ–љ—З–∞–љ–Є–Є 2-–≥–Њ

–Є 4-–≥–Њ —В–∞–Ї—В–Њ–≤ —А–∞–±–Њ—В—Л –Ь–Ъ, –њ–Њ—Н—В–Њ–Љ—Г, –µ—Б–ї–Є –њ—А–µ–і–і–µ–ї–Є—В–µ–ї—М –љ–µ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П, —В–Њ –і–ї—П

—Д–Є–Ї—Б–∞—Ж–Є–Є –≤—Е–Њ–і–љ–Њ–≥–Њ —Б–Њ–±—Л—В–Є—П –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ, —З—В–Њ–±—Л –і–ї–Є—В–µ–ї—М–љ–Њ—Б—В–Є –≤—Л—Б–Њ–Ї–Њ–≥–Њ –Є –љ–Є–Ј–Ї–Њ–≥–Њ

—Б–Њ—Б—В–Њ—П–љ–Є–є —Б–Є–≥–љ–∞–ї–∞ –љ–∞ –≤—Е–Њ–і–µ RA4/T0CKI –±—Л–ї–Є

–±—Л –љ–µ –Љ–µ–љ–µ–µ 2 –њ–µ—А–Є–Њ–і–Њ–≤ —В–∞–Ї—В–Њ–≤–Њ–є —З–∞—Б—В–Њ—В—Л Tosc –њ–ї—О—Б –љ–µ–Ї–Њ—В–Њ—А–∞—П –Ј–∞–і–µ—А–ґ–Ї–∞ ( ~ 20

–љ—Б).

–Х—Б–ї–Є –Љ–Њ–і—Г–ї—М TIMER0 –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П —Б–Њ–≤–Љ–µ—Б—В–љ–Њ —Б –њ—А–µ–і–µ–ї–Є—В–µ–ї–µ–Љ, —В–Њ —З–∞—Б—В–Њ—В–∞ –≤—Е–Њ–і–љ–Њ–≥–Њ

—Б–Є–≥–љ–∞–ї–∞ –і–µ–ї–Є—В—Б—П –∞—Б–Є–љ—Е—А–Њ–љ–љ—Л–Љ —Б—З–µ—В—З–Є–Ї–Њ–Љ —В–∞–Ї, —З—В–Њ —Б–Є–≥–љ–∞–ї –љ–∞ –≤—Л—Е–Њ–і–µ –њ—А–µ–і–µ–ї–Є—В–µ–ї—П

—Б—В–∞–љ–Њ–≤–Є—В—Б—П —Б–Є–Љ–Љ–µ—В—А–Є—З–љ—Л–Љ. –Я—А–Є —Н—В–Њ–Љ –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ, —З—В–Њ–±—Л –і–ї–Є—В–µ–ї—М–љ–Њ—Б—В–Є –≤—Л—Б–Њ–Ї–Њ–≥–Њ –Є

–љ–Є–Ј–Ї–Њ–≥–Њ —Г—А–Њ–≤–љ–µ–є —Б–Є–≥–љ–∞–ї–∞ –љ–∞ –≤—Е–Њ–і–µ RA4/T0CKI –±—Л–ї–Є –±—Л –љ–µ –Љ–µ–љ–µ–µ 10 –љ—Б. –°–Є–љ—Е—А–Њ–љ–Є–Ј–∞—Ж–Є—П —Б–Є–≥–љ–∞–ї–∞ –њ—А–Њ–Є—Б—Е–Њ–і–Є—В –љ–∞

–≤—Л—Е–Њ–і–µ –њ—А–µ–і–µ–ї–Є—В–µ–ї—П, –њ–Њ—Н—В–Њ–Љ—Г —Б—Г—Й–µ—Б—В–≤—Г–µ—В –љ–µ–±–Њ–ї—М—И–∞—П –Ј–∞–і–µ—А–ґ–Ї–∞ –Љ–µ–ґ–і—Г —Д—А–Њ–љ—В–Њ–Љ

–≤–љ–µ—И–љ–µ–≥–Њ —Б–Є–≥–љ–∞–ї–∞ –Є –≤—А–µ–Љ–µ–љ–µ–Љ —Д–∞–Ї—В–Є—З–µ—Б–Ї–Њ–≥–Њ –Є–љ–Ї—А–µ–Љ–µ–љ—В–∞ —В–∞–є–Љ–µ—А–∞/—Б—З–µ—В—З–Є–Ї–∞.

–≠—В–∞ –Ј–∞–і–µ—А–ґ–Ї–∞ –љ–∞—Е–Њ–і–Є—В—Б—П –≤ –і–Є–∞–њ–∞–Ј–Њ–љ–µ –Њ—В 3 –і–Њ 7 –њ–µ—А–Є–Њ–і–Њ–≤ –Ї–Њ–ї–µ–±–∞–љ–Є–є —В–∞–Ї—В–Њ–≤–Њ–≥–Њ

–≥–µ–љ–µ—А–∞—В–Њ—А–∞. –Ґ–∞–Ї–Є–Љ –Њ–±—А–∞–Ј–Њ–Љ, –Є–Ј–Љ–µ—А–µ–љ–Є–µ –Є–љ—В–µ—А–≤–∞–ї–∞ –Љ–µ–ґ–і—Г —Б–Њ–±—Л—В–Є—П–Љ–Є –±—Г–і–µ—В –≤—Л–њ–Њ–ї–љ–µ–љ–Њ

—Б —В–Њ—З–љ–Њ—Б—В—М—О ¬±4 ¬Ј Tosc.

–†–Є—Б. 13. –°—В—А—Г–Ї—В—Г—А–∞ –Є –≤–Њ–Ј–Љ–Њ–ґ–љ—Л–µ –≤–∞—А–Є–∞–љ—В—Л –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є—П –њ—А–µ–і–µ–ї–Є—В–µ–ї—П

11. –Я–∞–Љ—П—В—М –і–∞–љ–љ—Л—Е –≤ –†–Я–Ч–£ (EEPROM)

–Ь–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А—Л –њ–Њ–і–≥—А—Г–њ–њ—Л PIC6F8X –Є–Љ–µ—О—В

—Н–љ–µ—А–≥–Њ–љ–µ–Ј–∞–≤–Є—Б–Є–Љ—Г—О –њ–∞–Љ—П—В—М –і–∞–љ–љ—Л—Е 64—Е8 EEPROM –±–Є—В, –Ї–Њ—В–Њ—А–∞—П –і–Њ–њ—Г—Б–Ї–∞–µ—В –Ј–∞–њ–Є—Б—М –Є —З—В–µ–љ–Є–µ –≤–Њ –≤—А–µ–Љ—П –љ–Њ—А–Љ–∞–ї—М–љ–Њ–є

—А–∞–±–Њ—В—Л (–≤–Њ –≤—Б–µ–Љ –і–Є–∞–њ–∞–Ј–Њ–љ–µ –њ–Є—В–∞—О—Й–Є—Е –љ–∞–њ—А—П–ґ–µ–љ–Є–є). –≠—В–∞ –њ–∞–Љ—П—В—М –љ–µ –њ—А–Є–љ–∞–і–ї–µ–ґ–Є—В

–Њ–±–ї–∞—Б—В–Є —А–µ–≥–Є—Б—В—А–Њ–≤–Њ–є –њ–∞–Љ—П—В–Є –Ю–Ч–£. –Ф–Њ—Б—В—Г–њ –Ї –љ–µ–є –Њ—Б—Г—Й–µ—Б—В–≤–ї—П–µ—В—Б—П –њ–Њ—Б—А–µ–і—Б—В–≤–Њ–Љ

–Ї–Њ—Б–≤–µ–љ–љ–Њ–є –∞–і—А–µ—Б–∞—Ж–Є–Є —З–µ—А–µ–Ј —А–µ–≥–Є—Б—В—А—Л

—Б–њ–µ—Ж–Є–∞–ї—М–љ—Л—Е —Д—Г–љ–Ї—Ж–Є–є: EEDATA <08h>, –Ї–Њ—В–Њ—А—Л–є

—Б–Њ–і–µ—А–ґ–Є—В 8-–±–Є—В–Њ–≤—Л–µ –і–∞–љ–љ—Л–µ –і–ї—П —З—В–µ–љ–Є—П/–Ј–∞–њ–Є—Б–Є –Є EEADR <09h>, –≤–Ї–ї—О—З–∞—О—Й–Є–є –∞–і—А–µ—Б —П—З–µ–є–Ї–Є, –Ї –Ї–Њ—В–Њ—А–Њ–є –Є–і–µ—В –Њ–±—А–∞—Й–µ–љ–Є–µ. –Ф–ї—П —Г–њ—А–∞–≤–ї–µ–љ–Є—П

–њ—А–Њ—Ж–µ—Б—Б–Њ–Љ —З—В–µ–љ–Є—П/–Ј–∞–њ–Є—Б–Є –Є—Б–њ–Њ–ї—М–Ј—Г—О—В—Б—П –і–≤–∞ —А–µ–≥–Є—Б—В—А–∞: EECON1

<88h> –Є EECON2

<89h>.

–Я—А–Є –Ј–∞–њ–Є—Б–Є –±–∞–є—В–∞ –∞–≤—В–Њ–Љ–∞—В–Є—З–µ—Б–Ї–Є —Б—В–Є—А–∞–µ—В—Б—П

–њ—А–µ–і—Л–і—Г—Й–µ–µ –Ј–љ–∞—З–µ–љ–Є–µ, –Є –Ј–∞–њ–Є—Б—Л–≤–∞—О—В—Б—П –љ–Њ–≤—Л–µ –і–∞–љ–љ—Л–µ (—Б—В–Є—А–∞–љ–Є–µ –њ–µ—А–µ–і –Ј–∞–њ–Є—Б—М—О). –Т—Б–µ

—Н—В–Є –Њ–њ–µ—А–∞—Ж–Є–Є –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В –≤—Б—В—А–Њ–µ–љ–љ—Л–є –∞–≤—В–Њ–Љ–∞—В –Ј–∞–њ–Є—Б–Є EEPROM. –°–Њ–і–µ—А–ґ–Є–Љ–Њ–µ —П—З–µ–µ–Ї —Н—В–Њ–є –њ–∞–Љ—П—В–Є –њ—А–Є –≤—Л–Ї–ї—О—З–µ–љ–Є–Є –њ–Є—В–∞–љ–Є—П

—Б–Њ—Е—А–∞–љ—П–µ—В—Б—П.

–†–µ–≥–Є—Б—В—А EEADR –Љ–Њ–ґ–µ—В

–∞–і—А–µ—Б–Њ–≤–∞—В—М –і–Њ 256 –±–∞–є—В –і–∞–љ–љ—Л—Е EEPROM. –Т –Ь–Ъ –њ–Њ–і–≥—А—Г–њ–њ—Л PIC6F8X –Є—Б–њ–Њ–ї—М–Ј—Г—О—В—Б—П —В–Њ–ї—М–Ї–Њ –њ–µ—А–≤—Л–µ 64 –±–∞–є—В–∞,

–∞–і—А–µ—Б—Г–µ–Љ—Л–µ —И–µ—Б—В—М—О –Љ–ї–∞–і—И–Є–Љ–Є –±–Є—В–∞–Љ–Є EEADR<5:0>. –Ю–і–љ–∞–Ї–Њ —Б—В–∞—А—И–Є–µ –і–≤–∞ –±–Є—В–∞ —В–∞–Ї–ґ–µ –і–µ–Ї–Њ–і–Є—А—Г—О—В—Б—П. –Я–Њ—Н—В–Њ–Љ—Г —Н—В–Є –і–≤–∞

–±–Є—В–∞ –і–Њ–ї–ґ–љ—Л –±—Л—В—М —Г—Б—В–∞–љ–Њ–≤–ї–µ–љ—Л –≤ вАШ0вАЩ, —З—В–Њ–±—Л –∞–і—А–µ—Б –њ–Њ–њ–∞–ї –≤ –і–Њ—Б—В—Г–њ–љ—Л–µ 64 –±–Є—В–∞

–∞–і—А–µ—Б–љ–Њ–≥–Њ –њ—А–Њ—Б—В—А–∞–љ—Б—В–≤–∞.

–†–µ–≥–Є—Б—В—А EECON2 –љ–µ —П–≤–ї—П–µ—В—Б—П —Д–Є–Ј–Є—З–µ—Б–Ї–Є–Љ —А–µ–≥–Є—Б—В—А–Њ–Љ.

–Ю–љ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –Є—Б–Ї–ї—О—З–Є—В–µ–ї—М–љ–Њ –њ—А–Є –Њ—А–≥–∞–љ–Є–Ј–∞—Ж–Є–Є –Ј–∞–њ–Є—Б–Є –і–∞–љ–љ—Л—Е –≤ EEPROM. –І—В–µ–љ–Є–µ —А–µ–≥–Є—Б—В—А–∞ EECON2 –і–∞–µ—В –љ—Г–ї–Є.

–Я—А–Є —Б—З–Є—В—Л–≤–∞–љ–Є–Є –і–∞–љ–љ—Л—Е –Є–Ј –њ–∞–Љ—П—В–Є EEPROM –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ –Ј–∞–њ–Є—Б–∞—В—М –љ—Г–ґ–љ—Л–є –∞–і—А–µ—Б –≤ EEADR —А–µ–≥–Є—Б—В—А –Є –Ј–∞—В–µ–Љ

—Г—Б—В–∞–љ–Њ–≤–Є—В—М –±–Є—В RD EECON1<0> –≤ –µ–і–Є–љ–Є—Ж—Г.

–Ф–∞–љ–љ—Л–µ –њ–Њ—П–≤—П—В—Б—П –≤ —Б–ї–µ–і—Г—О—Й–µ–Љ –Ї–Њ–Љ–∞–љ–і–љ–Њ–Љ —Ж–Є–Ї–ї–µ –≤ —А–µ–≥–Є—Б—В—А–µ

EEDATA –Є –Љ–Њ–≥—Г—В –±—Л—В—М –њ—А–Њ—З–Є—В–∞–љ—Л.

–Ф–∞–љ–љ—Л–µ –≤ —А–µ–≥–Є—Б—В—А–µ EEDATA —Д–Є–Ї—Б–Є—А—Г—О—В—Б—П.

–Я—А–Є –Ј–∞–њ–Є—Б–Є –≤ –њ–∞–Љ—П—В—М EEPROM –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ —Б–љ–∞—З–∞–ї–∞ –Ј–∞–њ–Є—Б–∞—В—М –∞–і—А–µ—Б –≤ EEADR-—А–µ–≥–Є—Б—В—А –Є –і–∞–љ–љ—Л–µ –≤ EEDATA-—А–µ–≥–Є—Б—В—А. –Ч–∞—В–µ–Љ —Б–ї–µ–і—Г–µ—В –≤—Л–њ–Њ–ї–љ–Є—В—М

—Б–њ–µ—Ж–Є–∞–ї—М–љ—Г—О –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ—Б—В—М –Ї–Њ–Љ–∞–љ–і, –њ—А–Њ–Є–Ј–≤–Њ–і—П—Й—Г—О –љ–µ–њ–Њ—Б—А–µ–і—Б—В–≤–µ–љ–љ—Г—О –Ј–∞–њ–Є—Б—М:

movlw 55hmovwf EECON2 movlw AAh movwf EECON2 bsf EECON1,WR;—Г—Б—В–∞–љ–Њ–≤–Є—В—М WR –±–Є—В, –љ–∞—З–∞—В—М –Ј–∞–њ–Є—Б—М

–Т–Њ –≤—А–µ–Љ—П –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П —Н—В–Њ–≥–Њ —Г—З–∞—Б—В–Ї–∞ –њ—А–Њ–≥—А–∞–Љ–Љ—Л

–≤—Б–µ –њ—А–µ—А—Л–≤–∞–љ–Є—П –і–Њ–ї–ґ–љ—Л –±—Л—В—М –Ј–∞–њ—А–µ—Й–µ–љ—Л, –і–ї—П —В–Њ—З–љ–Њ–≥–Њ

–≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –≤—А–µ–Љ–µ–љ–љ–Њ–є –і–Є–∞–≥—А–∞–Љ–Љ—Л. –Т—А–µ–Љ—П –Ј–∞–њ–Є—Б–Є вАУ –њ—А–Є–Љ–µ—А–љ–Њ 10 –Љ—Б. –§–∞–Ї—В–Є—З–µ—Б–Ї–Њ–µ

–≤—А–µ–Љ—П –Ј–∞–њ–Є—Б–Є –Љ–Њ–ґ–µ—В –Є–Ј–Љ–µ–љ—П—В—М—Б—П –≤ –Ј–∞–≤–Є—Б–Є–Љ–Њ—Б—В–Є –Њ—В –љ–∞–њ—А—П–ґ–µ–љ–Є—П, —В–µ–Љ–њ–µ—А–∞—В—Г—А—Л –Є

–Є–љ–і–Є–≤–Є–і—Г–∞–ї—М–љ—Л—Е —Б–≤–Њ–є—Б—В–≤ –Ї—А–Є—Б—В–∞–ї–ї–∞. –Т –Ї–Њ–љ—Ж–µ –Ј–∞–њ–Є—Б–Є –±–Є—В WR –∞–≤—В–Њ–Љ–∞—В–Є—З–µ—Б–Ї–Є –Њ–±–љ—Г–ї—П–µ—В—Б—П, –∞ —Д–ї–∞–≥ –Ј–∞–≤–µ—А—И–µ–љ–Є—П –Ј–∞–њ–Є—Б–Є EEIF, –Њ–љ –ґ–µ –Ј–∞–њ—А–Њ—Б –љ–∞ –њ—А–µ—А—Л–≤–∞–љ–Є–µ,

—Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞–µ—В—Б—П.

–Ф–ї—П –њ—А–µ–і–Њ—В–≤—А–∞—Й–µ–љ–Є—П —Б–ї—Г—З–∞–є–љ—Л—Е –Ј–∞–њ–Є—Б–µ–є –≤

–њ–∞–Љ—П—В—М –і–∞–љ–љ—Л—Е –њ—А–µ–і—Г—Б–Љ–Њ—В—А–µ–љ —Б–њ–µ—Ж–Є–∞–ї—М–љ—Л–є –±–Є—В WREN –≤ —А–µ–≥–Є—Б—В—А–µ EECON1. –†–µ–Ї–Њ–Љ–µ–љ–і—Г–µ—В—Б—П –і–µ—А–ґ–∞—В—М –±–Є—В WREN –≤—Л–Ї–ї—О—З–µ–љ–љ—Л–Љ, –Ї—А–Њ–Љ–µ —В–µ—Е —Б–ї—Г—З–∞–µ–≤, –Ї–Њ–≥–і–∞ –љ—Г–ґ–љ–Њ –Њ–±–љ–Њ–≤–Є—В—М –њ–∞–Љ—П—В—М

–і–∞–љ–љ—Л—Е. –С–Њ–ї–µ–µ —В–Њ–≥–Њ, –Ї–Њ–і–Њ–≤—Л–µ —Б–µ–≥–Љ–µ–љ—В—Л, –Ї–Њ—В–Њ—А—Л–µ —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞—О—В –±–Є—В WREN, –Є —В–µ, –Ї–Њ—В–Њ—А—Л–µ –≤—Л–њ–Њ–ї–љ—П—О—В –Ј–∞–њ–Є—Б—М, —Б–ї–µ–і—Г–µ—В —Е—А–∞–љ–Є—В—М –љ–∞

—А–∞–Ј–ї–Є—З–љ—Л—Е –∞–і—А–µ—Б–∞—Е, —З—В–Њ–±—Л –Є–Ј–±–µ–ґ–∞—В—М —Б–ї—Г—З–∞–є–љ–Њ–≥–Њ –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –Є—Е –Њ–±–Њ–Є—Е –њ—А–Є —Б–±–Њ–µ

–њ—А–Њ–≥—А–∞–Љ–Љ—Л.

12. –Ю—А–≥–∞–љ–Є–Ј–∞—Ж–Є—П –њ—А–µ—А—Л–≤–∞–љ–Є–є

–Ь–Ъ –њ–Њ–і–≥—А—Г–њ–њ—Л PIC16F8X –Є–Љ–µ—О—В —З–µ—В—Л—А–µ

–Є—Б—В–Њ—З–љ–Є–Ї–∞ –њ—А–µ—А—Л–≤–∞–љ–Є–є:

¬Ј

–≤–љ–µ—И–љ–µ–µ –њ—А–µ—А—Л–≤–∞–љ–Є–µ —Б

–≤—Л–≤–Њ–і–∞ RB0/INT;

¬Ј

–њ—А–µ—А—Л–≤–∞–љ–Є–µ –Њ—В

–њ–µ—А–µ–њ–Њ–ї–љ–µ–љ–Є—П —Б—З–µ—В—З–Є–Ї–∞/—В–∞–є–Љ–µ—А–∞ TMR0;

¬Ј

–њ—А–µ—А—Л–≤–∞–љ–Є–µ –Њ—В

–Є–Ј–Љ–µ–љ–µ–љ–Є—П —Б–Є–≥–љ–∞–ї–Њ–≤ –љ–∞ –ї–Є–љ–Є—П—Е –њ–Њ—А—В–∞ RB<7:4>;

¬Ј

–њ—А–µ—А—Л–≤–∞–љ–Є–µ –њ–Њ

–Њ–Ї–Њ–љ—З–∞–љ–Є–Є –Ј–∞–њ–Є—Б–Є –і–∞–љ–љ—Л—Е –≤ EEPROM.

–Т—Б–µ –њ—А–µ—А—Л–≤–∞–љ–Є—П

–Є–Љ–µ—О—В –Њ–і–Є–љ –Є —В–Њ—В –ґ–µ –≤–µ–Ї—В–Њ—А/–∞–і—А–µ—Б вАУ 0004h. –Ю–і–љ–∞–Ї–Њ –≤ —Г–њ—А–∞–≤–ї—П—О—Й–µ–Љ —А–µ–≥–Є—Б—В—А–µ

–њ—А–µ—А—Л–≤–∞–љ–Є–є INTCON —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–Є–Љ –±–Є—В–Њ–Љ-–њ—А–Є–Ј–љ–∞–Ї–Њ–Љ –Ј–∞–њ–Є—Б—Л–≤–∞–µ—В—Б—П, –Њ—В –Ї–∞–Ї–Њ–≥–Њ

–Є–Љ–µ–љ–љ–Њ –Є—Б—В–Њ—З–љ–Є–Ї–∞ –њ–Њ—Б—В—Г–њ–Є–ї –Ј–∞–њ—А–Њ—Б –њ—А–µ—А—Л–≤–∞–љ–Є—П.

–Ш—Б–Ї–ї—О—З–µ–љ–Є–µ —Б–Њ—Б—В–∞–≤–ї—П–µ—В –њ—А–µ—А—Л–≤–∞–љ–Є–µ –њ–Њ –Ј–∞–≤–µ—А—И–µ–љ–Є–Є

–Ј–∞–њ–Є—Б–Є –≤ EEPROM, –њ—А–Є–Ј–љ–∞–Ї –Ї–Њ—В–Њ—А–Њ–≥–Њ

–љ–∞—Е–Њ–і–Є—В—Б—П –≤ —А–µ–≥–Є—Б—В—А–µ EECON1.

–С–Є—В –Њ–±—Й–µ–≥–Њ —А–∞–Ј—А–µ—И–µ–љ–Є—П/–Ј–∞–њ—А–µ—Й–µ–љ–Є—П –њ—А–µ—А—Л–≤–∞–љ–Є—П GIE (INTCON <7>) —А–∞–Ј—А–µ—И–∞–µ—В

(–µ—Б–ї–Є = 1) –≤—Б–µ –Є–љ–і–Є–≤–Є–і—Г–∞–ї—М–љ–Њ –љ–µ–Ј–∞–Љ–∞—Б–Ї–Є—А–Њ–≤–∞–љ–љ—Л–µ –њ—А–µ—А—Л–≤–∞–љ–Є—П

–Є–ї–Є –Ј–∞–њ—А–µ—Й–∞–µ—В –Є—Е (–µ—Б–ї–Є = 0). –Ъ–∞–ґ–і–Њ–µ –њ—А–µ—А—Л–≤–∞–љ–Є–µ –≤

–Њ—В–і–µ–ї—М–љ–Њ—Б—В–Є –Љ–Њ–ґ–µ—В –±—Л—В—М –і–Њ–њ–Њ–ї–љ–Є—В–µ–ї—М–љ–Њ —А–∞–Ј—А–µ—И–µ–љ–Њ/–Ј–∞–њ—А–µ—Й–µ–љ–Њ —Г—Б—В–∞–љ–Њ–≤–Ї–Њ–є/—Б–±—А–Њ—Б–Њ–Љ

—Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–µ–≥–Њ –±–Є—В–∞ –≤ —А–µ–≥–Є—Б—В—А–µ INTCON.

–С–Є—В GIE –њ—А–Є —Б–±—А–Њ—Б–µ –Њ–±–љ—Г–ї—П–µ—В—Б—П. –Ъ–Њ–≥–і–∞ –љ–∞—З–Є–љ–∞–µ—В –Њ–±—А–∞–±–∞—В—Л–≤–∞—В—М—Б—П –њ—А–µ—А—Л–≤–∞–љ–Є–µ, –±–Є—В GIE –Њ–±–љ—Г–ї—П–µ—В—Б—П, —З—В–Њ–±—Л –Ј–∞–њ—А–µ—В–Є—В—М –і–∞–ї—М–љ–µ–є—И–Є–µ –њ—А–µ—А—Л–≤–∞–љ–Є—П,

–∞–і—А–µ—Б –≤–Њ–Ј–≤—А–∞—В–∞ –њ–Њ—Б—Л–ї–∞–µ—В—Б—П –≤ —Б—В–µ–Ї, –∞ –≤ –њ—А–Њ–≥—А–∞–Љ–Љ–љ—Л–є —Б—З–µ—В—З–Є–Ї –Ј–∞–≥—А—Г–ґ–∞–µ—В—Б—П –∞–і—А–µ—Б 0004h. –Т—А–µ–Љ—П —А–µ–∞–Ї—Ж–Є–Є –љ–∞ –њ—А–µ—А—Л–≤–∞–љ–Є–µ –і–ї—П

–≤–љ–µ—И–љ–Є—Е —Б–Њ–±—Л—В–Є–є, —В–∞–Ї–Є—Е –Ї–∞–Ї –њ—А–µ—А—Л–≤–∞–љ–Є–µ –Њ—В –љ–Њ–ґ–Ї–Є INT –Є–ї–Є –њ–Њ—А—В–∞ B, —Б–Њ—Б—В–∞–≤–ї—П–µ—В –њ—А–Є–±–ї–Є–Ј–Є—В–µ–ї—М–љ–Њ –њ—П—В—М —Ж–Є–Ї–ї–Њ–≤. –≠—В–Њ –љ–∞ –Њ–і–Є–љ —Ж–Є–Ї–ї

–Љ–µ–љ—М—И–µ, —З–µ–Љ –і–ї—П –≤–љ—Г—В—А–µ–љ–љ–Є—Е —Б–Њ–±—Л—В–Є–є, —В–∞–Ї–Є—Е –Ї–∞–Ї –њ—А–µ—А—Л–≤–∞–љ–Є–µ

–њ–Њ –њ–µ—А–µ–њ–Њ–ї–љ–µ–љ–Є—О –Њ—В —В–∞–є–Љ–µ—А–∞ TMR0. –Т—А–µ–Љ—П —А–µ–∞–Ї—Ж–Є–Є –≤—Б–µ–≥–і–∞ –Њ–і–Є–љ–∞–Ї–Њ–≤–Њ–µ.

–Т –њ–Њ–і–њ—А–Њ–≥—А–∞–Љ–Љ–µ –Њ–±—А–∞–±–Њ—В–Ї–Є –њ—А–µ—А—Л–≤–∞–љ–Є—П –Є—Б—В–Њ—З–љ–Є–Ї –њ—А–µ—А—Л–≤–∞–љ–Є—П

–Љ–Њ–ґ–µ—В –±—Л—В—М –Њ–њ—А–µ–і–µ–ї–µ–љ –њ–Њ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–µ–Љ—Г –±–Є—В—Г –≤ —А–µ–≥–Є—Б—В—А–µ

–њ—А–Є–Ј–љ–∞–Ї–Њ–≤. –≠—В–Њ—В —Д–ї–∞–≥-–њ—А–Є–Ј–љ–∞–Ї –і–Њ–ї–ґ–µ–љ –±—Л—В—М –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ —Б–±—А–Њ—И–µ–љ –≤–љ—Г—В—А–Є

–њ–Њ–і–њ—А–Њ–≥—А–∞–Љ–Љ—Л. –Я—А–Є–Ј–љ–∞–Ї–Є –Ј–∞–њ—А–Њ—Б–Њ–≤ –њ—А–µ—А—Л–≤–∞–љ–Є–є –љ–µ

–Ј–∞–≤–Є—Б—П—В –Њ—В —Б–Њ–Њ—В–≤–µ—В—Б—В–≤—Г—О—Й–Є—Е –Љ–∞—Б–Ї–Є—А—Г—О—Й–Є—Е –±–Є—В–Њ–≤ –Є –±–Є—В–∞ –Њ–±—Й–µ–≥–Њ –Љ–∞—Б–Ї–Є—А–Њ–≤–∞–љ–Є—П GIE.

–Ъ–Њ–Љ–∞–љ–і–∞ –≤–Њ–Ј–≤—А–∞—В–∞ –Є–Ј –њ—А–µ—А—Л–≤–∞–љ–Є—П

RETFIE –Ј–∞–≤–µ—А—И–∞–µ—В –њ—А–µ—А—Л–≤–∞—О—Й—Г—О –њ–Њ–і–њ—А–Њ–≥—А–∞–Љ–Љ—Г

–Є —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞–µ—В –±–Є—В GIE, —З—В–Њ–±—Л –Њ–њ—П—В—М —А–∞–Ј—А–µ—И–Є—В—М –њ—А–µ—А—Л–≤–∞–љ–Є—П.

–Ы–Њ–≥–Є–Ї–∞ –њ—А–µ—А—Л–≤–∞–љ–Є–є

–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞ –Є–Ј–Њ–±—А–∞–ґ–µ–љ–∞ –љ–∞ —А–Є—Б. 14.

–†–Є—Б. 5.14. –Ы–Њ–≥–Є–Ї–∞ –њ—А–µ—А—Л–≤–∞–љ–Є–є

–Љ–Є–Ї—А–Њ–Ї–Њ–љ—В—А–Њ–ї–ї–µ—А–∞

–Т–љ–µ—И–љ–µ–µ –њ—А–µ—А—Л–≤–∞–љ–Є–µ

–љ–∞ –љ–Њ–ґ–Ї–µ RB0/INT

–Њ—Б—Г—Й–µ—Б—В–≤–ї—П–µ—В—Б—П –њ–Њ —Д—А–Њ–љ—В—Г: –ї–Є–±–Њ –њ–Њ –љ–∞—А–∞—Б—В–∞—О—Й–µ–Љ—Г (–µ—Б–ї–Є –≤ —А–µ–≥–Є—Б—В—А–µ

OPTION –±–Є—В INTEDG=1), –ї–Є–±–Њ –њ–Њ —Б–њ–∞–і–∞—О—Й–µ–Љ—Г (–µ—Б–ї–Є INTEDG=0). –Ъ–Њ–≥–і–∞ —Д—А–Њ–љ—В –Њ–±–љ–∞—А—Г–ґ–Є–≤–∞–µ—В—Б—П –љ–∞ –љ–Њ–ґ–Ї–µ INT, –±–Є—В –Ј–∞–њ—А–Њ—Б–∞ INTF —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞–µ—В—Б—П –≤ –µ–і–Є–љ–Є—Ж—Г (INTCON <1>). –≠—В–Њ –њ—А–µ—А—Л–≤–∞–љ–Є–µ –Љ–Њ–ґ–µ—В –±—Л—В—М

–Ј–∞–Љ–∞—Б–Ї–Є—А–Њ–≤–∞–љ–Њ —Б–±—А–Њ—Б–Њ–Љ —Г–њ—А–∞–≤–ї—П—О—Й–µ–≥–Њ –±–Є—В–∞ INTE –≤ –љ–Њ–ї—М (INTCON <4>). –С–Є—В –Ј–∞–њ—А–Њ—Б–∞ INTF –љ–µ–Њ–±—Е–Њ–і–Є–Љ–Њ –Њ—З–Є—Б—В–Є—В—М –њ—А–µ—А—Л–≤–∞—О—Й–µ–є –њ—А–Њ–≥—А–∞–Љ–Љ–Њ–є –њ–µ—А–µ–і —В–µ–Љ, –Ї–∞–Ї

–Њ–њ—П—В—М —А–∞–Ј—А–µ—И–Є—В—М —Н—В–Њ –њ—А–µ—А—Л–≤–∞–љ–Є–µ. –Я—А–µ—А—Л–≤–∞–љ–Є–µ INT –Љ–Њ–ґ–µ—В –≤—Л–≤–µ—Б—В–Є –њ—А–Њ—Ж–µ—Б—Б–Њ—А –Є–Ј —А–µ–ґ–Є–Љ–∞ SLEEP, –µ—Б–ї–Є –њ–µ—А–µ–і –≤—Е–Њ–і–Њ–Љ –≤ —Н—В–Њ—В —А–µ–ґ–Є–Љ –±–Є—В INTE –±—Л–ї —Г—Б—В–∞–љ–Њ–≤–ї–µ–љ –≤ –µ–і–Є–љ–Є—Ж—Г. –°–Њ—Б—В–Њ—П–љ–Є–µ –±–Є—В–∞ GIE —В–∞–Ї–ґ–µ –Њ–њ—А–µ–і–µ–ї—П–µ—В, –±—Г–і–µ—В –ї–Є –њ—А–Њ—Ж–µ—Б—Б–Њ—А –њ–µ—А–µ—Е–Њ–і–Є—В—М –љ–∞

–њ–Њ–і–њ—А–Њ–≥—А–∞–Љ–Љ—Г –њ—А–µ—А—Л–≤–∞–љ–Є—П –њ–Њ—Б–ї–µ –≤—Л—Е–Њ–і–∞ –Є–Ј —А–µ–ґ–Є–Љ–∞ SLEEP.

–Я–µ—А–µ–њ–Њ–ї–љ–µ–љ–Є–µ —Б—З–µ—В—З–Є–Ї–∞ TMR0 (FFh->00h)

—Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞–µ—В –≤ –µ–і–Є–љ–Є—Ж—Г –±–Є—В –Ј–∞–њ—А–Њ—Б–∞ T0IF (INTCON<2>). –≠—В–Њ –њ—А–µ—А—Л–≤–∞–љ–Є–µ –Љ–Њ–ґ–µ—В –±—Л—В—М —А–∞–Ј—А–µ—И–µ–љ–Њ/–Ј–∞–њ—А–µ—Й–µ–љ–Њ

—Г—Б—В–∞–љ–Њ–≤–Ї–Њ–є/—Б–±—А–Њ—Б–Њ–Љ –±–Є—В–∞ –Љ–∞—Б–Ї–Є T0IE (INTCON<5>). –°–±—А–Њ—Б –Ј–∞–њ—А–Њ—Б–∞

T0IF вАУ –і–µ–ї–Њ –њ—А–Њ–≥—А–∞–Љ–Љ—Л –Њ–±—А–∞–±–Њ—В–Ї–Є.

–Ы—О–±–Њ–µ –Є–Ј–Љ–µ–љ–µ–љ–Є–µ —Б–Є–≥–љ–∞–ї–∞ –љ–∞ –Њ–і–љ–Њ–Љ –Є–Ј —З–µ—В—Л—А–µ—Е

–≤—Е–Њ–і–Њ–≤ –њ–Њ—А—В–∞ RB<7:4> —Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞–µ—В –≤ –µ–і–Є–љ–Є—Ж—Г –±–Є—В RBIF (INTCON<0>). –≠—В–Њ –њ—А–µ—А—Л–≤–∞–љ–Є–µ –Љ–Њ–ґ–µ—В –±—Л—В—М —А–∞–Ј—А–µ—И–µ–љ–Њ/–Ј–∞–њ—А–µ—Й–µ–љ–Њ —Г—Б—В–∞–љ–Њ–≤–Ї–Њ–є/—Б–±—А–Њ—Б–Њ–Љ

–±–Є—В–∞ –Љ–∞—Б–Ї–Є RBIE (INTCON<3>). –°–±—А–Њ—Б –Ј–∞–њ—А–Њ—Б–∞ RBIF вАУ –і–µ–ї–Њ –њ—А–Њ–≥—А–∞–Љ–Љ—Л –Њ–±—А–∞–±–Њ—В–Ї–Є.

–Я—А–Є–Ј–љ–∞–Ї –Ј–∞–њ—А–Њ—Б–∞ –њ—А–µ—А—Л–≤–∞–љ–Є—П

–њ–Њ –Ј–∞–≤–µ—А—И–µ–љ–Є–Є –Ј–∞–њ–Є—Б–Є –≤ EEPROM, EEIF (EECON1<4>)

—Г—Б—В–∞–љ–∞–≤–ї–Є–≤–∞–µ—В—Б—П –≤ –µ–і–Є–љ–Є—Ж—Г –њ–Њ –Њ–Ї–Њ–љ—З–∞–љ–Є–Є –∞–≤—В–Њ–Љ–∞—В–Є—З–µ—Б–Ї–Њ–є –Ј–∞–њ–Є—Б–Є –і–∞–љ–љ—Л—Е –≤ EEPROM. –≠—В–Њ –њ—А–µ—А—Л–≤–∞–љ–Є–µ –Љ–Њ–ґ–µ—В –±—Л—В—М

–Ј–∞–Љ–∞—Б–Ї–Є—А–Њ–≤–∞–љ–Њ —Б–±—А–Њ—Б–Њ–Љ –±–Є—В–∞ EEIE (INTCON<6>). –°–±—А–Њ—Б –Ј–∞–њ—А–Њ—Б–∞ EEIF вАУ –і–µ–ї–Њ –њ—А–Њ–≥—А–∞–Љ–Љ—Л –Њ–±—А–∞–±–Њ—В–Ї–Є.

1) –≠—В–Њ—В

–±—Г—Д–µ—А –Є–Љ–µ–µ—В –≤—Е–Њ–і —В—А–Є–≥–≥–µ—А–∞ –®–Љ–Є—В—В–∞, –Ї–Њ–≥–і–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А—Г–µ—В—Б—П –≤ —А–µ–ґ–Є–Љ–µ RC-–≥–µ–љ–µ—А–∞—В–Њ—А–∞

–Є –Ъ–Ь–Ю–Я-–≤—Е–Њ–і –≤ –Њ—Б—В–∞–ї—М–љ—Л—Е —Б–ї—Г—З–∞—П—Е.

2) –≠—В–Њ—В –±—Г—Д–µ—А –Є–Љ–µ–µ—В –≤—Е–Њ–і —В—А–Є–≥–≥–µ—А–∞

–®–Љ–Є—В—В–∞, –Ї–Њ–≥–і–∞ –Ї–Њ–љ—Д–Є–≥—Г—А–Є—А—Г–µ—В—Б—П –≤ –Ї–∞—З–µ—Б—В–≤–µ –≤—Е–Њ–і–∞ –≤–љ–µ—И–љ–µ–≥–Њ –њ—А–µ—А—Л–≤–∞–љ–Є—П.

3) –≠—В–Њ—В –±—Г—Д–µ—А –Є–Љ–µ–µ—В –≤—Е–Њ–і —В—А–Є–≥–≥–µ—А–∞

–®–Љ–Є—В—В–∞, –Ї–Њ–≥–і–∞ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –≤ —А–µ–ґ–Є–Љ–µ –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ–≥–Њ –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П.

4) –≠—В–Њ—В –±—Г—Д–µ—А –Є–Љ–µ–µ—В –≤—Е–Њ–і —В—А–Є–≥–≥–µ—А–∞

–®–Љ–Є—В—В–∞, –Ї–Њ–≥–і–∞ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –≤ —А–µ–ґ–Є–Љ–µ –њ–Њ—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ–≥–Њ –њ—А–Њ–≥—А–∞–Љ–Љ–Є—А–Њ–≤–∞–љ–Є—П.