–õ–Ķ–ļ—Ü–ł—Ź. –ě—Ä–≥–į–Ĺ–ł–∑–į—Ü–ł—Ź –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā–ł –ú–ö

–ü–õ–ź–Ě

–õ–ē–ö–¶–ė–ė

1.

–ź–Ĺ–į–Ľ–ł–∑ –Ņ–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł—Ź –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā–ł

2.

–ü—Ä–ł–ľ–Ķ—Ä –Ņ–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł—Ź –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā–ł –ī–į–Ĺ–Ĺ—č—Ö –ļ

–ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É Z80

3.

–ü—Ä–ł–ľ–Ķ—Ä –Ņ–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł—Ź –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā–ł –ī–į–Ĺ–Ĺ—č—Ö –ļ

–ľ–ł–ļ—Ä–ĺ–ļ—Ä–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä—É —Ā–Ķ–ľ–Ķ–Ļ—Ā—ā–≤–į x51

4.

–ü–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł—Ź –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā–ł –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ –ļ

–ľ–ł–ļ—Ä–ĺ–ļ—Ä–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä—É —Ā–Ķ–ľ–Ķ–Ļ—Ā—ā–≤–į x51

1.

–ź–Ĺ–į–Ľ–ł–∑

–Ņ–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł—Ź –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā–ł

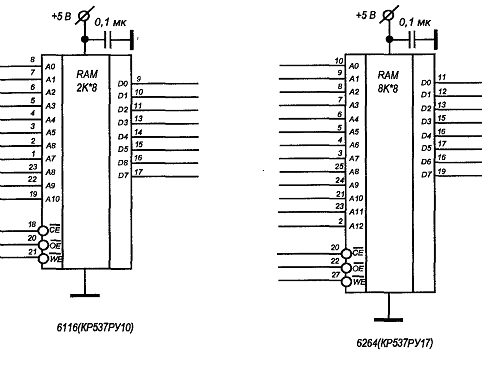

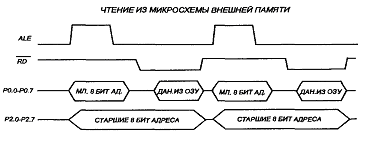

–í–Ĺ–Ķ—ą–Ĺ—Ź—Ź

–Ņ–į–ľ—Ź—ā—Ć –ī–į–Ĺ–Ĺ—č—Ö –Ņ—Ä–Ķ–ī—Ā—ā–į–≤–Ľ—Ź–Ķ—ā —Ā–ĺ–Ī–ĺ–Ļ –ĺ–ī–Ĺ—É –ł–Ľ–ł –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ —Ā–į–ľ–ĺ—Ā—ā–ĺ—Ź—ā–Ķ–Ľ—Ć–Ĺ—č—Ö –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ

–Ņ–į–ľ—Ź—ā–ł. –ß–į—Č–Ķ –≤—Ā–Ķ–≥–ĺ –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É—é—ā —Ā—ā–į—ā–ł—á–Ķ—Ā–ļ—É—é –Ņ–į–ľ—Ź—ā—Ć —Ā –Ī–į–Ļ—ā–ĺ–≤–ĺ–Ļ –ĺ—Ä–≥–į–Ĺ–ł–∑–į—Ü–ł–Ķ–Ļ

–ĺ–Ī—ä–Ķ–ľ–ĺ–ľ 2–ö*8 –ł–Ľ–ł 8–ö*8 –Ī–ł—ā (1–ö = 1024). –Ę–į–ļ–ł–Ķ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č; –ł–ľ–Ķ—é—ā 8 –≤—č–≤–ĺ–ī–ĺ–≤ –ī–į–Ĺ–Ĺ—č—Ö

(D0-D7), –Ņ–ĺ –ļ–ĺ—ā–ĺ—Ä—č–ľ –ĺ—Ā—É—Č–Ķ—Ā—ā–≤–Ľ—Ź–Ķ—ā—Ā—Ź –ĺ–ī–Ĺ–ĺ-–≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ–į—Ź –∑–į–Ņ–ł—Ā—Ć –≤ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—É –≤—Ā–Ķ—Ö 8

–Ī–ł—ā –≤ –≤—č–Ī—Ä–į–Ĺ–Ĺ—É—é —Ź—á–Ķ–Ļ–ļ—É –Ņ–į–ľ—Ź—ā–ł –ł–Ľ–ł —á—ā–Ķ–Ĺ–ł–Ķ 8 –Ī–ł—ā –ł–∑ —ć—ā–ĺ–Ļ —Ź—á–Ķ–Ļ–ļ–ł. –Ē–į–Ľ–Ķ–Ķ, –≤ —ā–į–ļ–ł—Ö

–ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ–į—Ö –Ķ—Ā—ā—Ć 11 –ł–Ľ–ł. 13 –į–ī—Ä–Ķ—Ā–Ĺ—č—Ö –≤—Ö–ĺ–ī–ĺ–≤ (–ź0-–ź10 –ł–Ľ–ł –ź0-–ź12), –ļ–ĺ–ľ–Ī–ł–Ĺ–į—Ü–ł—Ź

—Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ –Ĺ–į –ļ–ĺ—ā–ĺ—Ä—č—Ö –∑–į–ī–į–Ķ—ā –į–ī—Ä–Ķ—Ā —Ź—á–Ķ–Ļ–ļ–ł, –ļ –ļ–ĺ—ā–ĺ—Ä–ĺ–Ļ –ľ—č –ĺ–Ī—Ä–į—Č–į–Ķ–ľ—Ā—Ź. –í—Ö–ĺ–ī (Write Enable ‚Äď –†–į–∑—Ä–Ķ—ą–Ķ–Ĺ–ł–Ķ –ó–į–Ņ–ł—Ā–ł)

–ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ—Ź–Ķ—ā —Ö–į—Ä–į–ļ—ā–Ķ—Ä –ĺ–Ī—Ä–į—Č–Ķ–Ĺ–ł—Ź: –Ķ—Ā–Ľ–ł –Ĺ–į –Ĺ–Ķ–ľ —É—Ā—ā–į–Ĺ–ĺ–≤–Ľ–Ķ–Ĺ–į 1, —ā–ĺ –ĺ—Ā—É—Č–Ķ—Ā—ā–≤–Ľ—Ź–Ķ—ā—Ā—Ź —á—ā–Ķ–Ĺ–ł–Ķ

–ł–∑ –≤—č–Ī—Ä–į–Ĺ–Ĺ–ĺ–Ļ —Ź—á–Ķ–Ļ–ļ–ł; –Ņ—Ä–ł WE = 0 –≤ —Ź—á–Ķ–Ļ–ļ—É –Ī—É–ī–Ķ—ā –∑–į–Ņ–ł—Ā–į–Ĺ–į –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł—Ź. –í—Ö–ĺ–ī (Chip Enable - –†–į–∑—Ä–Ķ—ą–Ķ–Ĺ–ł–Ķ –ö—Ä–ł—Ā—ā–į–Ľ–į)

–į–ļ—ā–ł–≤–ł–∑–ł—Ä—É–Ķ—ā –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—É –Ņ–į–ľ—Ź—ā–ł ‚Äď –ļ–ĺ–≥–ī–į –Ĺ–į –Ķ–Ķ –≤—Ö–ĺ–ī–Ķ –°–ē —É—Ā—ā–į–Ĺ–ĺ–≤–Ľ–Ķ–Ĺ–į 1, –ĺ–Ĺ–į

–≤—č–ļ–Ľ—é—á–Ķ–Ĺ–į, –Ņ—Ä–ł –°–ē = 0 –ĺ–Ĺ–į –ī–ĺ–Ņ—É—Ā–ļ–į–Ķ—ā –∑–į–Ņ–ł—Ā—Ć –≤ –Ĺ–Ķ–Ķ –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł –ł —á—ā–Ķ–Ĺ–ł–Ķ –ł–∑ –Ĺ–Ķ–Ķ –∑–į–Ņ–ł—Ā–į–Ĺ–Ĺ—č—Ö

–ī–į–Ĺ–Ĺ—č—Ö. –Ě—É–Ľ–Ķ–≤–ĺ–Ļ —Ā–ł–≥–Ĺ–į–Ľ –Ĺ–į –≤—Ö–ĺ–ī–Ķ (Output Enable ‚Äď –†–į–∑—Ä–Ķ—ą–Ķ–Ĺ–ł–Ķ –í—č–≤–ĺ–ī–į)

–≤–ļ–Ľ—é—á–į–Ķ—ā –≤—č—Ö–ĺ–ī–Ĺ—č–Ķ –Ī—É—Ą–Ķ—Ä—č –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č –Ņ–į–ľ—Ź—ā–ł –Ĺ–į –Ņ—Ä–ĺ–Ņ—É—Ā–ļ–į–Ĺ–ł–Ķ –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł –Ņ–ĺ –Ľ–ł–Ĺ–ł—Ź–ľ

–ī–į–Ĺ–Ĺ—č—Ö D0-D7, –Ķ–ī–ł–Ĺ–ł—á–Ĺ—č–Ļ —Ā–ł–≥–Ĺ–į–Ľ –Ņ–Ķ—Ä–Ķ–≤–ĺ–ī–ł—ā —ć—ā–ł –Ľ–ł–Ĺ–ł–ł –≤ —ā—Ä–Ķ—ā—Ć–Ķ —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł–Ķ, —ā. –Ķ.

–ĺ—ā–ļ–Ľ—é—á–į–Ķ—ā –Ĺ–į—Ö–ĺ–ī—Ź—Č–ł–Ķ—Ā—Ź –≤–Ĺ—É—ā—Ä–ł –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č —Ź—á–Ķ–Ļ–ļ–ł –Ņ–į–ľ—Ź—ā–ł –ĺ—ā –Ķ–Ķ –Ĺ–ĺ–∂–Ķ–ļ. –ě–Ņ–ł—Ā—č–≤–į–Ķ–ľ—č–Ķ

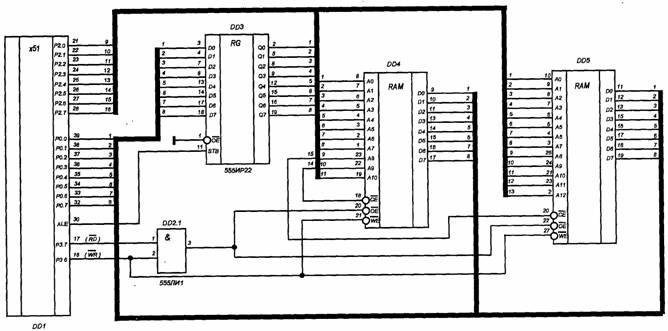

–ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č –ł–∑–ĺ–Ī—Ä–į–∂–Ķ–Ĺ—č –Ĺ–į —Ä–ł—Ā—É–Ĺ–ļ–Ķ 7.

–†–ł—Ā. 7.

–ě–Ī–ĺ–∑–Ĺ–į—á–Ķ–Ĺ–ł–Ķ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ –Ņ–į–ľ—Ź—ā–ł

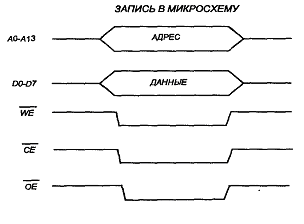

–†–į–Ī–ĺ—ā–į

—Ā –Ņ–ĺ–ī–ĺ–Ī–Ĺ—č–ľ–ł –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ–į–ľ–ł –ī–ĺ–Ľ–∂–Ĺ–į –ĺ—Ā—É—Č–Ķ—Ā—ā–≤–Ľ—Ź—ā—Ć—Ā—Ź —Ā–Ľ–Ķ–ī—É—é—Č–ł–ľ –ĺ–Ī—Ä–į–∑–ĺ–ľ. –ü–ĺ–Ľ–ĺ–∂–ł–ľ, –ľ—č

—Ö–ĺ—ā–ł–ľ –∑–į–Ņ–ł—Ā–į—ā—Ć —á–ł—Ā–Ľ–ĺ 145D = 10010001–í –≤ —Ź—á–Ķ–Ļ–ļ—É —Ā –į–ī—Ä–Ķ—Ā–ĺ–ľ 84D = 54–Ě = 1010100–í.

–Ē–Ľ—Ź —ć—ā–ĺ–≥–ĺ –ú–ö –ī–ĺ–Ľ–∂–Ķ–Ĺ —É—Ā—ā–į–Ĺ–ĺ–≤–ł—ā—Ć –∑–į–Ņ–ł—Ā—č–≤–į–Ķ–ľ–ĺ–Ķ —á–ł—Ā–Ľ–ĺ –Ĺ–į –Ľ–ł–Ĺ–ł—Ź—Ö –ī–į–Ĺ–Ĺ—č—Ö D0-D7

–ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č (D0=D4=D7=1, D1=D2-D3=D5=D6=0), –į –į–ī—Ä–Ķ—Ā —Ź—á–Ķ–Ļ–ļ–ł ‚Äď –Ĺ–į –į–ī—Ä–Ķ—Ā–Ĺ—č—Ö –Ľ–ł–Ĺ–ł—Ź—Ö

(–ź2=–ź4=–ź6=1, –ź0=–ź1=–ź–ó=–ź5=0; –ź7, –ź8 –ł –Ņ–ĺ—Ā–Ľ–Ķ–ī—É—é—Č–ł–Ķ —Ā—ā–į—Ä—ą–ł–Ķ –į–ī—Ä–Ķ—Ā–į –≤–Ņ–Ľ–ĺ—ā—Ć –ī–ĺ –ź10

–ī–Ľ—Ź –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ –ĺ–Ī—ä–Ķ–ľ–ĺ–ľ 2–ö* 8 –ł–Ľ–ł –ī–ĺ –ź12 –ī–Ľ—Ź –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ 8–ö*8 —ā–į–ļ–∂–Ķ –ī–ĺ–Ľ–∂–Ĺ—č –Ī—č—ā—Ć

—É—Ā—ā–į–Ĺ–ĺ–≤–Ľ–Ķ–Ĺ—č –≤ 0). –£—Ā—ā–į–Ĺ–ĺ–≤–ł–≤ –į–ī—Ä–Ķ—Ā–Ĺ—É—é –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł—é –ł –ī–į–Ĺ–Ĺ—č–Ķ, –ú–ö –ĺ–ī–Ĺ–ĺ–≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ–ĺ —Ā

—ć—ā–ł–ľ –ł–Ľ–ł —á—É—ā—Ć –Ņ–ĺ–∑–∂–Ķ –ī–ĺ–Ľ–∂–Ķ–Ĺ —É—Ā—ā–į–Ĺ–ĺ–≤–ł—ā—Ć 0 –Ĺ–į –≤—Ö–ĺ–ī–Ķ WE –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č (–Ī—É–ī–Ķ—ā –∑–į–Ņ–ł—Ā—Ć) –ł

0 –Ĺ–į –°–ē (–∑–Ĺ–į–ļ —ā–ĺ–≥–ĺ, —á—ā–ĺ –ľ—č –ĺ–Ī—Ä–į—Č–į–Ķ–ľ—Ā—Ź –ł–ľ–Ķ–Ĺ–Ĺ–ĺ –ļ —ć—ā–ĺ–Ļ –ľ–ł–ļ¬≠—Ä–ĺ—Ā—Ö–Ķ–ľ–Ķ). –ö–į–ļ —ā–ĺ–Ľ—Ć–ļ–ĺ

–Ņ–ĺ—Ā–Ľ–Ķ —ć—ā–ĺ–≥–ĺ –Ĺ–į –≤—Ö–ĺ–ī–Ķ –ě–ē –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č –Ņ–į–ľ—Ź—ā–ł –ú–ö —É—Ā—ā–į–Ĺ–ĺ–≤–ł—ā 0, –ĺ—Ā—É—Č–Ķ—Ā—ā–≤–ł—ā—Ā—Ź –∑–į–Ņ–ł—Ā—Ć

—á–ł—Ā–Ľ–į 145 –≤ –Ķ–Ķ 84-—é —Ź—á–Ķ–Ļ–ļ—É.

–°–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ,

–Ķ—Ā–Ľ–ł –ľ—č —Ö–ĺ—ā–ł–ľ –Ņ—Ä–ĺ—á–ł—ā–į—ā—Ć –ī–į–Ĺ–Ĺ—č–Ķ –ł–∑ –≤—Ā–Ķ —ā–ĺ–Ļ –∂–Ķ, –ļ –Ņ—Ä–ł–ľ–Ķ—Ä—É, 84-–Ļ —Ź—á–Ķ–Ļ–ļ–ł, –ľ—č –ī–ĺ–Ľ–∂–Ĺ—č,

–ļ–į–ļ –ł –≤ –Ņ—Ä–Ķ–ī—č–ī—É—Č–Ķ–ľ —Ā–Ľ—É—á–į–Ķ, —É—Ā¬≠—ā–į–Ĺ–ĺ–≤–ł—ā—Ć –į–ī—Ä–Ķ—Ā —Ź—á–Ķ–Ļ–ļ–ł –Ĺ–į –į–ī—Ä–Ķ—Ā–Ĺ—č—Ö –Ľ–ł–Ĺ–ł—Ź—Ö, –ł

–ĺ–ī–Ĺ–ĺ–≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ–ĺ —Ā —ć—ā–ł–ľ –ł–Ľ–ł —á—É—ā—Ć –Ņ–ĺ–∑–∂–Ķ —É—Ā—ā–į–Ĺ–ĺ–≤–ł—ā—Ć 1 –Ĺ–į –≤—Ö–ĺ–ī–Ķ WE

–ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č (–Ī—É–ī–Ķ—ā —á—ā–Ķ¬≠–Ĺ–ł–Ķ) –ł 0 –Ĺ–į –°–ē (–∑–Ĺ–į–ļ —ā–ĺ–≥–ĺ, —á—ā–ĺ –ľ—č –ĺ–Ī—Ä–į—Č–į–Ķ–ľ—Ā—Ź –ł–ľ–Ķ–Ĺ–Ĺ–ĺ –ļ

—ć—ā–ĺ–Ļ –ľ–ł–ļ—Ä–ĺ¬≠—Ā—Ö–Ķ–ľ–Ķ). –ö–į–ļ —ā–ĺ–Ľ—Ć–ļ–ĺ –Ņ–ĺ—Ā–Ľ–Ķ —ć—ā–ĺ–≥–ĺ –Ĺ–į –≤—Ö–ĺ–ī–Ķ –ě–ē –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č –Ņ–į–ľ—Ź—ā–ł –ú–ö

—É—Ā—ā–į–Ĺ–ĺ–≤–ł—ā 0, –ĺ—Ā—É—Č–Ķ—Ā—ā–≤–ł—ā—Ā—Ź —á—ā–Ķ–Ĺ–ł–Ķ —á–ł—Ā–Ľ–į –ł–∑ –≤—č–Ī—Ä–į–Ĺ–Ĺ–ĺ–Ļ —Ź—á–Ķ–Ļ–ļ–ł, –ł –ĺ–Ĺ–ĺ –Ņ–ĺ—Ź–≤–ł—ā—Ā—Ź –Ĺ–į

–Ľ–ł–Ĺ–ł—Ź—Ö –ī–į–Ĺ–Ĺ—č—Ö D0-D7 –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č –Ņ–į–ľ—Ź—ā–ł.

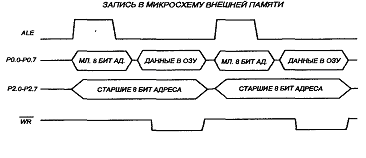

–°–ļ–į–∑–į–Ĺ–Ĺ–ĺ–Ķ –Ņ–ĺ—Ź—Ā–Ĺ—Ź–Ķ—ā—Ā—Ź –≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ—č–ľ–ł –ī–ł–į–≥—Ä–į–ľ–ľ–į–ľ–ł, –Ņ—Ä–ł–≤–Ķ–ī–Ķ–Ĺ–Ĺ—č–ľ–ł –Ĺ–į —Ä–ł—Ā—É–Ĺ–ļ–Ķ 8.

–†–ł—Ā. 8.

–Ē–ł–į–≥—Ä–į–ľ–ľ—č —á—ā–Ķ–Ĺ–ł—Ź –ł –∑–į–ľ–ł—Ā–ł –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ –Ņ–į–ľ—Ź—ā–ł

2. ¬†–ü—Ä–ł–ľ–Ķ—Ä

–Ņ–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł—Ź –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā–ł –Ē–ź–Ě–Ě–ę–•

–ļ –ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É Z80

–£ Z80 –Ķ—Ā—ā—Ć –≤—č–≤–ĺ–ī—č —ā—Ä–Ķ—Ö —ā–į–ļ –Ĺ–į–∑—č–≤–į–Ķ–ľ—č—Ö —ą–ł–Ĺ ‚Äď –į–ī—Ä–Ķ—Ā–į,

–ī–į–Ĺ–Ĺ—č—Ö –ł —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź.

–®–Ķ—Ā—ā–Ĺ–į–ī—Ü–į—ā—Ć –≤—č–≤–ĺ–ī–ĺ–≤ Z80 (–ź0, Al, –ź2,..., –ź14 –ł

–ź15) –Ĺ–į–∑—č–≤–į—é—ā—Ā—Ź –į–ī—Ä–Ķ—Ā–Ĺ—č–ľ–ł –≤—č—Ö–ĺ–ī–į–ľ–ł, –ł—Ö —Ā–ĺ–Ķ–ī–ł–Ĺ—Ź—é—ā —Ā –į–ī—Ä–Ķ—Ā–Ĺ—č–ľ–ł –≤—Ö–ĺ–ī–į–ľ–ł –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ

–Ņ–į–ľ—Ź—ā–ł. –°–ĺ–≤–ĺ–ļ—É–Ņ–Ĺ–ĺ—Ā—ā—Ć –Ľ–ł–Ĺ–ł–Ļ, –ĺ—Ā—É—Č–Ķ—Ā—ā–≤–Ľ—Ź—é—Č–ł—Ö —ć—ā–ł —Ā–ĺ–Ķ–ī–ł–Ĺ–Ķ–Ĺ–ł—Ź, –ł –Ķ—Ā—ā—Ć —ą–ł–Ĺ–į –į–ī—Ä–Ķ—Ā–į.

–°–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ, —ą–ł–Ĺ–į –ī–į–Ĺ–Ĺ—č—Ö, —Ā–ĺ—Ā—ā–ĺ—Ź—Č–į—Ź –ł–∑ 8 –Ņ—Ä–ĺ–≤–ĺ–ī–Ĺ–ł–ļ–ĺ–≤, —Ā–ĺ–Ķ–ī–ł–Ĺ—Ź–Ķ—ā –≤—č–≤–ĺ–ī—č

–ī–į–Ĺ–Ĺ—č—Ö –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ –Ņ–į–ľ—Ź—ā–ł –ł –ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į (—É –Ĺ–Ķ–≥–ĺ, –ļ–į–ļ –ł —É –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ –Ņ–į–ľ—Ź—ā–ł, –ł—Ö

—ā–ĺ–∂–Ķ 8, –ł –ĺ–Ī–ĺ–∑–Ĺ–į—á–į—é—ā—Ā—Ź –ĺ–Ĺ–ł —ā–į–ļ–∂–Ķ‚Äď D0, D1,..., D7).

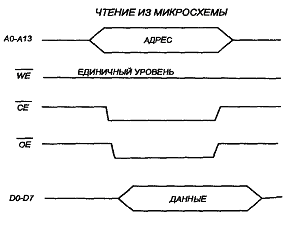

–ė–∑ —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź —É Z80 –Ĺ–į—Ā –ł–Ĺ—ā–Ķ—Ä–Ķ—Ā—É—é—ā —ā–ĺ–Ľ—Ć–ļ–ĺ –ī–≤–į ‚Äď (Read - –ß—ā–Ķ–Ĺ–ł–Ķ) –ł (Write - –ó–į–Ņ–ł—Ā—Ć).

–° –ł—Ö –Ņ–ĺ–ľ–ĺ—Č—Ć—é, –ļ–į–ļ –Ņ–ĺ–ļ–į–∑–į–Ĺ–ĺ –Ĺ–į —Ä–ł—Ā—É–Ĺ–ļ–Ķ 9, –ĺ—Ā—É—Č–Ķ—Ā—ā–≤–Ľ—Ź–Ķ—ā—Ā—Ź —É–Ņ¬≠—Ä–į–≤–Ľ–Ķ–Ĺ–ł–Ķ –Ņ–į–ľ—Ź—ā—Ć—é.

–†–ł—Ā. 9.¬†

–ü–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł–Ķ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ –Ņ–į–ľ—Ź—ā–ł –ļ –ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É Z80

–ü—Ä–ł

–ĺ–Ī—Ä–į—Č–Ķ–Ĺ–ł–ł –ļ –Ņ–į–ľ—Ź—ā–ł Z80 —Ą–ĺ—Ä–ľ–ł—Ä—É–Ķ—ā –Ĺ–į —Ā–≤–ĺ–ł—Ö –≤—č–≤–ĺ–ī–į—Ö –ź0-–ź15 –į–ī—Ä–Ķ—Ā —Ź—á–Ķ–Ļ–ļ–ł, –ļ

–ļ–ĺ—ā–ĺ—Ä–ĺ–Ļ –Ī—É–ī–Ķ—ā –Ņ—Ä–ĺ–ł—Ā—Ö–ĺ–ī–ł—ā—Ć –ĺ–Ī—Ä–į—Č–Ķ–Ĺ–ł–Ķ (–∑–į¬≠–Ņ–ł—Ā—Ć –ł–Ľ–ł —á—ā–Ķ–Ĺ–ł–Ķ). –ö–į–ļ –Ī—É–ī–Ķ—ā –Ņ–ĺ–ļ–į–∑–į–Ĺ–ĺ

—á—É—ā—Ć –Ĺ–ł–∂–Ķ, —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–į—Ź –ļ–ĺ–ľ–Ī–ł–Ĺ–į—Ü–ł—Ź —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ –Ĺ–į –ź13-–ź15 —Ā—Ą–ĺ—Ä–ľ–ł—Ä—É–Ķ—ā –Ņ—Ä–ł –Ņ–ĺ–ľ–ĺ—Č–ł

–ī–Ķ—ą–ł—Ą—Ä–į—ā–ĺ—Ä–į DD3 –Ĺ—É–Ľ–Ķ–≤–ĺ–Ļ —Ā–ł–≥–Ĺ–į–Ľ –Ĺ–į –≤—Ö–ĺ–ī–Ķ –°–ē —ā–ĺ–Ļ –ł–Ľ–ł –ł–Ĺ–ĺ–Ļ –ľ–ł–ļ¬≠—Ä–ĺ—Ā—Ö–Ķ–ľ—č.

–ü—Ä–ł

–∑–į–Ņ–ł—Ā–ł –Ĺ–į –≤—č–≤–ĺ–ī–į—Ö –ī–į–Ĺ–Ĺ—č—Ö D0-D7 –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į –Ņ–ĺ¬≠—Ź–≤–ł—ā—Ā—Ź –Ī–į–Ļ—ā,

–ļ–ĺ—ā–ĺ—Ä—č–Ļ –Ņ—Ä–Ķ–ī—Ā—ā–ĺ–ł—ā –∑–į–Ņ–ł—Ā–į—ā—Ć –≤ –Ņ–į–ľ—Ź—ā—Ć, –ł —á—É—ā—Ć-—á—É—ā—Ć –Ņ–ĺ–∑–∂–Ķ –Ķ–≥–ĺ –Ņ–ĺ—Ź–≤–Ľ–Ķ–Ĺ–ł—Ź ‚Äď –Ĺ—É–Ľ–Ķ–≤–ĺ–Ļ

—Ā–ł–≥–Ĺ–į–Ľ –Ĺ–į –≤—č—Ö–ĺ–ī–Ķ WR (RD –Ņ—Ä–ł —ć—ā–ĺ–ľ –ĺ—Ā—ā–į–Ĺ–Ķ—ā—Ā—Ź

–≤ 1). –ö–į–ļ –Ĺ–Ķ—ā—Ä—É–ī–Ĺ–ĺ –ī–ĺ–≥–į–ī–į—ā—Ć—Ā—Ź, –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ–į DD2 –≤ –Ľ—é–Ī–ĺ–ľ —Ü–ł–ļ–Ľ–Ķ –ĺ–Ī—Ä–į—Č–Ķ–Ĺ–ł—Ź

(–ļ–į–ļ —á—ā–Ķ–Ĺ–ł—Ź, –ļ–ĺ–≥–ī–į RD=0, —ā–į–ļ –ł –∑–į–Ņ–ł—Ā–ł, –ļ–ĺ–≥–ī–į WR =0) —Ā—Ą–ĺ—Ä–ľ–ł—Ä—É–Ķ—ā –Ĺ—É–Ľ—Ć –Ĺ–į

–≤—Ö–ĺ–ī–į—Ö –ě–ē –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ –ě–ó–£.

–°–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ

–Ņ—Ä–ł —á—ā–Ķ–Ĺ–ł–ł –≤—č–≤–ĺ–ī—č –ī–į–Ĺ–Ĺ—č—Ö –Ņ—Ä–Ķ–≤—Ä–į—Č–į—é—ā—Ā—Ź –≤–ĺ –≤—Ö–ĺ–ī—č, –ł –Ĺ–į –Ĺ–ł—Ö –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –Ĺ–ł—á–Ķ–≥–ĺ –Ĺ–Ķ

–≤—č–≤–ĺ–ī–ł—ā, –į –Ņ–ĺ—Ā–Ľ–Ķ —É—Ā—ā–į–Ĺ–ĺ–≤–ļ–ł –į–ī¬≠—Ä–Ķ—Ā–į –ĺ–Ĺ –Ņ–Ķ—Ä–Ķ–≤–ĺ–ī–ł—ā –≤ 0 —Ā–ł–≥–Ĺ–į–Ľ RD (WR –Ņ—Ä–ł

—ć—ā–ĺ–ľ –ĺ—Ā—ā–į–Ķ—ā—Ā—Ź –≤ 1).

–í

–ļ–į–∂–ī–ĺ–Ļ –ł–∑ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ –Ņ–į–ľ—Ź—ā–ł –Ķ—Ā—ā—Ć —Ā–≤–ĺ—Ź –Ĺ—É–Ľ–Ķ–≤–į—Ź, –Ņ–Ķ—Ä–≤–į—Ź, –≤—ā–ĺ—Ä–į—Ź –ł —ā. –ī. —Ź—á–Ķ–Ļ–ļ–ł,

–≤–Ņ–Ľ–ĺ—ā—Ć –ī–ĺ 2048-–Ļ. –ě–Ī—Ä–į—ā–ł—ā–Ķ –≤–Ĺ–ł–ľ–į–Ĺ–ł–Ķ, —á—ā–ĺ –≤—Ö–ĺ–ī—č –°–ē –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ —Ā–ĺ¬≠–Ķ–ī–ł–Ĺ–Ķ–Ĺ—č —Ā

–≤—č—Ö–ĺ–ī–į–ľ–ł –ī–Ķ—ą–ł—Ą—Ä–į—ā–ĺ—Ä–į DD3, –≤ —á–į—Ā—ā–Ĺ–ĺ—Ā—ā–ł –°–ē DD4 ‚Äď —Ā DD3.15,

–į –°–ē DD5 ‚Äď —Ā DD3.14. –Ě–į –≤—č—Ö–ĺ–ī–Ķ DD3.15 –Ĺ—É–Ľ–Ķ–≤–ĺ–Ļ —Ā–ł–≥–Ĺ–į–Ľ

–≤–ĺ–∑–Ĺ–ł–ļ–Ĺ–Ķ—ā –≤ —ā–ĺ–ľ —Ā–Ľ—É—á–į–Ķ, –ļ–ĺ–≥–ī–į –Ĺ–į —Ā–≤–ĺ–ł—Ö —ā—Ä–Ķ—Ö —Ā—ā–į—Ä—ą–ł—Ö –į–ī—Ä–Ķ—Ā–Ĺ—č—Ö –≤—č¬≠—Ö–ĺ–ī–į—Ö –ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä

—É—Ā—ā–į–Ĺ–ĺ–≤–ł—ā —Ā–Ľ–Ķ–ī—É—é—Č—É—é –ļ–ĺ–ľ–Ī–ł–Ĺ–į—Ü–ł—é —Ā–ł–≥–Ĺ–į¬≠–Ľ–ĺ–≤: –ź15=0, –ź14=0, –ź13=0. –°–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ,

–Ĺ—É–Ľ—Ć –Ĺ–į DD3.14 –Ņ–ĺ—Ź–≤–ł—ā¬≠—Ā—Ź, –Ķ—Ā–Ľ–ł –ź15=0, –ź14=0, –ź13=1. –°–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–ĺ,

—á—ā–ĺ–Ī—č –≤–Ķ—Ā—ā–ł –ĺ–Ī–ľ–Ķ–Ĺ —Ā 84-–Ļ —Ź—á–Ķ–Ļ–ļ–ĺ–Ļ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č DD4, –ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –ī–ĺ–Ľ–∂–Ķ–Ĺ —É—Ā—ā–į¬≠–Ĺ–ĺ–≤–ł—ā—Ć

–Ĺ–į –į–ī—Ä–Ķ—Ā–Ĺ—č—Ö –≤—č—Ö–ĺ–ī–į—Ö –ļ–ĺ–ľ–Ī–ł–Ĺ–į—Ü–ł—é –ź0=–ź1=0; –ź2=1; –ź3=0; –ź4=1; –ź5=0; –ź6=1;

–ź7=–ź8=–ź9=–ź10=–ź13=–ź14=–ź15=0. –ü–ĺ—Ā–ļ–ĺ–Ľ—Ć–ļ—É —É DD4 –ĺ—ā—Ā—É—ā—Ā—ā–≤—É—é—ā –≤—Ö–ĺ–ī—č –ź11 –ł

–ź12, –ł —ć—ā–ł –į–ī—Ä–Ķ—Ā–Ĺ—č–Ķ –Ľ–ł–Ĺ–ł–ł –ļ –Ĺ–Ķ–Ļ –Ĺ–Ķ –Ņ–ĺ–ī–≤–ĺ–ī—Ź—ā—Ā—Ź, —ā–ĺ –ł—Ö —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł–Ķ (–Ĺ—É–Ľ–ł –ł–Ľ–ł –Ķ–ī–ł–Ĺ–ł—Ü—č)

–Ĺ–ł–ļ–į–ļ –Ĺ–Ķ —Ā–ļ–į¬≠–∑—č–≤–į–Ķ—ā—Ā—Ź –Ĺ–į –į–ī—Ä–Ķ—Ā–Ķ –≤—č–Ī–ł—Ä–į–Ķ–ľ–ĺ–Ļ —Ź—á–Ķ–Ļ–ļ–ł –≤ —ć—ā–ĺ–Ļ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ–Ķ. –Ē–Ľ—Ź –ĺ–Ņ¬≠—Ä–Ķ–ī–Ķ–Ľ–Ķ–Ĺ–Ĺ–ĺ—Ā—ā–ł

–Ņ–ĺ–Ľ–ĺ–∂–ł–ľ, —á—ā–ĺ –ł –ĺ–Ĺ–ł –ī–ĺ–Ľ–∂–Ĺ—č –Ī—č—ā—Ć –Ņ—Ä–ł –ĺ–Ī—Ä–į—Č–Ķ–Ĺ–ł–ł –ļ DD4 –Ĺ—É–Ľ–Ķ–≤—č–ľ–ł. –Ę–į–ļ–ł–ľ –ĺ–Ī—Ä–į–∑–ĺ–ľ, –≤

–ł–∑–ĺ–Ī—Ä–į–∂–Ķ–Ĺ–Ĺ–ĺ–Ļ –Ĺ–į —Ä–ł—Ā—É–Ĺ–ļ–Ķ 9 —Ā–ł—Ā—ā–Ķ¬≠–ľ–Ķ –ļ 84-–Ļ —Ź—á–Ķ–Ļ–ļ–Ķ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č DD4

–ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –ĺ–Ī—Ä–į—ā–ł—ā—Ā—Ź, —É—Ā—ā–į–Ĺ–ĺ–≤–ł–≤ –Ĺ–į –į–ī—Ä–Ķ—Ā–Ĺ–ĺ–Ļ —ą–ł–Ĺ–Ķ

0000000001010100–í=0054–Ě=84. –Ē—ėɬ≠–≥–ł–ľ–ł —Ā–Ľ–ĺ–≤–į–ľ–ł, 84-—Ź —Ź—á–Ķ–Ļ–ļ–į –Ņ–į–ľ—Ź—ā–ł –Ĺ–į—ą–Ķ–Ļ —Ā–ł—Ā—ā–Ķ–ľ—č

–Ĺ–į—Ö–ĺ–ī–ł—ā—Ā—Ź –ł–ľ–Ķ–Ŭ≠–Ĺ–ĺ –≤ DD4.

–Ē–Ľ—Ź

–ĺ–Ī—Ä–į—Č–Ķ–Ĺ–ł—Ź –ļ 84-–ĺ–Ļ —Ź—á–Ķ–Ļ–ļ–ł DD5 –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –ī–ĺ–Ľ¬≠–∂–Ķ–Ĺ

—É—Ā—ā–į–Ĺ–ĺ–≤–ł—ā—Ć –Ĺ–į –į–ī—Ä–Ķ—Ā–Ĺ–ĺ–Ļ —ą–ł–Ĺ–Ķ 0010000001010100–í=2054–Ě=8276. –ė–Ĺ–į—á–Ķ –≥–ĺ–≤–ĺ—Ä—Ź, 84-—Ź

—Ź—á–Ķ–Ļ–ļ–į –Ņ–į–ľ—Ź—ā–ł –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č DD5 —Ź–≤–Ľ—Ź–Ķ—ā—Ā—Ź 8276-–Ļ —Ź—á–Ķ–Ļ¬≠–ļ–ĺ–Ļ —Ā–ł—Ā—ā–Ķ–ľ—č

–Ņ–į–ľ—Ź—ā–ł.

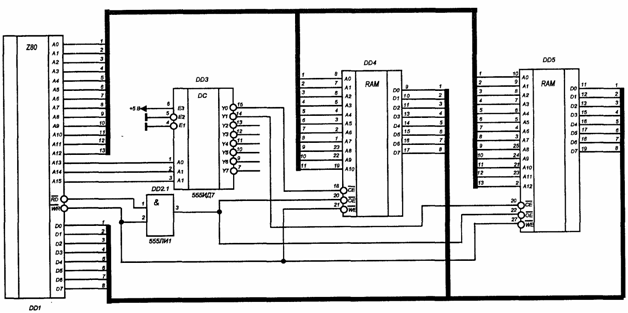

3. –ü—Ä–ł–ľ–Ķ—Ä –Ņ–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł—Ź –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā–ł –Ē–ź–Ě–Ě–ę–•

–ļ –ľ–ł–ļ—Ä–ĺ–ļ—Ä–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä—É —Ā–Ķ–ľ–Ķ–Ļ—Ā—ā–≤–į x51

–õ–ł–Ĺ–ł–ł

–Ņ–ĺ—Ä—ā–į –†2 –ľ–ł–ļ—Ä–ĺ–ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–į –Ņ—Ä–ł –ĺ–Ī¬≠—Ä–į—Č–Ķ–Ĺ–ł–ł –ļ –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā–ł –≤—č–≤–ĺ–ī—Ź—ā –į–ī—Ä–Ķ—Ā–Ĺ—č–Ķ –Ī–ł—ā—č

–ź8-–ź15. –Ē–į–Ľ–Ķ–Ķ, —Ā–ł–≥–Ĺ–į–Ľ —Ą–ĺ—Ä–ľ–ł—Ä—É–Ķ—ā—Ā—Ź –Ĺ–į –†3.7, a ‚Äď –Ĺ–į –†3.6.

–õ–ł–Ĺ–ł–ł

–Ņ–ĺ—Ä—ā–į –†0 –Ņ—Ä–Ķ–ī—Ā—ā–į–≤–Ľ—Ź—é—ā –ľ—É–Ľ—Ć—ā–ł–Ņ–Ľ–Ķ–ļ—Ā–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—É—é –≤–ĺ –≤—Ä–Ķ–ľ–Ķ–Ĺ–ł —ą–ł–Ĺ—É –į–ī—Ä–Ķ—Ā–į/–ī–į–Ĺ–Ĺ—č—Ö. –Ę.–Ķ.

–Ľ–ł–Ĺ–ł–ł P0 –ł—Ā–Ņ–ĺ–Ľ—Ƭ≠–∑—É—é—ā—Ā—Ź –ī–Ľ—Ź –≤–≤–ĺ–ī–į/–≤—č–≤–ĺ–ī–į –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł —Ā —ą–ł–Ĺ—č –ī–į–Ĺ–Ĺ—č—Ö.

–Ě–ĺ, –ļ—Ä–ĺ–ľ–Ķ —ā–ĺ–≥–ĺ, –≤ –Ņ–Ķ—Ä–≤—č–Ļ –ľ–ĺ–ľ–Ķ–Ĺ—ā –ĺ–Ī—Ä–į—Č–Ķ–Ĺ–ł—Ź –ļ –Ņ–į–ľ—Ź—ā–ł –Ņ–ĺ —ć—ā–ł–ľ –∂–Ķ –Ľ–ł–Ĺ–ł—Ź–ľ –≤—č–≤–ĺ–ī—Ź—ā—Ā—Ź

–į–ī—Ä–Ķ—Ā–į –ź0...–ź7, –ł –ĺ–ī–Ĺ–ĺ–≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ–ĺ —Ā —ć—ā–ł–ľ —É—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā—Ā—Ź –≤ 1 —Ā–ł–≥–Ĺ–į–Ľ –Ĺ–į –≤—č—Ö–ĺ–ī–Ķ ALE

(–į–ī—Ä–Ķ—Ā–į —Ā—ā—Ä–ĺ–Ī–ł—Ä—É—é—ā—Ā—Ź —Ā–ł–≥–Ĺ–į–Ľ–ĺ–ľ ALE). –°–Ņ—É—Ā—ā—Ź 2 –Ņ–Ķ—Ä–ł–ĺ–ī–į

—ā–į–ļ—ā–ĺ–≤–ĺ–≥–ĺ –≥–Ķ–Ĺ–Ķ—Ä–į—ā–ĺ—Ä–į ALE —Ā–Ī—Ä–į—Ā—č–≤–į–Ķ—ā—Ā—Ź –≤ 0, –ł —á–Ķ—Ä–Ķ–∑ –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ –Ĺ–į–Ĺ–ĺ—Ā–Ķ–ļ—É–Ĺ–ī –Ņ–ĺ—Ā–Ľ–Ķ

—ć—ā–ĺ–≥–ĺ –į–ī—Ä–Ķ—Ā–Ĺ–į—Ź –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł—Ź –Ņ—Ä–ĺ–Ņ–į–ī–į–Ķ—ā —Ā –Ľ–ł–Ĺ–ł–Ļ –Ņ–ĺ—Ä—ā–į –†0, –ī–į–≤–į—Ź –≤–ĺ–∑–ľ–ĺ–∂–Ĺ–ĺ—Ā—ā—Ć –≤–Ķ—Ā—ā–ł

–Ņ–ĺ –Ĺ–ł–ľ –ĺ–Ī–ľ–Ķ–Ĺ –ī–į–Ĺ–Ĺ—č–ľ–ł. –ź –ī–Ľ—Ź —ā–ĺ–≥–ĺ, —á—ā–ĺ–Ī—č –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į—ā—Ć –į–ī—Ä–Ķ—Ā–į –ź0-–ź7, –Ņ—Ä–ł–ľ–Ķ–Ĺ—Ź—é—ā

8-—Ä–į–∑—Ä—Ź–ī–Ĺ—č–Ļ —Ä–Ķ–≥–ł—Ā—ā—Ä-–∑–į—Č–Ķ–Ľ–ļ—É —ā–ł–Ņ–į 555–ė–†22, –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł—Ź –≤ –ļ–ĺ—ā–ĺ—Ä–ĺ–ľ —Ą–ł–ļ—Ā–ł—Ä—É–Ķ—ā—Ā—Ź –Ņ–ĺ

—Ā–Ņ–į–ī—É —Ā–ł–≥–Ĺ–į–Ľ–į –Ĺ–į –Ķ–≥–ĺ –≤—Ö–ĺ–ī–Ķ STB. –í –ļ–į—á–Ķ—Ā—ā–≤–Ķ —ć—ā–ĺ–≥–ĺ —Ā–ł–≥¬≠–Ĺ–į–Ľ–į,

–ļ–į–ļ –Ĺ–Ķ—ā—Ä—É–ī–Ĺ–ĺ –ī–ĺ–≥–į–ī–į—ā—Ć—Ā—Ź, –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ—ā—Ā—Ź —Ā–ł–≥–Ĺ–į–Ľ ALE (—ć—ā–ĺ –ĺ—Ā–Ĺ–ĺ–≤–Ĺ–ĺ–Ķ –Ķ–≥–ĺ

–Ĺ–į–∑–Ĺ–į—á–Ķ–Ĺ–ł–Ķ). –°–ļ–į–∑–į–Ĺ–Ĺ–ĺ–Ķ –ł–Ľ–Ľ—é—Ā—ā—Ä–ł—Ä—É–Ķ—ā—Ā—Ź –Ĺ–į —Ä–ł—Ā—É–Ĺ–ļ–Ķ 10.

–†–ł—Ā.

10. ¬†–ü–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł–Ķ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ –Ņ–į–ľ—Ź—ā–ł –ļ

–ľ–ł–ļ—Ä–ĺ–ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä—É —Ā–Ķ–ľ–Ķ–Ļ—Ā—ā–≤–į —Ö51

–Ę–į–ļ–ł–ľ

–ĺ–Ī—Ä–į–∑–ĺ–ľ, —Ä–į–Ī–ĺ—ā–į –ú–ö —Ā –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā—Ć—é –ī–į–Ĺ–Ĺ—č—Ö –ĺ—Ā—É—Č–Ķ¬≠—Ā—ā–≤–Ľ—Ź–Ķ—ā—Ā—Ź —Ā–Ľ–Ķ–ī—É—é—Č–ł–ľ –ĺ–Ī—Ä–į–∑–ĺ–ľ.

–ü—Ä–ĺ—á–ł—ā–į–≤ –ļ–ĺ–ľ–į–Ĺ–ī—É –ĺ–Ī—Ä–į—Č–Ķ–Ĺ–ł—Ź –ļ –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā–ł, –ľ–ł–ļ—Ä–ĺ–ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä –≤—č¬≠–≤–ĺ–ī–ł—ā –Ņ–ĺ –Ľ–ł–Ĺ–ł—Ź–ľ

–Ņ–ĺ—Ä—ā–į –†2 —Ā—ā–į—Ä—ą–ł–Ķ 8 –Ī–ł—ā –į–ī—Ä–Ķ—Ā–į, –į –Ņ–ĺ –Ľ–ł–Ĺ–ł—Ź–ľ –†0 ‚Äď –ľ–Ľ–į–ī—ą–ł–Ķ. –ě–ī–Ĺ–ĺ–≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ–ĺ —Ā —ć—ā–ł–ľ –ĺ–Ĺ

—É—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā –≤ 1 —Ā–ł–≥–Ĺ–į–Ľ –Ĺ–į –≤—č¬≠—Ö–ĺ–ī–Ķ ALE. –ö–ĺ–≥–ī–į —ć—ā–į 1 –Ņ–ĺ—Ā—ā—É–Ņ–į–Ķ—ā –Ĺ–į

–≤—Ö–ĺ–ī STB —Ä–Ķ–≥–ł—Ā—ā—Ä–į-–∑–į—Č–Ķ–Ľ–ļ–ł DD3, –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł—Ź —Ā –Ķ–≥–ĺ –≤—Ö–ĺ–ī–ĺ–≤ D0-D7

–Ĺ–į–Ņ—Ä—Ź–ľ—É—é –Ņ–ĺ—Ā—ā—É–Ņ–į–Ķ—ā –Ĺ–į –≤—č—Ö–ĺ–ī—č Q0- Q7, —Ā–ĺ–Ķ–ī–ł–Ĺ–Ķ–Ĺ–Ĺ—č–Ķ —Ā –ľ–Ľ–į–ī—ą–ł–ľ–ł 8

–Ľ–ł–Ĺ–ł—Ź–ľ–ł —ą–ł–Ĺ—č –į–ī—Ä–Ķ—Ā–į. –°–Ņ—É—Ā—ā—Ź –Ĺ–Ķ–ļ–ĺ¬≠—ā–ĺ—Ä–ĺ–Ķ –≤—Ä–Ķ–ľ—Ź ALE —É—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā—Ā—Ź –≤ 0. –ü–Ķ—Ä–Ķ–Ņ–į–ī

–ł–∑ 1 –≤ 0 –Ĺ–į –≤—Ö–ĺ–ī–Ķ STB DD3 –Ņ—Ä–ł–≤–ĺ–ī–ł—ā –ļ –∑–į—Č–Ķ–Ľ–ļ–ł–≤–į–Ĺ–ł—é –≤

—Ä–Ķ–≥–ł—Ā—ā—Ä–į—Ö –≤—č—Ö–ĺ–ī–ĺ–≤ Q0-Q7 –Ņ–ĺ—Ā—ā—ɬ≠–Ņ–į—é—Č–Ķ–Ļ –Ĺ–į –Ĺ–ł—Ö

–ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł, –ł –∑–į—Č–Ķ–Ľ–ļ–Ĺ—É—ā—č–Ķ –ľ–Ľ–į–ī—ą–ł–Ķ 8 –Ī–ł—ā –į–ī—Ä–Ķ—Ā–į –ĺ—Ā—ā–į—é—ā—Ā—Ź –Ĺ–Ķ–ł–∑–ľ–Ķ–Ĺ–Ĺ—č–ľ–ł –Ĺ–į –≤—č—Ö–ĺ–ī–į—Ö Q0-Q7 –ī–ĺ

—Ā–Ľ–Ķ–ī—É—é—Č–Ķ–≥–ĺ —Ü–ł–ļ–Ľ–į –ĺ–Ī¬≠–ľ–Ķ–Ĺ–į —Ā –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā—Ć—é. –°—ā–į—Ä—ą–ł–Ķ 8 –Ī–ł—ā, –≤—č–≤–ĺ–ī–ł–ľ—č–Ķ —á–Ķ—Ä–Ķ–∑ –†2,

—ā–į–ļ–∂–Ķ –Ĺ–Ķ –ľ–Ķ–Ĺ—Ź—é—ā—Ā—Ź –ī–ĺ –∑–į–≤–Ķ—Ä—ą–Ķ–Ĺ–ł—Ź —ā–Ķ–ļ—É—Č–Ķ–≥–ĺ —Ü–ł–ļ–Ľ–į —Ä–į–Ī–ĺ—ā—č —Ā –≤–Ĺ–Ķ—ą–Ĺ–ł–ľ –ě–ó–£.

–ü–ĺ—Ā–ļ–ĺ–Ľ—Ć–ļ—É

–ź0-–ź7 –∑–į–Ņ–ĺ–ľ–Ĺ–Ķ–Ĺ—č –≤ —Ä–Ķ–≥–ł—Ā—ā—Ä–Ķ-–∑–į—Č–Ķ–Ľ–ļ–Ķ, –ĺ–Ĺ–ł —Ā–Ĺ–ł–ľ–į—é—ā—Ā—Ź —Ā –≤—č–≤–ĺ–ī–ĺ–≤ –Ņ–ĺ—Ä—ā–į –†0, –ł

–Ņ–ĺ—Ā–Ľ–Ķ–ī–Ĺ–ł–Ķ –Ņ—Ä–Ķ–≤—Ä–į—Č–į—é—ā—Ā—Ź –≤ –≤—č–≤–ĺ–ī—č —ą–ł–Ĺ—č –ī–į–Ŭ≠–Ĺ—č—Ö. –ē—Ā–Ľ–ł –ú–ö –∑–į–Ņ–ł—Ā—č–≤–į–Ķ—ā –ī–į–Ĺ–Ĺ—č–Ķ –≤–ĺ

–≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ķ –ě–ó–£, –∑–į–Ņ–ł—Ā—č–≤–į–Ķ–ľ—č–Ļ –Ī–į–Ļ—ā –≤—č–≤–ĺ–ī–ł—ā—Ā—Ź –ł–ľ –Ĺ–į –†0.0-–†0.7, –ł —É—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā—Ā—Ź –≤ 0

—Ā–ł–≥–Ĺ–į–Ľ –Ĺ–į –Ķ–≥–ĺ –≤—č—Ö–ĺ–ī–Ķ WR (–†–ó.6). –ü–ĺ—Ź–≤–Ľ–Ķ–Ĺ–ł–Ķ –∂–Ķ –Ĺ—É–Ľ–Ķ–≤—č—Ö —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ –Ĺ–į –≤—Ö–ĺ–ī–į—Ö WE –ł –ě–ē,

—Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–Ķ–Ļ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č –Ņ–į–ľ—Ź—ā–ł –Ņ—Ä–ł–≤–ĺ–ī–ł—ā –ļ –∑–į–Ņ–ł—Ā–ł –≤ –Ĺ–Ķ–Ķ –Ī–į–Ļ—ā–į, –Ņ–ĺ–ī–į–Ĺ–Ĺ–ĺ–≥–ĺ –Ĺ–į

–Ķ–Ķ –≤—Ö–ĺ–ī—č D0-D7. –Ě—É–Ľ–Ķ–≤–ĺ–Ļ —Ā–ł–≥–Ĺ–į–Ľ –Ĺ–į –ě–ē, —Ą–ĺ—Ä–ľ–ł—Ä—É–Ķ—ā –ľ–ł–ļ—Ä–ĺ¬≠—Ā—Ö–Ķ–ľ–į DD2.

–°–ļ–į–∑–į–Ĺ–Ĺ–ĺ–Ķ –ł–Ľ–Ľ—é—Ā—ā—Ä–ł—Ä—É–Ķ—ā—Ā—Ź –≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ—č–ľ–ł –ī–ł–į–≥—Ä–į–ľ–ľ–į–ľ–ł –Ĺ–į —Ä–ł—Ā—É–Ĺ–ļ–Ķ 11.

–†–ł—Ā. 11. –í—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ—č–Ķ –ī–ł–į–≥—Ä–į–ľ–ľ—č —Ü–ł–ļ–Ľ–ĺ–≤ –ĺ–Ī–ľ–Ķ–Ĺ–į –ú–ö —Ā –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ

–Ņ–į–ľ—Ź—ā—Ć—é –ī–į–Ĺ–Ĺ—č—Ö

–í

–ĺ—ā–Ľ–ł—á–ł–Ķ –ĺ—ā —Ā—Ö–Ķ¬≠–ľ—č –Ĺ–į —Ä–ł—Ā—É–Ĺ–ļ–Ķ 9 –≤ —Ā—Ö–Ķ–ľ–Ķ –Ĺ–į —Ä–ł—Ā—É–Ĺ–ļ–Ķ 10 –ĺ—ā—Ā—É—ā—Ā—ā–≤—É–Ķ—ā –ī–Ķ—ą–ł—Ą—Ä–į—ā–ĺ—Ä,

—É–Ņ—Ä–į–≤–Ľ—Ź–≤¬≠—ą–ł–Ļ—Ā—Ź –į–ī—Ä–Ķ—Ā–į–ľ–ł –ź13-–ź15. –í–ľ–Ķ—Ā—ā–ĺ —ć—ā–ĺ–≥–ĺ –Ĺ–į –≤—Ö–ĺ–ī—č –°–ē –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ –Ņ–į¬≠–ľ—Ź—ā–ł

–Ņ–ĺ–ī–į–Ĺ—č —Ā–ł–≥–Ĺ–į–Ľ—č —Ā –ź13 –ł –ź14. –Ę–į–ļ–ĺ–Ķ —Ä–Ķ—ą–Ķ–Ĺ–ł–Ķ –≤–ĺ–∑–ľ–ĺ–∂–Ĺ–ĺ, –Ķ—Ā–Ľ–ł –≤—č —ā–ĺ—á–Ĺ–ĺ –∑–Ĺ–į–Ķ—ā–Ķ, —á—ā–ĺ –≤

–≤–į—ą–Ķ–Ļ —Ā–ł—Ā—ā–Ķ–ľ–Ķ –Ĺ–Ķ –Ī—É–ī–Ķ—ā –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į—ā—Ć—Ā—Ź –Ī–ĺ–Ľ–Ķ–Ķ —ā—Ä–Ķ—Ö –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā–ł

(–ī–Ķ—ą–ł—Ą—Ä–į—ā–ĺ—Ä DD3 –Ĺ–į —Ä–ł—Ā—É–Ĺ–ļ–Ķ 9 –Ņ–ĺ–∑–≤–ĺ–Ľ—Ź–Ľ —Ä–į–Ī–ĺ—ā–į—ā—Ć —Ā 8-—é –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ–į–ľ–ł).

–ü—Ä–ł –ĺ–Ī—Ä–į—Č–Ķ–Ĺ–ł–ł –ļ DD4 –ú–ö –ī–ĺ–Ľ–∂–Ķ–Ĺ —É—Ā—ā–į–Ĺ–ĺ–≤–ł—ā—Ć —Ā–Ľ–Ķ–ī—É—é—Č—É—é –ļ–ĺ–ľ–Ī–ł–Ĺ–į—Ü–ł—é —Ā—ā–į—Ä—ą–ł—Ö

–į–ī—Ä–Ķ—Ā–ĺ–≤: –ź13=0, –ź14=–ź15=1. –°–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ –ī–Ľ—Ź DD5 –ź13= 1, –ź14=0, –ź15= 1. –ź

–ļ–į–ļ–į—Ź –ļ–ĺ–ľ–Ī–ł–Ĺ–į—Ü–ł—Ź –Ņ–ĺ—ā—Ä–Ķ–Ī–ĺ–≤–į–Ľ–į—Ā—Ć –Ī—č –ī–Ľ—Ź 3-–Ļ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č, –Ķ—Ā–Ľ–ł –Ķ–Ķ –≤—Ö–ĺ–ī –°–ē —Ā–ĺ–Ķ–ī–ł–Ĺ–ł—ā—Ć

—Ā –ź15?

–ü—Ä–ĺ—Ü–Ķ—Ā—Ā

—á—ā–Ķ–Ĺ–ł—Ź –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł –ľ–ł–ļ—Ä–ĺ–ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–ĺ–ľ –į–Ĺ–į–Ľ–ĺ–≥–ł—á–Ķ–Ĺ —ā–ĺ–Ľ—Ć–ļ–ĺ —á—ā–ĺ —Ä–į—Ā—Ā–ľ–ĺ—ā—Ä–Ķ–Ĺ–Ĺ–ĺ–ľ—É

–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā—É –∑–į–Ņ–ł—Ā–ł —Ā —ā–ĺ–Ļ –Ľ–ł—ą—Ć —Ä–į–∑–Ĺ–ł—Ü–Ķ–Ļ, —á—ā–ĺ –ú–ö —É—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā –≤ 0 –Ĺ–Ķ WR , a RD, –ł –ī–į–Ĺ–Ĺ—č–Ķ –Ĺ–į —ą–ł–Ĺ—É –ī–į–Ĺ–Ĺ—č—Ö –Ņ–ĺ—Ā—ā—É–Ņ–į—é—ā –Ĺ–Ķ —Ā –Ĺ–Ķ–≥–ĺ, –į —Ā

—Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–Ķ–Ļ –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č –Ņ–į–ľ—Ź—ā–ł.

–ě–Ņ–ł—Ā–į–Ĺ–Ĺ—č–Ļ

—Ā–Ņ–ĺ—Ā–ĺ–Ī –≤—č–ī–į—á–ł –į–ī—Ä–Ķ—Ā–Ĺ–ĺ–Ļ –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł –Ņ–ĺ –≤—č–≤–ĺ–ī–į–ľ —ą–ł–Ĺ—č –ī–į–Ĺ–Ĺ—č—Ö –ĺ—á–Ķ–Ĺ—Ć —Ä–į—Ā–Ņ—Ä–ĺ—Ā—ā—Ä–į–Ĺ–Ķ–Ĺ

(–ĺ–Ĺ –Ņ—Ä–ł–ľ–Ķ–Ĺ—Ź–Ľ—Ā—Ź, –Ĺ–į–Ņ—Ä–ł–ľ–Ķ—Ä, –≤ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į—Ö 8086/8088, –Ĺ–į –ļ–ĺ—ā–ĺ—Ä—č—Ö –Ī—č–Ľ–ł –≤—č–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ—č

–Ņ–Ķ—Ä–≤—č–Ķ IBM PC), –ł –Ĺ–į–∑—č–≤–į–Ķ—ā—Ā—Ź

–ľ—É–Ľ—Ć—ā–ł–Ņ–Ľ–Ķ–ļ—Ā–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ–ľ —ą–ł–Ĺ –į–ī—Ä–Ķ—Ā–į/–ī–į–Ĺ–Ĺ—č—Ö.

4. –ü–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł—Ź –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā–ł –ü–†–ě–ď–†–ź–ú–ú

–ļ –ľ–ł–ļ—Ä–ĺ–ļ—Ä–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä—É —Ā–Ķ–ľ–Ķ–Ļ—Ā—ā–≤–į x51

–ú–ł–ļ—Ä–ĺ–ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä—č

—Ā–Ķ–ľ–Ķ–Ļ—Ā—ā–≤–į —Ö51 –ī–ĺ–Ņ—É—Ā–ļ–į—é—ā —Ä–į–Ī–ĺ—ā—É —Ā –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ –Ņ–į–ľ—Ź—ā—Ć—é –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ, –≤ –ļ–į—á–Ķ—Ā—ā–≤–Ķ –ļ–ĺ—ā–ĺ—Ä–ĺ–Ļ

–≤—č—Ā—ā—É–Ņ–į—é—ā –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č –ü–ó–£ –ĺ–Ī—ä–Ķ–ľ–ĺ–ľ –ī–ĺ 64 –ļ–Ī–į–Ļ—ā. –ė—Ö –Ņ–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł–Ķ –ł —Ä–į–Ī–ĺ—ā–į

–į–Ĺ–į–Ľ–ĺ–≥–ł—á–Ĺ—č –Ņ–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł—é –ł —Ä–į–Ī–ĺ—ā–Ķ –≤ —Ä–Ķ–∂–ł–ľ–Ķ —á—ā–Ķ–Ĺ–ł—Ź –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ –Ņ–į–ľ—Ź—ā–ł –ī–į–Ĺ–Ĺ—č—Ö –ě–ó–£. –í

–ļ–į—á–Ķ—Ā—ā–≤–Ķ —Ā–ł–≥–Ĺ–į–Ľ–į —á—ā–Ķ–Ĺ–ł—Ź –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ—ā—Ā—Ź —Ā–ł–≥–Ĺ–į–Ľ –≤—č–≤–ĺ–ī–į –≤–ľ–Ķ—Ā—ā–ĺ —Ā–ł–≥–Ĺ–į–Ľ–į.