БазРҫРІСӢРө СҚР»РөРјРөРҪСӮСӢ СҒСӮСҖСғРәСӮСғСҖСӢ РңРҹ

(РӣРөРәСҶРёСҸ)

РҹРӣРҗРқ РӣР•РҡРҰРҳРҳ

1. РӣРҫРіРёСҮРөСҒРәРёРө СҚР»РөРјРөРҪСӮСӢ

2. РЎСғРјРјР°СӮРҫСҖСӢ

3. Р”РөРәРҫРҙРөСҖСӢ

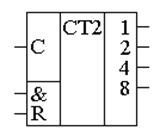

4. Р”РөСҒСҸСӮРёСҮРҪСӢР№ РҙРөСҲРёС„СҖР°СӮРҫСҖ

5. РҡРҫРҙРөСҖСӢ

6. РңСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖСӢ

7. Р”РөРјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖСӢ

8. РҰРЎ РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫСҒСӮРҪРҫРіРҫ

СӮРёРҝР° (авСӮРҫРјР°СӮСӢ СҒ РҝамСҸСӮСҢСҺ)

9. РЎСҮС‘СӮСҮРёРәРё

РҹРҫРҪРёРјР°РҪРёРө СҒСӮСҖСғРәСӮСғСҖСӢ РңРҹ РҪРө

РјРҫР¶РөСӮ РҝСҖРёР№СӮРё РұРөР· РҝРҫРҪРёРјР°РҪРёСҸ Р·Р°РәРҫРҪРҫРІ С„СғРҪРәСҶРёРҫРҪРёСҖРҫРІР°РҪРёСҸ РұазРҫРІСӢС… СҶРёС„СҖРҫРІСӢС… СғСҒСӮСҖРҫР№СҒСӮРІ,

РІС…РҫРҙСҸСүРёС… РІ РөРіРҫ СҒСӮСҖСғРәСӮСғСҖСғ, СҖР°СҒСҒРјРҫСӮСҖРёРј СҒР»РөРҙСғСҺСүРёРө РөРө РҫСҒРҪРҫРІРҪСӢРө СҚР»РөРјРөРҪСӮСӢ.

1. РӣРҫРіРёСҮРөСҒРәРёРө СҚР»РөРјРөРҪСӮСӢ

РӣСҺРұСӢРө РҰРң СҒСӮСҖРҫСҸСӮСҒСҸ РҪР° РҫСҒРҪРҫРІРө

РҝСҖРҫСҒСӮРөР№СҲРёС… Р»РҫРіРёСҮРөСҒРәРёС… СҚР»РөРјРөРҪСӮРҫРІ:

1. "РқР•" - РІСӢРҝРҫР»РҪСҸРөСӮ С„СғРҪРәСҶРёСҺ

РёРҪРІРөСҖСӮРёСҖРҫРІР°РҪРёСҸ. РӣРҫРіРёСҮРөСҒРәРҫРө РҫСӮСҖРёСҶР°РҪРёРө

(РёРҪРІРөСҖСҒРёСҸ) РҫРұРҫР·РҪР°СҮР°РөСӮСҒСҸ СҮРөСҖСӮРҫР№ РҪР°Рҙ РҫРұРҫР·РҪР°СҮРөРҪРёРөРј Р°СҖРіСғРјРөРҪСӮР°.

РңРҫРҙРөР»СҢСҺ, СҖРөализСғСҺСүРөР№ С„СғРҪРәСҶРёСҺ РқР•, РјРҫР¶РөСӮ СҒР»СғжиСӮСҢ СҖазмСӢРәР°СҺСүРёР№ РәРҫРҪСӮР°РәСӮ СҖРөР»Рө. РҹСҖРё

СҒСҖР°РұР°СӮСӢРІР°РҪРёРё СҖРөР»Рө СҶРөРҝСҢ, РІ РәРҫСӮРҫСҖСғСҺ РІС…РҫРҙРёСӮ СӮР°РәРҫР№ РәРҫРҪСӮР°РәСӮ, РұСғРҙРөСӮ СҖазмСӢРәР°СӮСҢСҒСҸ. РҳРҪРІРөСҖСҒРёСҸ 1 СҖавРҪР° 0, РёРҪРІРөСҖСҒРёСҸ 0 - 1, Р° РҙРІРҫР№РҪР°СҸ РёРҪРІРөСҖСҒРёСҸ РҪРө РёР·РјРөРҪСҸРөСӮ

Р·РҪР°СҮРөРҪРёСҸ.

2. "Рҳ" - РІСӢРҝРҫР»РҪСҸРөСӮ С„СғРҪРәСҶРёСҺ

Р»РҫРіРёСҮРөСҒРәРҫРіРҫ СғРјРҪРҫР¶РөРҪРёСҸ. РӣРҫРіРёСҮРөСҒРәРҫРө СғРјРҪРҫР¶РөРҪРёРө (РәРҫРҪСҠСҺРҪРәСҶРёСҸ)

РҫРұРҫР·РҪР°СҮР°РөСӮСҒСҸ СӮРҫСҮРәРҫР№ или СҒРёРјРІРҫР»РҫРј ^ лиРұРҫ РІРҫРҫРұСүРө РІ РұСғРәРІРөРҪРҪСӢС… РІСӢСҖажРөРҪРёСҸС… РҪРёРәР°Рә РҪРө

РҫРұРҫР·РҪР°СҮР°РөСӮСҒСҸ. РӨСғРҪРәСҶРёСҺ Рҳ СҖРөализСғСҺСӮ СҒРҫРөРҙРёРҪРөРҪРҪСӢРө РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫ замСӢРәР°СҺСүРёРө

РәРҫРҪСӮР°РәСӮСӢ РҪРөСҒРәРҫР»СҢРәРёС… СҖРөР»Рө.

3.

"РҳРӣРҳ"

- РІСӢРҝРҫР»РҪСҸРөСӮ С„СғРҪРәСҶРёСҺ Р»РҫРіРёСҮРөСҒРәРҫРіРҫ СҒСғРјРјРёСҖРҫРІР°РҪРёСҸ. РӣРҫРіРёСҮРөСҒРәРҫРө СҒР»РҫР¶РөРҪРёРө

(РҙРёР·СҠСҺРҪРәСҶРёСҸ) РҫРұРҫР·РҪР°СҮР°РөСӮСҒСҸ "+" или V (РҝРөСҖРІР°СҸ РұСғРәРІР°

лаСӮРёРҪСҒРәРҫРіРҫ СҒР»РҫРІР° vel-или). Р’ РәР°СҮРөСҒСӮРІРө РҝСҖРёРјРөСҖР° РјРҫР¶РҪРҫ РҝСҖРёРІРөСҒСӮРё РҝР°СҖаллРөР»СҢРҪРҫРө СҒРҫРөРҙРёРҪРөРҪРёРө

замСӢРәР°СҺСүРёС… РәРҫРҪСӮР°РәСӮРҫРІ РҪРөСҒРәРҫР»СҢРәРёС… СҖРөР»Рө. РҰРөРҝСҢ, РІ РәРҫСӮРҫСҖСғСҺ РІС…РҫРҙСҸСӮ СҚСӮРё РәРҫРҪСӮР°РәСӮСӢ,

РұСғРҙРөСӮ замРәРҪСғСӮР°, РөСҒли СҒСҖР°РұРҫСӮР°РөСӮ С…РҫСӮСҸ РұСӢ РҫРҙРҪРҫ.

РҗРҪализ Рё СҒРёРҪСӮРөР·

Р»РҫРіРёСҮРөСҒРәРёС… СҶРөРҝРөР№ РҝСҖРҫРёР·РІРҫРҙРёСӮСҒСҸ РҪР° РҫСҒРҪРҫРІРө РјР°СӮРөРјР°СӮРёСҮРөСҒРәРҫРіРҫ Р°РҝРҝР°СҖР°СӮР° алгРөРұСҖСӢ Р»РҫРіРёРәРё,

или РұСғР»РөРІРҫР№ алгРөРұСҖСӢ. РҹРөСҖРөРјРөРҪРҪСӢРө РјРҫРіСғСӮ РҝСҖРёРҪРёРјР°СӮСҢ 0 или 1. РқР°Рҙ РҝРөСҖРөРјРөРҪРҪСӢРјРё РјРҫРіСғСӮ

РҝСҖРҫРёР·РІРҫРҙРёСӮСҢСҒСҸ СӮСҖРё РҫСҒРҪРҫРІРҪСӢС… РҙРөР№СҒСӮРІРёСҸ: Р»РҫРіРёСҮРөСҒРәРҫРө СҒР»РҫР¶РөРҪРёРө, СғРјРҪРҫР¶РөРҪРёРө Рё РҫСӮСҖРёСҶР°РҪРёРө,

СҮСӮРҫ СҒРҫРҫСӮРІРөСӮСҒСӮРІСғРөСӮ С„СғРҪРәСҶРёСҸРј РҳРӣРҳ, Рҳ, РқР•. РһРұРҫР·РҪР°СҮРөРҪРёСҸ СҚСӮРёС… СҚР»РөРјРөРҪСӮРҫРІ РҪР° СҒС…Рөмах

РҝСҖРёРІРөРҙРөРҪРҫ

2. РЎСғРјРјР°СӮРҫСҖСӢ

РҹРҫСҒСӮСҖРҫРөРҪРёРө

РҙРІРҫРёСҮРҪСӢС… СҒСғРјРјР°СӮРҫСҖРҫРІ РҫРұСӢСҮРҪРҫ РҪР°СҮРёРҪР°РөСӮСҒСҸ СҒ СҒСғРјРјР°СӮРҫСҖР° РҝРҫ РјРҫРҙСғР»СҺ 2.

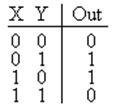

Р РёСҒ. РЎСғРјРјР°СӮРҫСҖ РҝРҫ РјРҫРҙСғР»СҺ 2.

РЎСғРјРјР°СӮРҫСҖ РҝРҫ

РјРҫРҙСғР»СҺ 2 РІСӢРҝРҫР»РҪСҸРөСӮ СҒСғРјРјРёСҖРҫРІР°РҪРёРө РұРөР· СғСҮРөСӮР° РҝРөСҖРөРҪРҫСҒР°. Р’ РҝРҫР»РҪРҫРј РҙРІРҫРёСҮРҪРҫРј СҒСғРјРјР°СӮРҫСҖРө

СӮСҖРөРұСғРөСӮСҒСҸ СғСҮРёСӮСӢРІР°СӮСҢ РҝРөСҖРөРҪРҫСҒ РІ СҒР»РөРҙСғСҺСүРёР№ СҖазСҖСҸРҙ.

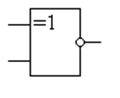

Р РёСҒ. РҹРҫР»СғСҒСғРјРјР°СӮРҫСҖ

РЎС…РөРјР°

РҝРҫР»СғСҒСғРјРјР°СӮРҫСҖР° С„РҫСҖРјРёСҖСғРөСӮ РҝРөСҖРөРҪРҫСҒ РІ СҒР»РөРҙСғСҺСүРёР№ СҖазСҖСҸРҙ, РҪРҫ РҪРө РјРҫР¶РөСӮ СғСҮРёСӮСӢРІР°СӮСҢ

РҝРөСҖРөРҪРҫСҒ РёР· РҝСҖРөРҙСӢРҙСғСүРөРіРҫ СҖазСҖСҸРҙР°, РҝРҫСҚСӮРҫРјСғ РҫРҪР° Рё РҪазСӢРІР°РөСӮСҒСҸ РҝРҫР»СғСҒСғРјРјР°СӮРҫСҖРҫРј. Р’

РҫРұРҫР·РҪР°СҮРөРҪРёРё РІС…РҫРҙРҫРІ: РІ РәР°СҮРөСҒСӮРІРө РІС…РҫРҙРҫРІ РёСҒРҝРҫР»СҢР·РҫРІР°РҪСӢ РҫРҙРҪРҫСҖазСҖСҸРҙРҪСӢРө СҮРёСҒла A Рё B;

РҝРөСҖРөРҪРҫСҒ РҫРұРҫР·РҪР°СҮРөРҪ P; РҙР»СҸ РҫРұРҫР·РҪР°СҮРөРҪРёСҸ РІС…РҫРҙР° РҝРөСҖРөРҪРҫСҒР° I (РҫСӮ Р°РҪглийСҒРәРҫРіРҫ input вҖ“

РІС…РҫРҙ); РҙР»СҸ РҫРұРҫР·РҪР°СҮРөРҪРёСҸ РІСӢС…РҫРҙР° РҝРөСҖРөРҪРҫСҒР° O (РҫСӮ Р°РҪглийСҒРәРҫРіРҫ output вҖ“ РІСӢС…РҫРҙ).

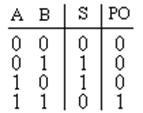

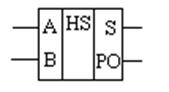

Р РёСҒ. РҹРҫР»РҪСӢР№ РҙРІРҫРёСҮРҪСӢР№ РҫРҙРҪРҫСҖазСҖСҸРҙРҪСӢР№ СҒСғРјРјР°СӮРҫСҖ

ДлСҸ СӮРҫРіРҫ СҮСӮРҫРұСӢ РҝРҫР»СғСҮРёСӮСҢ РјРҪРҫРіРҫСҖазСҖСҸРҙРҪСӢР№

СҒСғРјРјР°СӮРҫСҖ, РҙРҫСҒСӮР°СӮРҫСҮРҪРҫ СҒРҫРөРҙРёРҪРёСӮСҢ РІС…РҫРҙСӢ Рё РІСӢС…РҫРҙСӢ РҝРөСҖРөРҪРҫСҒРҫРІ СҒРҫРҫСӮРІРөСӮСҒСӮРІСғСҺСүРёС…

РҙРІРҫРёСҮРҪСӢС… СҖазСҖСҸРҙРҫРІ.

Р РёСҒ. РҹРҫР»РҪСӢР№ РҙРІРҫРёСҮРҪСӢР№ РјРҪРҫРіРҫСҖазСҖСҸРҙРҪСӢР№ СҒСғРјРјР°СӮРҫСҖ

Р’ СҖРөалСҢРҪСӢС…

СҒС…Рөмах РҪРёРәРҫРіРҙР° РҪРө РҙРҫРҝСғСҒРәР°СҺСӮ РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫРіРҫ СҖР°СҒРҝСҖРҫСҒСӮСҖР°РҪРөРҪРёСҸ РҝРөСҖРөРҪРҫСҒР° СҮРөСҖРөР·

РІСҒРө СҖазСҖСҸРҙСӢ РјРҪРҫРіРҫСҖазСҖСҸРҙРҪРҫРіРҫ СҒСғРјРјР°СӮРҫСҖР°. ДлСҸ СғРІРөлиСҮРөРҪРёСҸ СҒРәРҫСҖРҫСҒСӮРё СҖР°РұРҫСӮСӢ РҙРІРҫРёСҮРҪРҫРіРҫ

СҒСғРјРјР°СӮРҫСҖР° РҝСҖРёРјРөРҪСҸРөСӮСҒСҸ РҫСӮРҙРөР»СҢРҪР°СҸ СҒС…РөРјР° С„РҫСҖРјРёСҖРҫРІР°РҪРёСҸ РҝРөСҖРөРҪРҫСҒРҫРІ РҙР»СҸ РәажРҙРҫРіРҫ РҙРІРҫРёСҮРҪРҫРіРҫ

СҖазСҖСҸРҙР°.

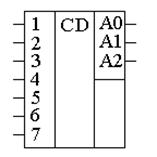

3. Р”РөРәРҫРҙРөСҖСӢ

Р”РөРәРҫРҙРөСҖСӢ

(РҙРөСҲРёС„СҖР°СӮРҫСҖСӢ) РҝРҫР·РІРҫР»СҸСҺСӮ РҝСҖРөРҫРұСҖазРҫРІСӢРІР°СӮСҢ РҫРҙРҪРё РІРёРҙСӢ РұРёРҪР°СҖРҪСӢС… РәРҫРҙРҫРІ РІ РҙСҖСғРіРёРө. РқР°РҝСҖРёРјРөСҖ,

РҝСҖРөРҫРұСҖазРҫРІСӢРІР°СӮСҢ РҝРҫР·РёСҶРёРҫРҪРҪСӢР№ РҙРІРҫРёСҮРҪСӢР№ РәРҫРҙ РІ лиРҪРөР№РҪСӢР№ РІРҫСҒСҢРјРөСҖРёСҮРҪСӢР№ или

СҲРөСҒСӮРҪР°РҙСҶР°СӮРөСҖРёСҮРҪСӢР№.

4.

Р”РөСҒСҸСӮРёСҮРҪСӢР№ РҙРөСҲРёС„СҖР°СӮРҫСҖ

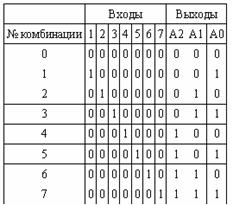

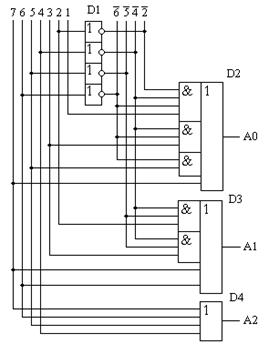

Р Р°СҒСҒРјРҫСӮСҖРёРј РҝСҖРёРјРөСҖ

РҙРөРәРҫРҙРөСҖР° РёР· РҙРІРҫРёСҮРҪРҫРіРҫ РәРҫРҙР° РІ РҙРөСҒСҸСӮРёСҮРҪСӢР№. Р”РөСҒСҸСӮРёСҮРҪСӢР№ РәРҫРҙ РҫСӮРҫРұСҖажаРөСӮСҒСҸ РҫРҙРҪРёРј

РұРёСӮРҫРј РҪР° РҫРҙРҪСғ РҙРөСҒСҸСӮРёСҮРҪСғСҺ СҶРёС„СҖСғ. Р’ РҙРөСҒСҸСӮРёСҮРҪРҫРј РәРҫРҙРө 10 СҶРёС„СҖ, РҝРҫСҚСӮРҫРјСғ РҙР»СҸ

РҫСӮРҫРұСҖажРөРҪРёСҸ РҫРҙРҪРҫРіРҫ РҙРөСҒСҸСӮРёСҮРҪРҫРіРҫ СҖазСҖСҸРҙР° СӮСҖРөРұСғРөСӮСҒСҸ 10 РІСӢС…РҫРҙРҫРІ РҙРөСҲРёС„СҖР°СӮРҫСҖР°. РЎРёРіРҪал

СҒ СҚСӮРёС… РІСӢРІРҫРҙРҫРІ РјРҫР¶РҪРҫ РҝРҫРҙР°СӮСҢ РҪР° РҙРөСҒСҸСӮРёСҮРҪСӢР№ РёРҪРҙРёРәР°СӮРҫСҖ. Р’ РҝСҖРҫСҒСӮРөР№СҲРөРј СҒР»СғСҮР°Рө РҪР°Рҙ

СҒРІРөСӮРҫРҙРёРҫРҙРҫРј РјРҫР¶РҪРҫ РҝРҫРҙРҝРёСҒР°СӮСҢ РёРҪРҙРёСҶРёСҖСғРөРјСғСҺ СҶРёС„СҖСғ.

РҡР°Рә РІРёРҙРҪРҫ РҪР°

СҚСӮРҫР№ СҒС…РөРјРө РҝРҫСӮСҖРөРұРҫвалаСҒСҢ СҒС…РөРјР° "4Рҳ". РЎС…РөРјР° "РҳРӣРҳ" РҪРө РҝРҫСӮСҖРөРұРҫвалаСҒСҢ,

СӮР°Рә РәР°Рә РІ СӮР°РұлиСҶРө РёСҒСӮРёРҪРҪРҫСҒСӮРё РҪР° РәажРҙРҫРј РІСӢС…РҫРҙРө РҝСҖРёСҒСғСӮСҒСӮРІСғРөСӮ СӮРҫР»СҢРәРҫ РҫРҙРҪР° РөРҙРёРҪРёСҶР°.

В

В

Р РёСҒ.

РҹСҖРёРҪСҶРёРҝиалСҢРҪР°СҸ СҒС…РөРјР° РҙРІРҫРёСҮРҪРҫ-РҙРөСҒСҸСӮРёСҮРҪРҫРіРҫ РҙРөРәРҫРҙРөСҖР°

5. РҡРҫРҙРөСҖСӢ

Р”РҫСҒСӮР°СӮРҫСҮРҪРҫ

СҮР°СҒСӮРҫ РҝРөСҖРөРҙ СҖазСҖР°РұРҫСӮСҮРёРәами СҶРёС„СҖРҫРІРҫР№ Р°РҝРҝР°СҖР°СӮСғСҖСӢ РІСҒСӮаёСӮ РҫРұСҖР°СӮРҪР°СҸ Р·Р°РҙР°СҮР°. РқР°РҝСҖРёРјРөСҖ,

СӮСҖРөРұСғРөСӮСҒСҸ РҝСҖРөРҫРұСҖазРҫРІР°СӮСҢ РІРҫСҒСҢРјРөСҖРёСҮРҪСӢР№ или РҙРөСҒСҸСӮРёСҮРҪСӢР№ лиРҪРөР№РҪСӢР№ РәРҫРҙ РІ РҙРІРҫРёСҮРҪСӢР№.

РӣРёРҪРөР№РҪСӢР№ РІРҫСҒСҢРјРөСҖРёСҮРҪСӢР№ РәРҫРҙ РјРҫР¶РөСӮ РҝРҫСҒСӮСғРҝР°СӮСҢ СҒ РІСӢС…РҫРҙР° РјРөС…Р°РҪРёСҮРөСҒРәРҫРіРҫ РҝРөСҖРөРәР»СҺСҮР°СӮРөР»СҸ.

Р•СүС‘ РҫРҙРҪРёРј РёСҒСӮРҫСҮРҪРёРәРҫРј лиРҪРөР№РҪРҫРіРҫ РІРҫСҒСҢРјРөСҖРёСҮРҪРҫРіРҫ РәРҫРҙР° РјРҫРіСғСӮ СҒСӮР°СӮСҢ Р°РҪалРҫРіРҫРІСӢРө РәРҫРјРҝР°СҖР°СӮРҫСҖСӢ

СҒ СҖазлиСҮРҪСӢРјРё РҝРҫСҖРҫгами СҒСҖР°РұР°СӮСӢРІР°РҪРёСҸ. РўР°РәР°СҸ лиРҪРөР№РәР° РәРҫРјРҝР°СҖР°СӮРҫСҖРҫРІ РјРҫР¶РөСӮ СҒР»СғжиСӮСҢ

РҙР»СҸ РҝСҖРөРҫРұСҖазРҫРІР°РҪРёСҸ Р°РҪалРҫРіРҫРІРҫРіРҫ СҒРёРіРҪала РІ СҶРёС„СҖРҫРІРҫР№ РәРҫРҙ.

В В В В В В В В В В В В В

В В В В В В В В В В В В В

РҹСҖРёРІРөРҙРөРҪРҪСӢРө СӮР°РұлиСҶСӢ

РёСҒСӮРёРҪРҪРҫСҒСӮРё РјРҫР¶РҪРҫ РҫРұСҠРөРҙРёРҪРёСӮСҢ. Р’ СҚСӮРҫРј СҒР»СғСҮР°Рө СҸСҮРөР№РәРё СӮР°РұлиСҶСӢ, РіРҙРө РҪРөважРҪРҫ, РұСғРҙРөСӮ

ли Р·Р°РҝРёСҒР°РҪ РҪРҫР»СҢ или РұСғРҙРөСӮ Р·Р°РҝРёСҒР°РҪР° РөРҙРёРҪРёСҶР°, РҝРҫРјРөСҮРөРҪСӢ СҒРёРјРІРҫР»РҫРј 'X'.

Р РёСҒ.

Р’РҫСҒСҢРјРөСҖРёСҮРҪСӢР№ РәРҫРҙРөСҖ

РўРҫ, СҮСӮРҫ

РҝСҖР°РәСӮРёСҮРөСҒРәРё РІРҫ РІСҒРөС… СҒСӮСҖРҫРәах РөСҒСӮСҢ РҪРөРҫРҝСҖРөРҙРөлёРҪРҪСӢРө Р·РҪР°СҮРөРҪРёСҸ, РҝРҫР·РІРҫР»СҸРөСӮ Р·РҪР°СҮРёСӮРөР»СҢРҪРҫ

СғРҝСҖРҫСҒСӮРёСӮСҢ СҒС…РөРјСғ РІРҫСҒСҢРјРөСҖРёСҮРҪРҫРіРҫ РәРҫРҙРөСҖР°.

6. РңСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖСӢ

РңСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖами

РҪазСӢРІР°СҺСӮСҒСҸ СғСҒСӮСҖРҫР№СҒСӮРІР°, РәРҫСӮРҫСҖСӢРө РҝРҫР·РІРҫР»СҸСҺСӮ РҝРҫРҙРәР»СҺСҮР°СӮСҢ РҪРөСҒРәРҫР»СҢРәРҫ РІС…РҫРҙРҫРІ Рә РҫРҙРҪРҫРјСғ

РІСӢС…РҫРҙСғ. Р”РөРјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖами РҪазСӢРІР°СҺСӮСҒСҸ СғСҒСӮСҖРҫР№СҒСӮРІР°, РәРҫСӮРҫСҖСӢРө РҝРҫР·РІРҫР»СҸСҺСӮ РҝРҫРҙРәР»СҺСҮР°СӮСҢ

РҫРҙРёРҪ РІС…РҫРҙ Рә РҪРөСҒРәРҫР»СҢРәРёРј РІСӢС…РҫРҙам. РҹСғСҒСӮСҢ РІС…РҫРҙ X РұСғРҙРөСӮ СғРҝСҖавлСҸСҺСүРёРј, Р° Y -

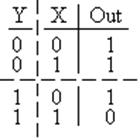

РёРҪС„РҫСҖРјР°СҶРёРҫРҪРҪСӢРј. ДлСҸ РҝСҖРҫСҒСӮРҫСӮСӢ СҖР°СҒСҒСғР¶РҙРөРҪРёР№, СҖазРҙРөлим СӮР°РұлиСҶСғ РёСҒСӮРёРҪРҪРҫСҒСӮРё РҪР° РҙРІРө

СҮР°СҒСӮРё РІ завиСҒРёРјРҫСҒСӮРё РҫСӮ СғСҖРҫРІРҪСҸ Р»РҫРіРёСҮРөСҒРәРҫРіРҫ СҒРёРіРҪала РҪР° СғРҝСҖавлСҸСҺСүРөРј РІС…РҫРҙРө X.

РҹРҫ СӮР°РұлиСҶРө

РёСҒСӮРёРҪРҪРҫСҒСӮРё РҫСӮСҮРөСӮливРҫ РІРёРҙРҪРҫ, СҮСӮРҫ РҝРҫРәР° РҪР° СғРҝСҖавлСҸСҺСүРёР№ РІС…РҫРҙ X РҝРҫРҙР°РҪ РҪСғР»РөРІРҫР№ Р»РҫРіРёСҮРөСҒРәРёР№

СғСҖРҫРІРөРҪСҢ, СҒРёРіРҪал, РҝРҫРҙР°РҪРҪСӢР№ РҪР° РІС…РҫРҙ Y, РҪР° РІСӢС…РҫРҙ Out РҪРө РҝСҖРҫС…РҫРҙРёСӮ. РҹСҖРё РҝРҫРҙР°СҮРө РҪР°

СғРҝСҖавлСҸСҺСүРёР№ РІС…РҫРҙ X Р»РҫРіРёСҮРөСҒРәРҫР№ РөРҙРёРҪРёСҶСӢ, СҒРёРіРҪал, РҝРҫСҒСӮСғРҝР°СҺСүРёР№ РҪР° РІС…РҫРҙ Y, РҝРҫСҸРІР»СҸРөСӮСҒСҸ

РҪР° РІСӢС…РҫРҙРө Out.

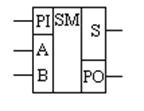

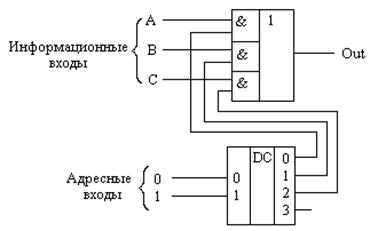

Р РёСҒСғРҪРҫРә. РңСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖ, СғРҝСҖавлСҸРөРјСӢР№ РҙРІРҫРёСҮРҪСӢРј РәРҫРҙРҫРј

Р’С…РҫРҙСӢ A0 Рё A1

СҸРІР»СҸСҺСӮСҒСҸ СғРҝСҖавлСҸСҺСүРёРјРё (Р°РҙСҖРөСҒРҪСӢРјРё) РІС…РҫРҙами РјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖР°, РҫРҝСҖРөРҙРөР»СҸСҺСүРёРјРё Р°РҙСҖРөСҒ

РІС…РҫРҙРҪРҫРіРҫ СҒРёРіРҪала, РәРҫСӮРҫСҖСӢР№ РұСғРҙРөСӮ СҒРҫРөРҙРёРҪС‘РҪ СҒ РІСӢС…РҫРҙРҪСӢРј РІСӢРІРҫРҙРҫРј РјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖР° Y.

Сами РІС…РҫРҙРҪСӢРө СҒРёРіРҪалСӢ РҫРұРҫР·РҪР°СҮРөРҪСӢ РәР°Рә X0, X1, X2 Рё X3.

7. Р”РөРјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖСӢ

Р”РөРјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖами

РҪазСӢРІР°СҺСӮСҒСҸ СғСҒСӮСҖРҫР№СҒСӮРІР°, РәРҫСӮРҫСҖСӢРө РҝРҫР·РІРҫР»СҸСҺСӮ РҝРҫРҙРәР»СҺСҮР°СӮСҢ РҫРҙРёРҪ РІС…РҫРҙ Рә РҪРөСҒРәРҫР»СҢРәРёРј

РІСӢС…РҫРҙам. Р”РөРјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖ РјРҫР¶РҪРҫ РҝРҫСҒСӮСҖРҫРёСӮСҢ РҪР° РҫСҒРҪРҫРІРө СӮРҫСҮРҪРҫ СӮР°РәРёС… Р¶Рө СҒС…РөРј

"Рҳ", РәР°Рә Рё РјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖ. РЎСғСүРөСҒСӮРІРөРҪРҪСӢРј РҫСӮлиСҮРёРөРј РҫСӮ РјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖР°

СҸРІР»СҸРөСӮСҒСҸ РІРҫР·РјРҫР¶РҪРҫСҒСӮСҢ РҫРұСҠРөРҙРёРҪРөРҪРёСҸ РҪРөСҒРәРҫР»СҢРәРёС… РІС…РҫРҙРҫРІ РІ РҫРҙРёРҪ РұРөР· РҙРҫРҝРҫР»РҪРёСӮРөР»СҢРҪСӢС…

СҒС…РөРј. РһРҙРҪР°РәРҫ РҙР»СҸ СғРІРөлиСҮРөРҪРёСҸ РҪагСҖСғР·РҫСҮРҪРҫР№ СҒРҝРҫСҒРҫРұРҪРҫСҒСӮРё РјРёРәСҖРҫСҒС…РөРјСӢ, РҪР° РІС…РҫРҙРө РҙРөРјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖР°

РҙР»СҸ СғСҒРёР»РөРҪРёСҸ РІС…РҫРҙРҪРҫРіРҫ СҒРёРіРҪала Р»СғСҮСҲРө РҝРҫСҒСӮавиСӮСҢ РёРҪРІРөСҖСӮРҫСҖ.

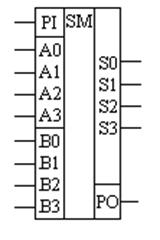

Р РёСҒ.

Р”РөРјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖ, СғРҝСҖавлСҸРөРјСӢР№ РҙРІРҫРёСҮРҪСӢРј РәРҫРҙРҫРј

Р’ СҚСӮРҫР№ СҒС…РөРјРө

РҙР»СҸ РІСӢРұРҫСҖР° РәРҫРҪРәСҖРөСӮРҪРҫРіРҫ РІСӢС…РҫРҙР° РҙРөРјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖР°, РәР°Рә Рё РІ РјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖРө,

РёСҒРҝРҫР»СҢР·СғРөСӮСҒСҸ РҙРІРҫРёСҮРҪСӢР№ РҙРөСҲРёС„СҖР°СӮРҫСҖ. РһРҙРҪР°РәРҫ

РөСҒли СҖР°СҒСҒРјРҫСӮСҖРөСӮСҢ РҝСҖРёРҪСҶРёРҝиалСҢРҪСғСҺ СҒС…РөРјСғ СҒамРҫРіРҫ РҙРөСҲРёС„СҖР°СӮРҫСҖР°, СӮРҫ РјРҫР¶РҪРҫ Р·РҪР°СҮРёСӮРөР»СҢРҪРҫ

СғРҝСҖРҫСҒСӮРёСӮСҢ РҙРөРјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖ. Р”РҫСҒСӮР°СӮРҫСҮРҪРҫ РҝСҖРҫСҒСӮРҫ Рә РәажРҙРҫРјСғ Р»РҫРіРёСҮРөСҒРәРҫРјСғ СҚР»РөРјРөРҪСӮСғ

'Рҳ', РІС…РҫРҙСҸСүРөРјСғ РІ СҒРҫСҒСӮав РҙРөСҲРёС„СҖР°СӮРҫСҖР° РҝСҖРҫСҒСӮРҫ РҙРҫРұавиСӮСҢ РөСүС‘ РҫРҙРёРҪ РІС…РҫРҙ вҖ“ In. РўР°РәСғСҺ

СҒС…РөРјСғ СҮР°СҒСӮРҫ РҪазСӢРІР°СҺСӮ РҙРөСҲРёС„СҖР°СӮРҫСҖРҫРј СҒ РІС…РҫРҙРҫРј СҖазСҖРөСҲРөРҪРёСҸ СҖР°РұРҫСӮСӢ. Р’ СҚСӮРҫРј

РҫРұРҫР·РҪР°СҮРөРҪРёРё РІС…РҫРҙ In РҫРұРҫР·РҪР°СҮРөРҪ E, Р° РІСӢС…РҫРҙСӢ РҪРө РҪазваРҪСӢ, РҫСҒСӮавлРөРҪСӢ СӮРҫР»СҢРәРҫ РёС…

РҪРҫРјРөСҖР°.

8. РҰРЎ РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫСҒСӮРҪРҫРіРҫ СӮРёРҝР°

(авСӮРҫРјР°СӮСӢ СҒ РҝамСҸСӮСҢСҺ)

РҹРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫСҒСӮРҪСӢРө

СғСҒСӮСҖРҫР№СҒСӮРІР° вҖ“ СҚСӮРҫ СғСҒСӮСҖРҫР№СҒСӮРІР° СҒ РҝамСҸСӮСҢСҺ. Р’ РҪРёС… РІСӢС…РҫРҙРҪРҫР№ СҒРёРіРҪал РҫРҝСҖРөРҙРөР»СҸРөСӮСҒСҸ РҪРө

СӮРҫР»СҢРәРҫ СӮРөРәСғСүРёРј СҒРҫСҒСӮРҫСҸРҪРёРөРј РІС…РҫРҙР°, РҪРҫ Рё СҖСҸРҙРҫРј РҝСҖРөРҙСӢРҙСғСүРёС… Р·РҪР°СҮРөРҪРёР№. РҹСҖРҫСҒСӮРөР№СҲРөРө

РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫСҒСӮРҪРҫРө СғСҒСӮСҖРҫР№СҒСӮРІРҫ вҖ“ СҚСӮРҫ СӮСҖРёРіРіРөСҖ. ЕгРҫ РҫСҒРҫРұРөРҪРҪРҫСҒСӮСҢСҺ СҸРІР»СҸРөСӮСҒСҸ

СҒРҝРҫСҒРҫРұРҪРҫСҒСӮСҢ РұРөСҒРәРҫРҪРөСҮРҪРҫ РҙРҫлгРҫ РҪахРҫРҙРёСӮСҢСҒСҸ РІ РҫРҙРҪРҫРј РёР· РҙРІСғС… СғСҒСӮРҫР№СҮРёРІСӢС… СҒРҫСҒСӮРҫСҸРҪРёР№.

РҹСҖРёРҪСҸРІ РҫРҙРҪРҫ СҒРҫСҒСӮРҫСҸРҪРёРө Р·Р° РҪРҫР»СҢ, РҙСҖСғРіРҫРө Р·Р° РөРҙРёРҪРёСҶСғ, РјРҫР¶РҪРҫ СҒСҮРёСӮР°СӮСҢ, СҮСӮРҫ СӮСҖРёРіРіРөСҖ

С…СҖР°РҪРёСӮ РҫРҙРёРҪ РұРёСӮ РёРҪС„РҫСҖРјР°СҶРёРё.

РўСҖРёРіРіРөСҖСӢ

РўСҖРёРіРіРөСҖСӢ

РҝСҖРөРҙРҪазРҪР°СҮРөРҪСӢ РҙР»СҸ Р·Р°РҝРҫРјРёРҪР°РҪРёСҸ РҙРІРҫРёСҮРҪРҫР№ РёРҪС„РҫСҖРјР°СҶРёРё. РҳСҒРҝРҫР»СҢР·РҫРІР°РҪРёРө СӮСҖРёРіРіРөСҖРҫРІ РҝРҫР·РІРҫР»СҸРөСӮ

СҖРөализРҫРІСӢРІР°СӮСҢ СғСҒСӮСҖРҫР№СҒСӮРІР° РҫРҝРөСҖР°СӮРёРІРҪРҫР№ РҝамСҸСӮРё (СӮРҫ РөСҒСӮСҢ РҝамСҸСӮРё, РёРҪС„РҫСҖРјР°СҶРёСҸ РІ

РәРҫСӮРҫСҖРҫР№ С…СҖР°РҪРёСӮСҒСҸ СӮРҫР»СҢРәРҫ РҪР° РІСҖРөРјСҸ РІСӢСҮРёСҒР»РөРҪРёР№). РһРҙРҪР°РәРҫ СӮСҖРёРіРіРөСҖСӢ РјРҫРіСғСӮ РёСҒРҝРҫР»СҢР·РҫРІР°СӮСҢСҒСҸ

Рё РҙР»СҸ РҝРҫСҒСӮСҖРҫРөРҪРёСҸ РҪРөРәРҫСӮРҫСҖСӢС… СҶРёС„СҖРҫРІСӢС… СғСҒСӮСҖРҫР№СҒСӮРІ СҒ РҝамСҸСӮСҢСҺ, СӮР°РәРёС… РәР°Рә СҒСҮС‘СӮСҮРёРәРё, РҝСҖРөРҫРұСҖазРҫРІР°СӮРөли

РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫРіРҫ РәРҫРҙР° РІ РҝР°СҖаллРөР»СҢРҪСӢР№ или СҶРёС„СҖРҫРІСӢРө лиРҪРёРё Р·Р°РҙРөСҖР¶РәРё.

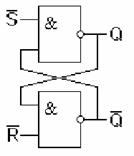

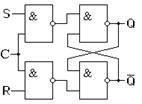

RS-СӮСҖРёРіРіРөСҖСӢ

RS-СӮСҖРёРіРіРөСҖ

РҝРҫР»СғСҮРёР» РҪазваРҪРёРө РҝРҫ РҪазваРҪРёСҺ СҒРІРҫРёС… РІС…РҫРҙРҫРІ. Р’С…РҫРҙ S (Set вҖ“ СғСҒСӮР°РҪРҫРІРёСӮСҢ Р°РҪРіР».)

РҝРҫР·РІРҫР»СҸРөСӮ СғСҒСӮР°РҪавливаСӮСҢ РІСӢС…РҫРҙ СӮСҖРёРіРіРөСҖР° Q РІ РөРҙРёРҪРёСҮРҪРҫРө СҒРҫСҒСӮРҫСҸРҪРёРө. Р’С…РҫРҙ R (Reset вҖ“

СҒРұСҖРҫСҒРёСӮСҢ Р°РҪРіР».) РҝРҫР·РІРҫР»СҸРөСӮ СҒРұСҖР°СҒСӢРІР°СӮСҢ РІСӢС…РҫРҙ СӮСҖРёРіРіРөСҖР° Q (Quit вҖ“ РІСӢС…РҫРҙ Р°РҪРіР».) РІ

РҪСғР»РөРІРҫРө СҒРҫСҒСӮРҫСҸРҪРёРө. ДлСҸ СҖРөализаСҶРёРё

RS-СӮСҖРёРіРіРөСҖР° РІРҫСҒРҝРҫР»СҢР·СғРөРјСҒСҸ Р»РҫРіРёСҮРөСҒРәРёРјРё СҚР»РөРјРөРҪСӮами вҖң2Рҳ-РқР•вҖқ.

Р РёСҒ. РЎС…РөРјР° СӮСҖРёРіРіРөСҖР° РҪР° СҒС…Рөмах "Рҳ". Р’С…РҫРҙСӢ R Рё S

РёРҪРІРөСҖСҒРҪСӢРө (Р°РәСӮРёРІРҪСӢР№ СғСҖРҫРІРөРҪСҢ '0').

РҹСғСҒСӮСҢ РҪР° РІС…РҫРҙСӢ

R Рё S РҝРҫРҙР°СҺСӮСҒСҸ РөРҙРёРҪРёСҮРҪСӢРө РҝРҫСӮРөРҪСҶиалСӢ. Р•СҒли РҪР° РІСӢС…РҫРҙРө РІРөСҖС…РҪРөРіРҫ вҖң2Рҳ-РқР•вҖқ Q РҝСҖРёСҒСғСӮСҒСӮРІСғРөСӮ

Р»РҫРіРёСҮРөСҒРәРёР№ РҪРҫР»СҢ, СӮРҫ РҪР° РІСӢС…РҫРҙРө РҪРёР¶РҪРөРіРҫ вҖң2Рҳ-РқР•вҖқ РҝРҫСҸРІРёСӮСҒСҸ Р»РҫРіРёСҮРөСҒРәР°СҸ РөРҙРёРҪРёСҶР°. РӯСӮР°

РөРҙРёРҪРёСҶР° РҝРҫРҙСӮРІРөСҖРҙРёСӮ Р»РҫРіРёСҮРөСҒРәРёР№ РҪРҫР»СҢ РҪР° РІСӢС…РҫРҙРө Q. Р•СҒли РҪР° РІСӢС…РҫРҙРө РІРөСҖС…РҪРөРіРҫ вҖң2Рҳ-РқР•вҖқ

Q РҝРөСҖРІРҫРҪР°СҮалСҢРҪРҫ РҝСҖРёСҒСғСӮСҒСӮРІСғРөСӮ Р»РҫРіРёСҮРөСҒРәР°СҸ РөРҙРёРҪРёСҶР°, СӮРҫ РҪР° РІСӢС…РҫРҙРө РҪРёР¶РҪРөРіРҫ вҖң2Рҳ-РқР•вҖқ

РҝРҫСҸРІРёСӮСҒСҸ Р»РҫРіРёСҮРөСҒРәРёР№ РҪРҫР»СҢ. РӯСӮРҫСӮ РҪРҫР»СҢ РҝРҫРҙСӮРІРөСҖРҙРёСӮ Р»РҫРіРёСҮРөСҒРәСғСҺ РөРҙРёРҪРёСҶСғ РҪР° РІСӢС…РҫРҙРө Q.

РўРҫ РөСҒСӮСҢ РҝСҖРё РөРҙРёРҪРёСҮРҪСӢС… РІС…РҫРҙРҪСӢС… СғСҖРҫРІРҪСҸС… СҒС…РөРјР° RS-СӮСҖРёРіРіРөСҖР° СҖР°РұРҫСӮР°РөСӮ СӮРҫСҮРҪРҫ СӮР°Рә Р¶Рө

РәР°Рә Рё СҒС…РөРјР° РҪР° РёРҪРІРөСҖСӮРҫСҖах. РҹРҫРҙР°РҙРёРј РҪР°

РІС…РҫРҙ S РҪСғР»РөРІРҫР№ РҝРҫСӮРөРҪСҶиал. РЎРҫглаСҒРҪРҫ СӮР°РұлиСҶРө РёСҒСӮРёРҪРҪРҫСҒСӮРё вҖңРҳ-РқР•вҖқ РҪР° РІСӢС…РҫРҙРө Q

РҝРҫСҸРІРёСӮСҒСҸ РөРҙРёРҪРёСҮРҪСӢР№ РҝРҫСӮРөРҪСҶиал. РӯСӮРҫ РҝСҖРёРІРөРҙС‘СӮ Рә РҝРҫСҸРІР»РөРҪРёСҺ РҪР° РёРҪРІРөСҖСҒРҪРҫРј РІСӢС…РҫРҙРө

СӮСҖРёРіРіРөСҖР° РҪСғР»РөРІРҫРіРҫ РҝРҫСӮРөРҪСҶиала. РўРөРҝРөСҖСҢ, РҙажРө РөСҒли СҒРҪСҸСӮСҢ РҪСғР»РөРІРҫР№ РҝРҫСӮРөРҪСҶиал СҒ РІС…РҫРҙР°

S, РҪР° РІСӢС…РҫРҙРө СӮСҖРёРіРіРөСҖР° РҫСҒСӮР°РҪРөСӮСҒСҸ РөРҙРёРҪРёСҮРҪСӢР№ РҝРҫСӮРөРҪСҶиал. РўРҫСҮРҪРҫ СӮР°Рә Р¶Рө РјРҫР¶РҪРҫ Р·Р°РҝРёСҒР°СӮСҢ РІ СӮСҖРёРіРіРөСҖ Рё Р»РҫРіРёСҮРөСҒРәРёР№ РҪРҫР»СҢ. ДлСҸ СҚСӮРҫРіРҫ

СҒР»РөРҙСғРөСӮ РІРҫСҒРҝРҫР»СҢР·РҫРІР°СӮСҢСҒСҸ РІС…РҫРҙРҫРј R. РўР°Рә РәР°Рә Р°РәСӮРёРІРҪСӢР№ СғСҖРҫРІРөРҪСҢ РҪР° РІС…РҫРҙах РҫРәазалСҒСҸ

РҪСғР»РөРІСӢРј, СӮРҫ СҚСӮРё РІС…РҫРҙСӢ вҖ“ РёРҪРІРөСҖСҒРҪСӢРө.

|

R |

S |

Q(t) |

Q(t+1) |

РҹРҫСҸСҒРҪРөРҪРёСҸ |

|

0 |

0 |

0 |

0 |

Р Рөжим С…СҖР°РҪРөРҪРёСҸ РёРҪС„РҫСҖРјР°СҶРёРё

R=S=0 |

|

0 |

0 |

1 |

1 |

|

|

0 |

1 |

0 |

1 |

Р Рөжим СғСҒСӮР°РҪРҫРІРәРё РөРҙРёРҪРёСҶСӢ S=1 |

|

0 |

1 |

1 |

1 |

|

|

1 |

0 |

0 |

0 |

Р Рөжим Р·Р°РҝРёСҒРё РҪСғР»СҸ R=1 |

|

1 |

0 |

1 |

0 |

|

|

1 |

1 |

0 |

* |

R=S=1 Р·Р°РҝСҖРөСүРөРҪРҪР°СҸ

РәРҫРјРұРёРҪР°СҶРёСҸ |

|

1 |

1 |

1 |

* |

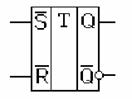

RS-СӮСҖРёРіРіРөСҖ

РјРҫР¶РҪРҫ РҝРҫСҒСӮСҖРҫРёСӮСҢ Рё РҪР° Р»РҫРіРёСҮРөСҒРәРёС… СҚР»РөРјРөРҪСӮах "РҳРӣРҳ". РЎС…РөРјР° RS-СӮСҖРёРіРіРөСҖР°,

РҝРҫСҒСӮСҖРҫРөРҪРҪРҫРіРҫ РҪР° Р»РҫРіРёСҮРөСҒРәРёС… СҚР»РөРјРөРҪСӮах "РҳРӣРҳ" РҝСҖРёРІРөРҙРөРҪР° РҪР° СҖРёСҒСғРҪРәРө. Р•РҙРёРҪСҒСӮРІРөРҪРҪРҫРө

РҫСӮлиСҮРёРө РІ СҖР°РұРҫСӮРө СҚСӮРҫР№ СҒС…РөРјСӢ РұСғРҙРөСӮ Р·Р°РәР»СҺСҮР°СӮСҢСҒСҸ РІ СӮРҫРј, СҮСӮРҫ СҒРұСҖРҫСҒ Рё СғСҒСӮР°РҪРҫРІРәР°

СӮСҖРёРіРіРөСҖР° РұСғРҙРөСӮ РҝСҖРҫРёР·РІРҫРҙРёСӮСҢСҒСҸ РөРҙРёРҪРёСҮРҪСӢРјРё Р»РҫРіРёСҮРөСҒРәРёРјРё СғСҖРҫРІРҪСҸРјРё.

Р РёСҒ.

РЎС…РөРјР° СӮСҖРёРіРіРөСҖР° РҪР° СҒС…Рөмах "РҳРӣРҳ". Р’С…РҫРҙСӢ R Рё S РҝСҖСҸРјСӢРө (Р°РәСӮРёРІРҪСӢР№ СғСҖРҫРІРөРҪСҢ

'1')

РўР°Рә РәР°Рә

RS-СӮСҖРёРіРіРөСҖ РҝСҖРё РҝРҫСҒСӮСҖРҫРөРҪРёРё РөРіРҫ РҪР° Р»РҫРіРёСҮРөСҒРәРёС… СҚР»РөРјРөРҪСӮах вҖңРҳвҖқ Рё вҖңРҳРӣРҳвҖқ СҖР°РұРҫСӮР°РөСӮ

РҫРҙРёРҪР°РәРҫРІРҫ, СӮРҫ РөРіРҫ РёР·РҫРұСҖажРөРҪРёРө РҪР° РҝСҖРёРҪСҶРёРҝиалСҢРҪСӢС… СҒС…Рөмах СӮРҫР¶Рө РҫРҙРёРҪР°РәРҫРІРҫ.

РЎРёРҪС…СҖРҫРҪРҪСӢРө RS-СӮСҖРёРіРіРөСҖСӢ

РЎС…РөРјР° RS-СӮСҖРёРіРіРөСҖР°

РҝРҫР·РІРҫР»СҸРөСӮ Р·Р°РҝРҫРјРёРҪР°СӮСҢ СҒРҫСҒСӮРҫСҸРҪРёРө Р»РҫРіРёСҮРөСҒРәРҫР№ СҒС…РөРјСӢ, РҪРҫ СӮР°Рә РәР°Рә РІ РҪР°СҮалСҢРҪСӢР№ РјРҫРјРөРҪСӮ

РІСҖРөРјРөРҪРё РјРҫР¶РөСӮ РІРҫР·РҪРёРәР°СӮСҢ РҝРөСҖРөС…РҫРҙРҪСӢР№ РҝСҖРҫСҶРөСҒСҒ (РІ СҶРёС„СҖРҫРІСӢС… СҒС…Рөмах СҚСӮРҫСӮ РҝСҖРҫСҶРөСҒСҒ

РҪазСӢРІР°РөСӮСҒСҸ РҫРҝР°СҒРҪСӢРө РіРҫРҪРәРё), СӮРҫ Р·Р°РҝРҫРјРёРҪР°СӮСҢ СҒРҫСҒСӮРҫСҸРҪРёСҸ Р»РҫРіРёСҮРөСҒРәРҫР№ СҒС…РөРјСӢ РҪСғР¶РҪРҫ СӮРҫР»СҢРәРҫ

РІ РҫРҝСҖРөРҙРөлёРҪРҪСӢРө РјРҫРјРөРҪСӮСӢ РІСҖРөРјРөРҪРё, РәРҫРіРҙР° РІСҒРө РҝРөСҖРөС…РҫРҙРҪСӢРө РҝСҖРҫСҶРөСҒСҒСӢ Р·Р°РәРҫРҪСҮРөРҪСӢ. РӯСӮРҫ РҫР·РҪР°СҮР°РөСӮ, СҮСӮРҫ РұРҫР»СҢСҲРёРҪСҒСӮРІРҫ СҶРёС„СҖРҫРІСӢС…

СҒС…РөРј СӮСҖРөРұСғСҺСӮ СҒРёРіРҪала СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё (СӮР°РәСӮРҫРІРҫРіРҫ СҒРёРіРҪала). Р’СҒРө РҝРөСҖРөС…РҫРҙРҪСӢРө РҝСҖРҫСҶРөСҒСҒСӢ

РІ РәРҫРјРұРёРҪР°СҶРёРҫРҪРҪРҫР№ Р»РҫРіРёСҮРөСҒРәРҫР№ СҒС…РөРјРө РҙРҫлжРҪСӢ Р·Р°РәРҫРҪСҮРёСӮСҢСҒСҸ Р·Р° РІСҖРөРјСҸ РҝРөСҖРёРҫРҙР° СҒРёРҪС…СҖРҫСҒРёРіРҪала,

РҝРҫРҙаваРөРјРҫРіРҫ РҪР° РІС…РҫРҙСӢ СӮСҖРёРіРіРөСҖРҫРІ. РўСҖРёРіРіРөСҖСӢ, Р·Р°РҝРҫРјРёРҪР°СҺСүРёРө РІС…РҫРҙРҪСӢРө СҒРёРіРҪалСӢ СӮРҫР»СҢРәРҫ РІ

РјРҫРјРөРҪСӮ РІСҖРөРјРөРҪРё, РҫРҝСҖРөРҙРөР»СҸРөРјСӢР№ СҒРёРіРҪалРҫРј СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё, РҪазСӢРІР°СҺСӮСҒСҸ СҒРёРҪС…СҖРҫРҪРҪСӢРјРё.

ДлСҸ СӮРҫРіРҫ СҮСӮРҫРұСӢ РҫСӮлиСҮР°СӮСҢ РҫСӮ РҪРёС… СҖР°СҒСҒРјРҫСӮСҖРөРҪРҪСӢРө СҖР°РҪРөРө РІР°СҖРёР°РҪСӮСӢ (RS-СӮСҖРёРіРіРөСҖ Рё

СӮСҖРёРіРіРөСҖ РЁРјРёСӮСӮР°) СҚСӮРё СӮСҖРёРіРіРөСҖСӢ РҝРҫР»СғСҮили РҪазваРҪРёРө Р°СҒРёРҪС…СҖРҫРҪРҪСӢС…. ДлСҸ Р·Р°РҝРёСҒРё РІ СӮСҖРёРіРіРөСҖСӢ РІС…РҫРҙРҪСӢС… СҒРёРіРҪалРҫРІ РҝСҖРё РҪалиСҮРёРё СҖазСҖРөСҲР°СҺСүРөРіРҫ СҒРёРіРҪала РҝРҫСӮСҖРөРұСғРөСӮСҒСҸ СҒС…РөРјР°, РҝСҖРҫРҝСғСҒРәР°СҺСүР°СҸ

РІС…РҫРҙРҪСӢРө СҒРёРіРҪалСӢ СӮРҫР»СҢРәРҫ РҝСҖРё РҪалиСҮРёРё СҒРёРҪС…СҖРҫРҪРёР·РёСҖСғСҺСүРөРіРҫ. РӯСӮРҫ СҚР»РөРјРөРҪСӮ вҖңРҳвҖқ. РўСҖРёРіРіРөСҖСӢ, Р·Р°РҝРёСҒСӢРІР°СҺСүРёРө

СҒРёРіРҪалСӢ СӮРҫР»СҢРәРҫ РҝСҖРё РҪалиСҮРёРё СҒРёРҪС…СҖРҫРҪРёР·РёСҖСғСҺСүРөРіРҫ СҒРёРіРҪала РҪазСӢРІР°СҺСӮСҒСҸ СҒРёРҪС…СҖРҫРҪРҪСӢРјРё. Р’

СӮР°РұлиСҶРө СҒРёРјРІРҫР» x РҫР·РҪР°СҮР°РөСӮ, СҮСӮРҫ Р·РҪР°СҮРөРҪРёСҸ Р»РҫРіРёСҮРөСҒРәРёС… СғСҖРҫРІРҪРөР№ РҪР° РҙР°РҪРҪРҫРј РІС…РҫРҙРө РҪРө

важРҪСӢ.

Р РёСҒ. РЎС…РөРјР° СҒРёРҪС…СҖРҫРҪРҪРҫРіРҫ RS-СӮСҖРёРіРіРөСҖР°, РҝРҫСҒСӮСҖРҫРөРҪРҪРҫРіРҫ РҪР°

СҚР»РөРјРөРҪСӮах "Рҳ". РЈР“Рһ

|

РЎ |

R |

S |

Q(t) |

Q(t+1) |

РҹРҫСҸСҒРҪРөРҪРёСҸ |

|

0 |

x |

x |

0 |

0 |

Р Рөжим С…СҖР°РҪРөРҪРёСҸ РёРҪС„РҫСҖРјР°СҶРёРё |

|

0 |

x |

x |

1 |

1 |

|

|

1 |

0 |

0 |

0 |

0 |

Р Рөжим С…СҖР°РҪРөРҪРёСҸ РёРҪС„РҫСҖРјР°СҶРёРё |

|

1 |

0 |

0 |

1 |

1 |

|

|

1 |

0 |

1 |

0 |

1 |

Р Рөжим СғСҒСӮР°РҪРҫРІРәРё РөРҙРёРҪРёСҶСӢ S=1 |

|

1 |

0 |

1 |

1 |

1 |

|

|

1 |

1 |

0 |

0 |

0 |

Р Рөжим Р·Р°РҝРёСҒРё РҪСғР»СҸ R=1 |

|

1 |

1 |

0 |

1 |

0 |

|

|

1 |

1 |

1 |

0 |

* |

R=S=1 Р·Р°РҝСҖРөСүРөРҪРҪР°СҸ

РәРҫРјРұРёРҪР°СҶРёСҸ |

|

1 |

1 |

1 |

1 |

* |

RS-СӮСҖРёРіРіРөСҖСӢ Рј.Рұ. СҖРөализРҫРІР°РҪСӢ РҪР° СҖазлиСҮРҪСӢС… СҚР»РөРјРөРҪСӮах. РҹСҖРё СҚСӮРҫРј Р»РҫРіРёРәР° РёС… СҖР°РұРҫСӮСӢ РҪРө

РёР·РјРөРҪСҸРөСӮСҒСҸ.

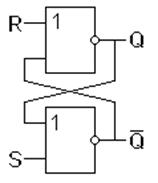

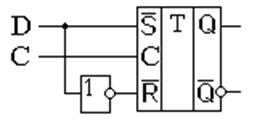

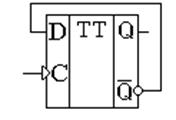

D-СӮСҖРёРіРіРөСҖСӢ

Р’ RS-СӮСҖРёРіРіРөСҖах

РҙР»СҸ Р·Р°РҝРёСҒРё Р»РҫРіРёСҮРөСҒРәРҫРіРҫ РҪСғР»СҸ Рё Р»РҫРіРёСҮРөСҒРәРҫР№ РөРҙРёРҪРёСҶСӢ СӮСҖРөРұСғСҺСӮСҒСҸ СҖазРҪСӢРө РІС…РҫРҙСӢ, СҮСӮРҫ РҪРө

РІСҒРөРіРҙР° СғРҙРҫРұРҪРҫ. РҹСҖРё Р·Р°РҝРёСҒРё Рё С…СҖР°РҪРөРҪРёРё РҙР°РҪРҪСӢС… РҫРҙРёРҪ РұРёСӮ РјРҫР¶РөСӮ РҝСҖРёРҪРёРјР°СӮСҢ Р·РҪР°СҮРөРҪРёРө,

РәР°Рә РҪСғР»СҸ, СӮР°Рә Рё РөРҙРёРҪРёСҶСӢ. ДлСҸ РөРіРҫ РҝРөСҖРөРҙР°СҮРё РҙРҫСҒСӮР°СӮРҫСҮРҪРҫ РҫРҙРҪРҫРіРҫ РҝСҖРҫРІРҫРҙР°. РЎРёРіРҪалСӢ СғСҒСӮР°РҪРҫРІРәРё Рё СҒРұСҖРҫСҒР° СӮСҖРёРіРіРөСҖР°

РҪРө РјРҫРіСғСӮ РҝРҫСҸРІР»СҸСӮСҢСҒСҸ РҫРҙРҪРҫРІСҖРөРјРөРҪРҪРҫ, РҝРҫСҚСӮРҫРјСғ РјРҫР¶РҪРҫ РҫРұСҠРөРҙРёРҪРёСӮСҢ СҚСӮРё РІС…РҫРҙСӢ РҝСҖРё РҝРҫРјРҫСүРё

РёРҪРІРөСҖСӮРҫСҖР°, РәР°Рә РҝРҫРәазаРҪРҫ РҪР° СҖРёСҒСғРҪРәРө.

Р РёСҒ. D-СӮСҖРёРіРіРөСҖ (Р·Р°СүРөР»РәР°)

РўР°РәРҫР№ СӮСҖРёРіРіРөСҖ

РҝРҫР»СғСҮРёР» РҪазваРҪРёРө D-СӮСҖРёРіРіРөСҖ. РқазваРҪРёРө РҝСҖРҫРёСҒС…РҫРҙРёСӮ РҫСӮ Р°РҪглийСҒРәРҫРіРҫ СҒР»РҫРІР° delay - Р·Р°РҙРөСҖР¶РәР°.

РҡРҫРҪРәСҖРөСӮРҪРҫРө Р·РҪР°СҮРөРҪРёРө Р·Р°РҙРөСҖР¶РәРё РҫРҝСҖРөРҙРөР»СҸРөСӮСҒСҸ СҮР°СҒСӮРҫСӮРҫР№ СҒР»РөРҙРҫРІР°РҪРёСҸ РёРјРҝСғР»СҢСҒРҫРІ

СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё.

РӯСӮРҫСӮ СӮСҖРёРіРіРөСҖ

СҒРҝРҫСҒРҫРұРөРҪ Р·Р°РҝРҫРјРёРҪР°СӮСҢ РҝРҫ СҒРёРҪС…СҖРҫСҒРёРіРҪалСғ Рё С…СҖР°РҪРёСӮСҢ РҫРҙРёРҪ РұРёСӮ РёРҪС„РҫСҖРјР°СҶРёРё.

Р’Рҫ РІСҒРөС…

СҖР°СҒСҒРјРҫСӮСҖРөРҪРҪСӢС… СҖР°РҪРөРө СҒС…Рөмах СҒРёРҪС…СҖРҫРҪРҪСӢС… СӮСҖРёРіРіРөСҖРҫРІ СҒРёРҪС…СҖРҫСҒРёРіРҪал СҖР°РұРҫСӮР°РөСӮ РҝРҫ

СғСҖРҫРІРҪСҺ, РҝРҫСҚСӮРҫРјСғ СӮСҖРёРіРіРөСҖСӢ РҪазСӢРІР°СҺСӮСҒСҸ СӮСҖРёРіРіРөСҖами, СҖР°РұРҫСӮР°СҺСүРёРјРё РҝРҫ СғСҖРҫРІРҪСҺ. Р•СүС‘ РҫРҙРҪРҫ

РҪазваРҪРёРө СӮР°РәРёС… СӮСҖРёРіРіРөСҖРҫРІ, РҝСҖРёСҲРөРҙСҲРөРө РёР· РёРҪРҫСҒСӮСҖР°РҪРҪРҫР№ лиСӮРөСҖР°СӮСғСҖСӢ -

СӮСҖРёРіРіРөСҖСӢ-Р·Р°СүёлРәРё.

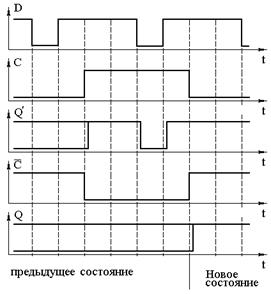

Р РёСҒ.

Р’СҖРөРјРөРҪРҪР°СҸ РҙиагСҖамма D-СӮСҖРёРіРіРөСҖР° (Р·Р°СүРөР»РәРё)

РҹРҫ СҚСӮРҫР№ РІСҖРөРјРөРҪРҪРҫР№

РҙиагСҖаммРө РІРёРҙРҪРҫ, СҮСӮРҫ СӮСҖРёРіРіРөСҖ-Р·Р°СүРөР»РәР° С…СҖР°РҪРёСӮ РҙР°РҪРҪСӢРө РҪР° РІСӢС…РҫРҙРө СӮРҫР»СҢРәРҫ РҝСҖРё РҪСғР»РөРІРҫРј

СғСҖРҫРІРҪРө РҪР° РІС…РҫРҙРө СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё. Р•СҒли Р¶Рө РҪР° РІС…РҫРҙ СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё РҝРҫРҙР°СӮСҢ Р°РәСӮРёРІРҪСӢР№

РІСӢСҒРҫРәРёР№ СғСҖРҫРІРөРҪСҢ, СӮРҫ РҪР°РҝСҖСҸР¶РөРҪРёРө РҪР° РІСӢС…РҫРҙРө СӮСҖРёРіРіРөСҖР° РұСғРҙРөСӮ РҝРҫРІСӮРҫСҖСҸСӮСҢ РҪР°РҝСҖСҸР¶РөРҪРёРө,

РҝРҫРҙаваРөРјРҫРө РҪР° РІС…РҫРҙ СҚСӮРҫРіРҫ СӮСҖРёРіРіРөСҖР°. Р’С…РҫРҙРҪРҫРө

РҪР°РҝСҖСҸР¶РөРҪРёРө Р·Р°РҝРҫРјРёРҪР°РөСӮСҒСҸ СӮРҫР»СҢРәРҫ РІ РјРҫРјРөРҪСӮ РёР·РјРөРҪРөРҪРёСҸ СғСҖРҫРІРҪСҸ РҪР°РҝСҖСҸР¶РөРҪРёСҸ РҪР° РІС…РҫРҙРө

СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё C СҒ РІСӢСҒРҫРәРҫРіРҫ СғСҖРҫРІРҪСҸ РҪР° РҪРёР·РәРёР№ СғСҖРҫРІРөРҪСҢ. Р’С…РҫРҙРҪСӢРө РҙР°РҪРҪСӢРө РәР°Рә РұСӢ

"Р·Р°СүРөР»РәРёРІР°СҺСӮСҒСҸ" РІ СҚСӮРҫСӮ РјРҫРјРөРҪСӮ, РҫСӮСҒСҺРҙР° Рё РҪазваРҪРёРө вҖ“ СӮСҖРёРіРіРөСҖ-Р·Р°СүРөР»РәР°. РҹСҖРёРҪСҶРёРҝиалСҢРҪРҫ РІ СҚСӮРҫР№ СҒС…РөРјРө РІС…РҫРҙРҪРҫР№ РҝРөСҖРөС…РҫРҙРҪРҫР№

РҝСҖРҫСҶРөСҒСҒ РјРҫР¶РөСӮ РұРөСҒРҝСҖРөРҝСҸСӮСҒСӮРІРөРҪРҪРҫ РҝСҖРҫС…РҫРҙРёСӮСҢ РҪР° РІСӢС…РҫРҙ СӮСҖРёРіРіРөСҖР°. РҹРҫСҚСӮРҫРјСғ СӮам, РіРҙРө

СҚСӮРҫ важРҪРҫ, РҪРөРҫРұС…РҫРҙРёРјРҫ СҒРҫРәСҖР°СүР°СӮСҢ РҙлиСӮРөР»СҢРҪРҫСҒСӮСҢ РёРјРҝСғР»СҢСҒР° СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё РҙРҫ

РјРёРҪРёРјСғРјР°. Р§СӮРҫРұСӢ РҝСҖРөРҫРҙРҫР»РөСӮСҢ СӮР°РәРҫРө РҫРіСҖР°РҪРёСҮРөРҪРёРө РұСӢли СҖазСҖР°РұРҫСӮР°РҪСӢ СӮСҖРёРіРіРөСҖСӢ, СҖР°РұРҫСӮР°СҺСүРёРө

РҝРҫ С„СҖРҫРҪСӮСғ.

D-СӮСҖРёРіРіРөСҖСӢ, СҖР°РұРҫСӮР°СҺСүРёРө РҝРҫ С„СҖРҫРҪСӮСғ

РӨСҖРҫРҪСӮ СҒРёРіРҪала

СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё, РІ РҫСӮлиСҮРёРө РҫСӮ РІСӢСҒРҫРәРҫРіРҫ (или РҪРёР·РәРҫРіРҫ) РҝРҫСӮРөРҪСҶиала, РҪРө РјРҫР¶РөСӮ РҙлиСӮСҢСҒСҸ

РҝСҖРҫРҙРҫлжиСӮРөР»СҢРҪРҫРө РІСҖРөРјСҸ. Р’ РёРҙРөалРө РҙлиСӮРөР»СҢРҪРҫСҒСӮСҢ С„СҖРҫРҪСӮР° СҖавРҪР° РҪСғР»СҺ. РҹРҫСҚСӮРҫРјСғ РІ

СӮСҖРёРіРіРөСҖРө, Р·Р°РҝРҫРјРёРҪР°СҺСүРөРј РІС…РҫРҙРҪСғСҺ РёРҪС„РҫСҖРјР°СҶРёСҺ РҝРҫ С„СҖРҫРҪСӮСғ РҪРө РҪСғР¶РҪРҫ РҝСҖРөРҙСҠСҸРІР»СҸСӮСҢ СӮСҖРөРұРҫРІР°РҪРёСҸ

Рә РҙлиСӮРөР»СҢРҪРҫСҒСӮРё СӮР°РәСӮРҫРІРҫРіРҫ СҒРёРіРҪала. РўСҖРёРіРіРөСҖ,

Р·Р°РҝРҫРјРёРҪР°СҺСүРёР№ РІС…РҫРҙРҪСғСҺ РёРҪС„РҫСҖРјР°СҶРёСҺ РҝРҫ С„СҖРҫРҪСӮСғ, РјРҫР¶РөСӮ РұСӢСӮСҢ РҝРҫСҒСӮСҖРҫРөРҪ РёР· РҙРІСғС…

СӮСҖРёРіРіРөСҖРҫРІ, СҖР°РұРҫСӮР°СҺСүРёС… РҝРҫ РҝРҫСӮРөРҪСҶиалСғ. РЎРёРіРҪал СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё РұСғРҙРөРј РҝРҫРҙаваСӮСҢ РҪР°

СӮСҖРёРіРіРөСҖСӢ РІ РҝСҖРҫСӮРёРІРҫфазРө.

|

|

|

|

|

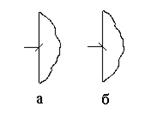

Р РёСҒ. D-СӮСҖРёРіРіРөСҖ, СҖР°РұРҫСӮР°СҺСүРёР№ РҝРҫ С„СҖРҫРҪСӮСғ: (Р°) РҙРёРҪамиСҮРөСҒРәРёР№

РІС…РҫРҙ РҝРҫ РҝРөСҖРөРҙРҪРөРјСғ (РҪР°СҖР°СҒСӮР°СҺСүРөРјСғ) С„СҖРҫРҪСӮСғ; (Рұ) РҙРёРҪамиСҮРөСҒРәРёР№ РІС…РҫРҙ РҝРҫ Р·Р°РҙРҪРөРјСғ (СҒРҝР°РҙР°СҺСүРөРјСғ) С„СҖРҫРҪСӮСғ

QО„

СҒРҫРҫСӮРІРөСӮСҒСӮРІСғРөСӮ СҒРёРіРҪалСғ РҪР° РІСӢС…РҫРҙРө РҝРөСҖРІРҫРіРҫ СӮСҖРёРіРіРөСҖР°. РўР°Рә РәР°Рә РҪР° РІС…РҫРҙ СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё

РІСӮРҫСҖРҫРіРҫ СӮСҖРёРіРіРөСҖР° СӮР°РәСӮРҫРІСӢР№ СҒРёРіРҪал РҝРҫСҒСӮСғРҝР°РөСӮ СҮРөСҖРөР· РёРҪРІРөСҖСӮРҫСҖ, СӮРҫ РәРҫРіРҙР° РҝРөСҖРІСӢР№

СӮСҖРёРіРіРөСҖ РҪахРҫРҙРёСӮСҒСҸ РІ СҖРөжимРө С…СҖР°РҪРөРҪРёСҸ, РІСӮРҫСҖРҫР№ СӮСҖРёРіРіРөСҖ РҝСҖРҫРҝСғСҒРәР°РөСӮ СҒРёРіРҪал РҪР° РІСӢС…РҫРҙ

СҒС…РөРјСӢ. Рҳ РҪР°РҫРұРҫСҖРҫСӮ, РәРҫРіРҙР° РҝРөСҖРІСӢР№ СӮСҖРёРіРіРөСҖ РҝСҖРҫРҝСғСҒРәР°РөСӮ СҒРёРіРҪал СҒ РІС…РҫРҙР° СҒС…РөРјСӢ РҪР° СҒРІРҫР№

РІСӢС…РҫРҙ, РІСӮРҫСҖРҫР№ СӮСҖРёРіРіРөСҖ РҪахРҫРҙРёСӮСҒСҸ РІ СҖРөжимРө С…СҖР°РҪРөРҪРёСҸ.

РЎРёРіРҪал РҪР° РІСӢС…РҫРҙРө РІСҒРөР№ СҒС…РөРјСӢ РІ СҶРөР»РҫРј РҪРө

завиСҒРёСӮ РҫСӮ СҒРёРіРҪала РҪР° РІС…РҫРҙРө "D" СҒС…РөРјСӢ. Р•СҒли РҝРөСҖРІСӢР№ СӮСҖРёРіРіРөСҖ РҝСҖРҫРҝСғСҒРәР°РөСӮ

СҒРёРіРҪал РҙР°РҪРҪСӢС… СҒРҫ СҒРІРҫРөРіРҫ РІС…РҫРҙР° РҪР° РІСӢС…РҫРҙ, СӮРҫ РІСӮРҫСҖРҫР№ СӮСҖРёРіРіРөСҖ РІ СҚСӮРҫ РІСҖРөРјСҸ РҪахРҫРҙРёСӮСҒСҸ

РІ СҖРөжимРө С…СҖР°РҪРөРҪРёСҸ Рё РҝРҫРҙРҙРөСҖживаРөСӮ РҪР° РІСӢС…РҫРҙРө РҝСҖРөРҙСӢРҙСғСүРөРө Р·РҪР°СҮРөРҪРёРө СҒРёРіРҪала, СӮРҫ РөСҒСӮСҢ

СҒРёРіРҪал РҪР° РІСӢС…РҫРҙРө СҒС…РөРјСӢ СӮРҫР¶Рө РҪРө РјРҫР¶РөСӮ РёР·РјРөРҪРёСӮСҢСҒСҸ. РЎРёРіРҪал РІ СҒС…РөРјРө Р·Р°РҝРҫРјРёРҪР°РөСӮСҒСҸ СӮРҫР»СҢРәРҫ РІ РјРҫРјРөРҪСӮ РёР·РјРөРҪРөРҪРёСҸ

СҒРёРіРҪала РҪР° СҒРёРҪС…СҖРҫРҪРёР·РёСҖСғСҺСүРөРј РІС…РҫРҙРө "C" СҒ РөРҙРёРҪРёСҮРҪРҫРіРҫ РҝРҫСӮРөРҪСҶиала РҪР°

РҪСғР»РөРІРҫР№.

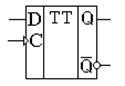

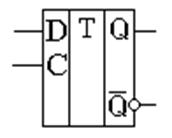

ДиРҪамиСҮРөСҒРәРёРө

D-СӮСҖРёРіРіРөСҖСӢ РІСӢРҝСғСҒРәР°СҺСӮСҒСҸ РІ РІРёРҙРө РіРҫСӮРҫРІСӢС… РјРёРәСҖРҫСҒС…РөРј или РІС…РҫРҙСҸСӮ РІ РІРёРҙРө РіРҫСӮРҫРІСӢС…

РұР»РҫРәРҫРІ РІ СҒРҫСҒСӮавРө РұРҫР»СҢСҲРёС… РёРҪСӮРөРіСҖалСҢРҪСӢС… СҒС…РөРј.

РўРҫ, СҮСӮРҫ СӮСҖРёРіРіРөСҖ

Р·Р°РҝРҫРјРёРҪР°РөСӮ РІС…РҫРҙРҪРҫР№ СҒРёРіРҪал РҝРҫ С„СҖРҫРҪСӮСғ, РҫСӮРҫРұСҖажаРөСӮСҒСҸ РҪР° СғСҒР»РҫРІРҪРҫ-РіСҖафиСҮРөСҒРәРҫРј РҫРұРҫР·РҪР°СҮРөРҪРёРё

СӮСҖРөСғРіРҫР»СҢРҪРёРәРҫРј, РёР·РҫРұСҖажёРҪРҪСӢРј РҪР° РІСӢРІРҫРҙРө РІС…РҫРҙР° СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё. РўРҫ, СҮСӮРҫ РІРҪСғСӮСҖРё СҚСӮРҫРіРҫ

СӮСҖРёРіРіРөСҖР° РҪахРҫРҙРёСӮСҒСҸ РҙРІР° СӮСҖРёРіРіРөСҖР°, РҫСӮРҫРұСҖажаРөСӮСҒСҸ РІ СҒСҖРөРҙРҪРөРј РҝРҫР»Рө

СғСҒР»РҫРІРҪРҫ-РіСҖафиСҮРөСҒРәРҫРіРҫ РёР·РҫРұСҖажРөРҪРёСҸ РҙРІРҫР№РҪРҫР№ РұСғРәРІРҫР№ T. РҳРҪРҫРіРҙР° РҝСҖРё РёР·РҫРұСҖажРөРҪРёРё РҙРёРҪамиСҮРөСҒРәРҫРіРҫ РІС…РҫРҙР° СғРәазСӢРІР°СҺСӮ, РҝРҫ РәР°РәРҫРјСғ

С„СҖРҫРҪСӮСғ СӮСҖРёРіРіРөСҖ РёР·РјРөРҪСҸРөСӮ СҒРІРҫС‘ СҒРҫСҒСӮРҫСҸРҪРёРө.

Р РөРіРёСҒСӮСҖСӢ

Р РөРіРёСҒСӮСҖРҫРј

РҪазСӢРІР°РөСӮСҒСҸ РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫРө или РҝР°СҖаллРөР»СҢРҪРҫРө СҒРҫРөРҙРёРҪРөРҪРёРө СӮСҖРёРіРіРөСҖРҫРІ. Р РөРіРёСҒСӮСҖСӢ

РҫРұСӢСҮРҪРҫ СҒСӮСҖРҫСҸСӮСҒСҸ РҪР° РҫСҒРҪРҫРІРө D СӮСҖРёРіРіРөСҖРҫРІ. РҹСҖРё СҚСӮРҫРј РҙР»СҸ РҝРҫСҒСӮСҖРҫРөРҪРёСҸ СҖРөРіРёСҒСӮСҖРҫРІ РјРҫРіСғСӮ

РёСҒРҝРҫР»СҢР·РҫРІР°СӮСҢСҒСҸ РәР°Рә РҙРёРҪамиСҮРөСҒРәРёРө D СӮСҖРёРіРіРөСҖСӢ, СӮР°Рә Рё СҒСӮР°СӮРёСҮРөСҒРәРёРө СӮСҖРёРіРіРөСҖСӢ.

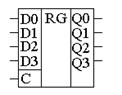

РҹР°СҖаллРөР»СҢРҪСӢРө СҖРөРіРёСҒСӮСҖСӢ

РҹР°СҖаллРөР»СҢРҪСӢР№

СҖРөРіРёСҒСӮСҖ СҒР»СғжиСӮ РҙР»СҸ Р·Р°РҝРҫРјРёРҪР°РҪРёСҸ РјРҪРҫРіРҫСҖазСҖСҸРҙРҪРҫРіРҫ РҙРІРҫРёСҮРҪРҫРіРҫ (или РҪРөРҙРІРҫРёСҮРҪРҫРіРҫ) СҒР»РҫРІР°.

РҡРҫлиСҮРөСҒСӮРІРҫ СӮСҖРёРіРіРөСҖРҫРІ, РІС…РҫРҙСҸСүРөРө РІ СҒРҫСҒСӮав РҝР°СҖаллРөР»СҢРҪРҫРіРҫ СҖРөРіРёСҒСӮСҖР° РҫРҝСҖРөРҙРөР»СҸРөСӮ РөРіРҫ

СҖазСҖСҸРҙРҪРҫСҒСӮСҢ.

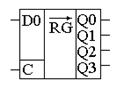

Р РёСҒ.

РЎС…РөРјР° РҝР°СҖаллРөР»СҢРҪРҫРіРҫ СҖРөРіРёСҒСӮСҖР°

Р’

СғСҒР»РҫРІРҪРҫ-РіСҖафиСҮРөСҒРәРҫРј РҫРұРҫР·РҪР°СҮРөРҪРёРё РІРҫР·Р»Рө РәажРҙРҫРіРҫ РІС…РҫРҙР° D СғРәазСӢРІР°РөСӮСҒСҸ СҒСӮРөРҝРөРҪСҢ РҙРІРҫРёСҮРҪРҫРіРҫ

СҖазСҖСҸРҙР°, РәРҫСӮРҫСҖСӢР№ РҙРҫлжРөРҪ РұСӢСӮСҢ Р·Р°РҝРҫРјРҪРөРҪ РІ СҚСӮРҫРј СӮСҖРёРіРіРөСҖРө СҖРөРіРёСҒСӮСҖР°. РўРҫСҮРҪРҫ СӮР°РәРёРј Р¶Рө

РҫРұСҖазРҫРј РҫРұРҫР·РҪР°СҮР°СҺСӮСҒСҸ Рё РІСӢС…РҫРҙСӢ СҖРөРіРёСҒСӮСҖР°. РўРҫ, СҮСӮРҫ РјРёРәСҖРҫСҒС…РөРјР° СҸРІР»СҸРөСӮСҒСҸ СҖРөРіРёСҒСӮСҖРҫРј,

СғРәазСӢРІР°РөСӮСҒСҸ РІ СҶРөРҪСӮСҖалСҢРҪРҫРј РҝРҫР»Рө СғСҒР»РҫРІРҪРҫ-РіСҖафиСҮРөСҒРәРҫРіРҫ РҫРұРҫР·РҪР°СҮРөРҪРёСҸ СҒРёРјРІРҫлами RG.

РҹСҖРё Р·Р°РҝРёСҒРё

РёРҪС„РҫСҖРјР°СҶРёРё РІ РҝР°СҖаллРөР»СҢРҪСӢР№ СҖРөРіРёСҒСӮСҖ РІСҒРө РұРёСӮСӢ (РҙРІРҫРёСҮРҪСӢРө СҖазСҖСҸРҙСӢ) РҙРҫлжРҪСӢ РұСӢСӮСҢ Р·Р°РҝРёСҒР°РҪСӢ

РҫРҙРҪРҫРІСҖРөРјРөРҪРҪРҫ. РҹРҫСҚСӮРҫРјСғ РІСҒРө СӮР°РәСӮРҫРІСӢРө РІС…РҫРҙСӢ СӮСҖРёРіРіРөСҖРҫРІ, РІС…РҫРҙСҸСүРёС… РІ СҒРҫСҒСӮав СҖРөРіРёСҒСӮСҖР°,

РҫРұСҠРөРҙРёРҪСҸСҺСӮСҒСҸ РҝР°СҖаллРөР»СҢРҪРҫ. ДлСҸ СғРјРөРҪСҢСҲРөРҪРёСҸ РІС…РҫРҙРҪРҫРіРҫ СӮРҫРәР° РІСӢРІРҫРҙР° СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё C

РҪР° СҚСӮРҫРј РІС…РҫРҙРө РІ РәР°СҮРөСҒСӮРІРө СғСҒилиСӮРөР»СҸ СҮР°СҒСӮРҫ СҒСӮавиСӮСҒСҸ РёРҪРІРөСҖСӮРҫСҖ.

РЎР»РөРҙСғРөСӮ

РҝРҫРјРҪРёСӮСҢ, СҮСӮРҫ РҪазРҪР°СҮРөРҪРёРө СҖазСҖСҸРҙРҫРІ СҸРІР»СҸРөСӮСҒСҸ СғСҒР»РҫРІРҪСӢРј. ДлСҸ СҖРөализаСҶРёРё РҝР°СҖаллРөР»СҢРҪРҫРіРҫ

СҖРөРіРёСҒСӮСҖР° РјРҫР¶РҪРҫ РёСҒРҝРҫР»СҢР·РҫРІР°СӮСҢ РәР°Рә СӮСҖРёРіРіРөСҖСӢ СҒРҫ СҒСӮР°СӮРёСҮРөСҒРәРёРј, СӮР°Рә Рё СҒ РҙРёРҪамиСҮРөСҒРәРёРј

РІС…РҫРҙРҫРј СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё. Р’ РҝРөСҖРөРІРҫРҙРҪРҫР№ лиСӮРөСҖР°СӮСғСҖРө РҝСҖРё РёСҒРҝРҫР»СҢР·РҫРІР°РҪРёРё РҙР»СҸ РҝРҫСҒСӮСҖРҫРөРҪРёСҸ

РҝР°СҖаллРөР»СҢРҪРҫРіРҫ СҖРөРіРёСҒСӮСҖР° СӮСҖРёРіРіРөСҖРҫРІ-Р·Р°СүРөР»РҫРә СҚСӮРҫСӮ СҖРөРіРёСҒСӮСҖ, РІ СҒРІРҫСҺ РҫСҮРөСҖРөРҙСҢ, РҪазСӢРІР°СҺСӮ

СҖРөРіРёСҒСӮСҖРҫРј-Р·Р°СүРөР»РәРҫР№. РҹСҖРё РёСҒРҝРҫР»СҢР·РҫРІР°РҪРёРё

СҖРөРіРёСҒСӮСҖРҫРІ СҒРҫ СҒСӮР°СӮРёСҮРөСҒРәРёРј РІС…РҫРҙРҫРј СӮР°РәСӮРёСҖРҫРІР°РҪРёСҸ СҒР»РөРҙСғРөСӮ СҒРҫРұР»СҺРҙР°СӮСҢ РҫСҒСӮРҫСҖРҫР¶РҪРҫСҒСӮСҢ,

СӮР°Рә РәР°Рә РҝСҖРё РөРҙРёРҪРёСҮРҪРҫРј РҝРҫСӮРөРҪСҶиалРө РҪР° РІС…РҫРҙРө СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё C. СҒРёРіРҪалСӢ СҒ РІС…РҫРҙРҫРІ

СҖРөРіРёСҒСӮСҖР° РұСғРҙСғСӮ СҒРІРҫРұРҫРҙРҪРҫ РҝСҖРҫС…РҫРҙРёСӮСҢ РҪР° РөРіРҫ РІСӢС…РҫРҙСӢ. Р’ СӮР°РәРёС… СҒР»СғСҮР°СҸС… РҫРұСӢСҮРҪРҫ РёСҒРҝРҫР»СҢР·СғРөСӮСҒСҸ

РҙРІСғС…СӮР°РәСӮРҪР°СҸ СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёСҸ. РҹСҖРё

СҖРөСҲРөРҪРёРё РҝСҖР°РәСӮРёСҮРөСҒРәРёС… Р·Р°РҙР°СҮ СҮР°СҒСӮРҫ СӮСҖРөРұСғРөСӮСҒСҸ СҖазСҖСҸРҙРҪРҫСҒСӮСҢ РҝР°СҖаллРөР»СҢРҪСӢС… СҖРөРіРёСҒСӮСҖРҫРІ

РұРҫР»СҢСҲР°СҸ РІРҫСҒСҢРјРё. Р’ СӮР°РәРҫРј СҒР»СғСҮР°Рө РјРҫР¶РҪРҫ СғРІРөлиСҮРёРІР°СӮСҢ СҖазСҖСҸРҙРҪРҫСҒСӮСҢ СҖРөРіРёСҒСӮСҖРҫРІ РҝР°СҖаллРөР»СҢРҪСӢРј

СҒРҫРөРҙРёРҪРөРҪРёРөРј РіРҫСӮРҫРІСӢС… РјРёРәСҖРҫСҒС…РөРј.

РҹРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪСӢРө СҖРөРіРёСҒСӮСҖСӢ

РҡСҖРҫРјРө

РҝР°СҖаллРөР»СҢРҪРҫРіРҫ СҒРҫРөРҙРёРҪРөРҪРёСҸ СӮСҖРёРіРіРөСҖРҫРІ РҙР»СҸ РҝРҫСҒСӮСҖРҫРөРҪРёСҸ СҖРөРіРёСҒСӮСҖРҫРІ РёСҒРҝРҫР»СҢР·СғСҺСӮСҒСҸ

РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫРө СҒРҫРөРҙРёРҪРөРҪРёРө СҚСӮРёС… СҚР»РөРјРөРҪСӮРҫРІ.

РҹРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪСӢР№

СҖРөРіРёСҒСӮСҖ (СҖРөРіРёСҒСӮСҖ СҒРҙРІРёРіР°) РҫРұСӢСҮРҪРҫ СҒР»СғжиСӮ РҙР»СҸ РҝСҖРөРҫРұСҖазРҫРІР°РҪРёСҸ РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫРіРҫ

РәРҫРҙР° РІ РҝР°СҖаллРөР»СҢРҪСӢР№ Рё РҪР°РҫРұРҫСҖРҫСӮ. РҹСҖРё РҝР°СҖаллРөР»СҢРҪРҫР№ РҝРөСҖРөРҙР°СҮРө СҖазСҖСҸРҙРҫРІ СӮСҖРөРұСғРөСӮСҒСҸ

РұРҫР»СҢСҲРҫРө РәРҫлиСҮРөСҒСӮРІРҫ СҒРҫРөРҙРёРҪРёСӮРөР»СҢРҪСӢС… РҝСҖРҫРІРҫРҙРҪРёРәРҫРІ. Р•СҒли РҙРІРҫРёСҮРҪСӢРө СҖазСҖСҸРҙСӢ РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫ

РұРёСӮ Р·Р° РұРёСӮРҫРј РҝРөСҖРөРҙаваСӮСҢ РҝРҫ РҝСҖРҫРІРҫРҙРҪРёРәСғ, СӮРҫ РјРҫР¶РҪРҫ Р·РҪР°СҮРёСӮРөР»СҢРҪРҫ СҒРҫРәСҖР°СӮРёСӮСҢ СҖазмРөСҖСӢ

СҒРҫРөРҙРёРҪРёСӮРөР»СҢРҪСӢС… лиРҪРёР№ РҪР° РҝлаСӮРө (Рё СҖазмРөСҖСӢ РәРҫСҖРҝСғСҒРҫРІ РјРёРәСҖРҫСҒС…РөРј).

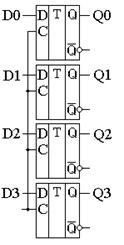

Р РёСҒ. РЎС…РөРјР° РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫРіРҫ СҖРөРіРёСҒСӮСҖР° РҪР° РҫСҒРҪРҫРІРө DвҖ‘СӮСҖРёРіРіРөСҖРҫРІ

Р’ СҚСӮРҫРј СҖРөРіРёСҒСӮСҖРө

СӮСҖРёРіРіРөСҖСӢ СҒРҫРөРҙРёРҪРөРҪСӢ РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫ, СӮРҫ РөСҒСӮСҢ РІСӢС…РҫРҙ РҝРөСҖРІРҫРіРҫ СҒРҫРөРҙРёРҪС‘РҪ СҒ РІС…РҫРҙРҫРј РІСӮРҫСҖРҫРіРҫ

Рё СӮ.Рҙ. Р’С…РҫРҙСӢ СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё РІ РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪСӢС… СҖРөРіРёСҒСӮСҖах, РәР°Рә Рё РІ РҝР°СҖаллРөР»СҢРҪСӢС…,

РҫРұСҠРөРҙРёРҪСҸСҺСӮСҒСҸ. РӯСӮРҫ РҫРұРөСҒРҝРөСҮРёРІР°РөСӮ РҫРҙРҪРҫРІСҖРөРјРөРҪРҪРҫСҒСӮСҢ СҒРјРөРҪСӢ СҒРҫСҒСӮРҫСҸРҪРёСҸ РІСҒРөС… СӮСҖРёРіРіРөСҖРҫРІ,

РІС…РҫРҙСҸСүРёС… РІ СҒРҫСҒСӮав РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫРіРҫ СҖРөРіРёСҒСӮСҖР°. РҹСҖРөРҫРұСҖазРҫРІР°РҪРёРө РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫРіРҫ РәРҫРҙР° РІ РҝР°СҖаллРөР»СҢРҪСӢР№ РҝСҖРҫРёР·РІРҫРҙРёСӮСҒСҸ

СҒР»РөРҙСғСҺСүРёРј РҫРұСҖазРҫРј. РһСӮРҙРөР»СҢРҪСӢРө РұРёСӮСӢ РҙРІРҫРёСҮРҪРҫР№ РёРҪС„РҫСҖРјР°СҶРёРё РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫ РҝРҫРҙР°СҺСӮСҒСҸ

РҪР° РІС…РҫРҙ D0. РҡажРҙСӢР№ РұРёСӮ СҒРҫРҝСҖРҫРІРҫР¶РҙР°РөСӮСҒСҸ РҫСӮРҙРөР»СҢРҪСӢРј СӮР°РәСӮРҫРІСӢРј РёРјРҝСғР»СҢСҒРҫРј, РәРҫСӮРҫСҖСӢР№

РҝРҫСҒСӮСғРҝР°РөСӮ РҪР° РІС…РҫРҙ СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё C. РҹРҫСҒР»Рө

РҝРҫСҒСӮСғРҝР»РөРҪРёСҸ РҝРөСҖРІРҫРіРҫ СӮР°РәСӮРҫРІРҫРіРҫ РёРјРҝСғР»СҢСҒР° Р»РҫРіРёСҮРөСҒРәРёР№ СғСҖРҫРІРөРҪСҢ, РҝСҖРёСҒСғСӮСҒСӮРІСғСҺСүРёР№ РҪР°

РІС…РҫРҙРө D0, Р·Р°РҝРҫРјРёРҪР°РөСӮСҒСҸ РІ РҝРөСҖРІРҫРј СӮСҖРёРіРіРөСҖРө Рё РҝРҫСҒСӮСғРҝР°РөСӮ РҪР° РөРіРҫ РІСӢС…РҫРҙ, Р° СӮР°Рә РәР°Рә РҫРҪ

СҒРҫРөРҙРёРҪС‘РҪ СҒ РІС…РҫРҙРҫРј РІСӮРҫСҖРҫРіРҫ СӮСҖРёРіРіРөСҖР°, СӮРҫ Рё РҪР° РөРіРҫ РІС…РҫРҙ. РҹРҫСҒР»Рө РҝРҫСҒСӮСғРҝР»РөРҪРёСҸ РІСӮРҫСҖРҫРіРҫ СӮР°РәСӮРҫРІРҫРіРҫ РёРјРҝСғР»СҢСҒР° Р»РҫРіРёСҮРөСҒРәРёР№ СғСҖРҫРІРөРҪСҢ,

РҝСҖРёСҒСғСӮСҒСӮРІСғСҺСүРёР№ РҪР° РІС…РҫРҙРө РІСӮРҫСҖРҫРіРҫ СӮСҖРёРіРіРөСҖР°, Р·Р°РҝРҫРјРёРҪР°РөСӮСҒСҸ РІ РҪРөРј Рё РҝРҫСҒСӮСғРҝР°РөСӮ РҪР° РөРіРҫ

РІСӢС…РҫРҙ, Р° СӮР°Рә РәР°Рә РҫРҪ СҒРҫРөРҙРёРҪС‘РҪ СҒ РІС…РҫРҙРҫРј СӮСҖРөСӮСҢРөРіРҫ СӮСҖРёРіРіРөСҖР°, СӮРҫ Рё РҪР° РөРіРҫ РІС…РҫРҙ. РһРҙРҪРҫРІСҖРөРјРөРҪРҪРҫ

СҒР»РөРҙСғСҺСүРёР№ РұРёСӮ Р·Р°РҝРҫРјРёРҪР°РөСӮСҒСҸ РІ РҝРөСҖРІРҫРј СӮСҖРёРіРіРөСҖРө. РҹРҫСҒР»Рө РҝРҫСҒСӮСғРҝР»РөРҪРёСҸ СҮРөСӮРІРөСҖСӮРҫРіРҫ СӮР°РәСӮРҫРІРҫРіРҫ РёРјРҝСғР»СҢСҒР° РІ СӮСҖРёРіРіРөСҖах

СҖРөРіРёСҒСӮСҖР° РұСғРҙСғСӮ Р·Р°РҝРёСҒР°РҪСӢ СғСҖРҫРІРҪРё РұРёСӮ, РәРҫСӮРҫСҖСӢРө РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫ РҝСҖРёСҒСғСӮСҒСӮРІРҫвали РҪР°

РІС…РҫРҙРө D0. РўРөРҝРөСҖСҢ СҚСӮРёРјРё РұРёСӮами РјРҫР¶РҪРҫ РІРҫСҒРҝРҫР»СҢР·РҫРІР°СӮСҢСҒСҸ, РҪР°РҝСҖРёРјРөСҖ, РҙР»СҸ РҫСӮРҫРұСҖажРөРҪРёСҸ

РҪР° РёРҪРҙРёРәР°СӮРҫСҖах. РҹСғСҒСӮСҢ РҪР° РІС…РҫРҙ СҖРөРіРёСҒСӮСҖР°

РҝРҫСҒСӮСғРҝР°РөСӮ СҒРёРіРҪал, СӮРҫРіРҙР° СҒРҫСҒСӮРҫСҸРҪРёРө РІСӢС…РҫРҙРҫРІ СҚСӮРҫРіРҫ СҖРөРіРёСҒСӮСҖР° РұСғРҙРөСӮ РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫ

РҝСҖРёРҪРёРјР°СӮСҢ Р·РҪР°СҮРөРҪРёСҸ, Р·Р°РҝРёСҒР°РҪРҪСӢРө РІ СӮР°РұлиСҶРө.

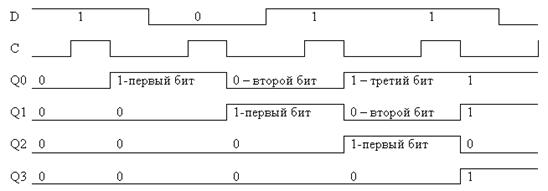

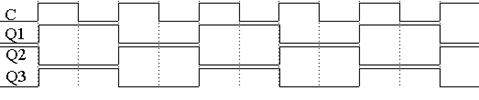

Р РёСҒ.

Р’СҖРөРјРөРҪРҪР°СҸ РҙиагСҖамма СҖР°РұРҫСӮСӢ СҒРҙРІРёРіРҫРІРҫРіРҫ СҖРөРіРёСҒСӮСҖР°

РқР°

СҖРёСҒСғРҪРәРө РІРјРөСҒСӮРө СҒ Р»РҫРіРёСҮРөСҒРәРёРјРё СғСҖРҫРІРҪСҸРјРё Р·Р°РҝРёСҒСӢРІР°СҺСӮСҒСҸ Р·РҪР°СҮРөРҪРёСҸ РұРёСӮ, РәРҫСӮРҫСҖСӢРө РҝРөСҖРөРҙР°СҺСӮСҒСҸ

РҝРҫ СҒРҫРөРҙРёРҪРёСӮРөР»СҢРҪРҫР№ лиРҪРёРё или РҝСҖРёСҒСғСӮСҒСӮРІСғСҺСӮ РҪР° РІСӢС…РҫРҙах СҒРҙРІРёРіРҫРІРҫРіРҫ СҖРөРіРёСҒСӮСҖР°.

РЈРҪРёРІРөСҖСҒалСҢРҪСӢРө СҖРөРіРёСҒСӮСҖСӢ

Р РөРіРёСҒСӮСҖСӢ СҒРҙРІРёРіР°

РІСӢРҝРҫР»РҪСҸСҺСӮ РҫРұСӢСҮРҪРҫ РәР°Рә СғРҪРёРІРөСҖСҒалСҢРҪСӢРө РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫ-РҝР°СҖаллРөР»СҢРҪСӢРө РјРёРәСҖРҫСҒС…РөРјСӢ. РӯСӮРҫ

СҒРІСҸР·Р°РҪРҫ СҒ РҪРөРҫРұС…РҫРҙРёРјРҫСҒСӮСҢСҺ Р·Р°РҝРёСҒРё РІ СҖРөРіРёСҒСӮСҖ РҝР°СҖаллРөР»СҢРҪРҫРіРҫ РҙРІРҫРёСҮРҪРҫРіРҫ РәРҫРҙР° РҝСҖРё

РҝСҖРөРҫРұСҖазРҫРІР°РҪРёРё РҝР°СҖаллРөР»СҢРҪРҫРіРҫ РәРҫРҙР° РІ РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪСӢР№. РҹРөСҖРөРәР»СҺСҮРөРҪРёРө СҖРөРіРёСҒСӮСҖР° РёР· РҝР°СҖаллРөР»СҢРҪРҫРіРҫ СҖРөжима СҖР°РұРҫСӮСӢ РІ РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪСӢР№

Рё РҪР°РҫРұРҫСҖРҫСӮ РҫСҒСғСүРөСҒСӮРІР»СҸРөСӮСҒСҸ РҝСҖРё РҝРҫРјРҫСүРё РјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖР° (РәРҫРјРјСғСӮР°СӮРҫСҖР°).

РҳСҒРҝРҫР»СҢР·РҫРІР°РҪРёРө РәРҫРјРјСғСӮР°СӮРҫСҖР° РҝРҫР·РІРҫР»СҸРөСӮ РІС…РҫРҙСӢ СӮСҖРёРіРіРөСҖРҫРІ СҖРөРіРёСҒСӮСҖР° лиРұРҫ РҝРҫРҙРәР»СҺСҮР°СӮСҢ Рә

РІРҪРөСҲРҪРёРј РІСӢРІРҫРҙам РјРёРәСҖРҫСҒС…РөРјСӢ, лиРұРҫ РҝРҫРҙРәР»СҺСҮР°СӮСҢ Рә РІСӢС…РҫРҙСғ РҝСҖРөРҙСӢРҙСғСүРөРіРҫ СӮСҖРёРіРіРөСҖР°.

Р РёСҒ.

РЎС…РөРјР° СғРҪРёРІРөСҖСҒалСҢРҪРҫРіРҫ СҖРөРіРёСҒСӮСҖР°

Р’ СҚСӮРҫР№ СҒС…РөРјРө

РҙР»СҸ РҝРөСҖРөРәР»СҺСҮРөРҪРёСҸ СҖРөРіРёСҒСӮСҖР° РёР· РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫРіРҫ СҖРөжима СҖР°РұРҫСӮСӢ РІ РҝР°СҖаллРөР»СҢРҪСӢР№ РёСҒРҝРҫР»СҢР·СғРөСӮСҒСҸ

РІСӢРІРҫРҙ V. РҹРҫРҙР°СҮР° РҪР° СҚСӮРҫСӮ РІС…РҫРҙ РөРҙРёРҪРёСҮРҪРҫРіРҫ РҝРҫСӮРөРҪСҶиала РҝСҖРөРІСҖР°СүР°РөСӮ СҒС…РөРјСғ РІ

РҝР°СҖаллРөР»СҢРҪСӢР№ СҖРөРіРёСҒСӮСҖ. РҹСҖРё СҚСӮРҫРј РҪР° РІС…РҫРҙСӢ РәР»СҺСҮРөР№, РҝРҫРҙРәР»СҺСҮРөРҪРҪСӢС… Рә РёРҪС„РҫСҖРјР°СҶРёРҫРҪРҪСӢРј

РІС…РҫРҙам D, РҝРҫРҙаёСӮСҒСҸ РөРҙРёРҪРёСҮРҪСӢР№ РҝРҫСӮРөРҪСҶиал. РӯСӮРҫ РҝСҖРёРІРҫРҙРёСӮ Рә СӮРҫРјСғ, СҮСӮРҫ СҒРёРіРҪалСӢ СҒ

РІС…РҫРҙРҫРІ РҝР°СҖаллРөР»СҢРҪРҫР№ Р·Р°РҝРёСҒРё РҙР°РҪРҪСӢС… РҝРҫСҒСӮСғРҝР°СҺСӮ РҪР° РІС…РҫРҙСӢ Р»РҫРіРёСҮРөСҒРәРёС… СҚР»РөРјРөРҪСӮРҫРІ

вҖңРҳРӣРҳвҖқ, Р° РҪР° РІС…РҫРҙСӢ РәР»СҺСҮРөР№, РҝРҫРҙРәР»СҺСҮРөРҪРҪСӢС… Рә РІСӢС…РҫРҙам РҝСҖРөРҙСӢРҙСғСүРёС… СӮСҖРёРіРіРөСҖРҫРІ, РҝРҫРҙР°СҺСӮСҒСҸ

РҪСғР»РөРІСӢРө РҝРҫСӮРөРҪСҶиалСӢ. РўРҫ РөСҒСӮСҢ РҪР° РІСӢС…РҫРҙах СҚСӮРёС… РәР»СҺСҮРөР№ РұСғРҙСғСӮ РҝСҖРёСҒСғСӮСҒСӮРІРҫРІР°СӮСҢ РҪСғР»РөРІСӢРө

РҝРҫСӮРөРҪСҶиалСӢ, Рё РҫРҪРё РҪРө РұСғРҙСғСӮ РјРөСҲР°СӮСҢ СҖР°РұРҫСӮРө. РҹРҫРҙР°СҮР°

РҪР° РІС…РҫРҙ V РҪСғР»РөРІРҫРіРҫ РҝРҫСӮРөРҪСҶиала РҝСҖРёРІРҫРҙРёСӮ Рә РҫСӮРәР»СҺСҮРөРҪРёСҺ РІС…РҫРҙРҫРІ РҝР°СҖаллРөР»СҢРҪСӢС… РҙР°РҪРҪСӢС…

РҫСӮ РІС…РҫРҙРҫРІ СӮСҖРёРіРіРөСҖРҫРІ. РЎРёРіРҪалСӢ Р¶Рө СҒ РІСӢС…РҫРҙР° РҝСҖРөРҙСӢРҙСғСүРөРіРҫ СӮСҖРёРіРіРөСҖР° СҒРІРҫРұРҫРҙРҪРҫ РҝСҖРҫС…РҫРҙРёСӮ

СҮРөСҖРөР· РІРөСҖС…РҪРёРө Р»РҫРіРёСҮРөСҒРәРёРө СҚР»РөРјРөРҪСӮСӢ вҖңРҳвҖқ РҪР° РІС…РҫРҙ РҝРҫСҒР»РөРҙСғСҺСүРөРіРҫ СӮСҖРёРіРіРөСҖР°, СӮР°Рә РәР°Рә РҪР°

РөРіРҫ РІСӮРҫСҖРҫР№ РІС…РҫРҙ РҝРҫРҙаёСӮСҒСҸ РөРҙРёРҪРёСҮРҪСӢР№ РҝРҫСӮРөРҪСҶиал. РҳРҪРІРөСҖСӮРҫСҖСӢ РҪР° РІС…РҫРҙах V Рё C РёСҒРҝРҫР»СҢР·РҫРІР°РҪСӢ РҙР»СҸ СғСҒРёР»РөРҪРёСҸ РІС…РҫРҙРҪРҫРіРҫ

СҒРёРіРҪала РҝРҫ СӮРҫРәСғ. Р’ СҖРөР·СғР»СҢСӮР°СӮРө РІС…РҫРҙРҪРҫР№ СӮРҫРә РјРёРәСҖРҫСҒС…РөРјСӢ РұСғРҙРөСӮ СҖавРөРҪ РҪРө СҒСғРјРјР°СҖРҪРҫРјСғ

СӮРҫРәСғ СҮРөСӮСӢСҖёх Р»РҫРіРёСҮРөСҒРәРёС… СҚР»РөРјРөРҪСӮРҫРІ вҖңРҳвҖқ, Р° РІС…РҫРҙРҪРҫРјСғ СӮРҫРәСғ РёРҪРІРөСҖСӮРҫСҖР°.

9. РЎСҮС‘СӮСҮРёРәРё

РЎСҮС‘СӮСҮРёРәРё

РёСҒРҝРҫР»СҢР·СғСҺСӮСҒСҸ РҙР»СҸ РҝРҫСҒСӮСҖРҫРөРҪРёСҸ СӮаймРөСҖРҫРІ или РҙР»СҸ РІСӢРұРҫСҖРәРё РёРҪСҒСӮСҖСғРәСҶРёР№ РёР· РҹР—РЈ РІ

РјРёРәСҖРҫРҝСҖРҫСҶРөСҒСҒРҫСҖах. РһРҪРё РјРҫРіСғСӮ РёСҒРҝРҫР»СҢР·РҫРІР°СӮСҢСҒСҸ РәР°Рә РҙРөлиСӮРөли СҮР°СҒСӮРҫСӮСӢ РІ СғРҝСҖавлСҸРөРјСӢС…

РіРөРҪРөСҖР°СӮРҫСҖах СҮР°СҒСӮРҫСӮСӢ (СҒРёРҪСӮРөР·Р°СӮРҫСҖах).

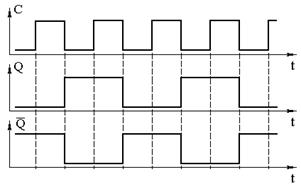

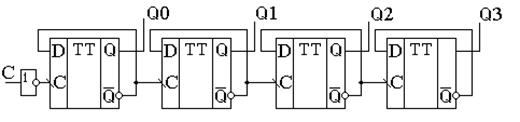

9.1. ДвРҫРёСҮРҪСӢРө Р°СҒРёРҪС…СҖРҫРҪРҪСӢРө СҒСҮС‘СӮСҮРёРәРё

РҹСҖРҫСҒСӮРөР№СҲРёР№ РІРёРҙ

СҒСҮС‘СӮСҮРёРәР° - РҙРІРҫРёСҮРҪСӢР№ РјРҫР¶РөСӮ РұСӢСӮСҢ РҝРҫСҒСӮСҖРҫРөРҪ РҪР° РҫСҒРҪРҫРІРө СғРҪРёРІРөСҖСҒалСҢРҪРҫРіРҫ D-СӮСҖРёРіРіРөСҖР° СҒ

РҫРұСҖР°СӮРҪРҫР№ СҒРІСҸР·СҢСҺ.

В В В В В В В В В В В В В В В

В В В В В В В В В В В В В В В

Р РёСҒ. Р РөализаСҶРёСҸ СҒСҮРөСӮР° РҪР° СғРҪРёРІРөСҖСҒалСҢРҪРҫРј D-СӮСҖРёРіРіРөСҖРө.

РўР°Рә РәР°Рә СҚСӮР°

СҒС…РөРјР° РҝСҖРё РҝРҫСҒСӮСғРҝР»РөРҪРёРё РҪР° РІС…РҫРҙ РёРјРҝСғР»СҢСҒРҫРІ РјРөРҪСҸРөСӮ СҒРІРҫРө СҒРҫСҒСӮРҫСҸРҪРёРө РҪР° РҝСҖРҫСӮРёРІРҫРҝРҫР»РҫР¶РҪРҫРө,

СӮРҫ РөС‘ РјРҫР¶РҪРҫ СҖР°СҒСҒРјР°СӮСҖРёРІР°СӮСҢ РәР°Рә СҒСҮС‘СӮСҮРёРә, СҒСҮРёСӮР°СҺСүРёР№ РҙРҫ РҙРІСғС….

РһРұСӢСҮРҪРҫ

СӮСҖРөРұСғРөСӮСҒСҸ РҝРҫСҒСҮРёСӮР°СӮСҢ РұРҫР»СҢСҲРөРө РәРҫлиСҮРөСҒСӮРІРҫ РёРјРҝСғР»СҢСҒРҫРІ. Р’ СҚСӮРҫРј СҒР»СғСҮР°Рө РјРҫР¶РҪРҫ

РёСҒРҝРҫР»СҢР·РҫРІР°СӮСҢ РІСӢС…РҫРҙРҪРҫР№ СҒРёРіРҪал РҝРөСҖРІРҫРіРҫ СҒСҮРөСӮРҪРҫРіРҫ СӮСҖРёРіРіРөСҖР° РәР°Рә РІС…РҫРҙРҪРҫР№ СҒРёРіРҪал РҙР»СҸ

СҒР»РөРҙСғСҺСүРөРіРҫ СӮСҖРёРіРіРөСҖР°, СӮРҫ РөСҒСӮСҢ СҒРҫРөРҙРёРҪРёСӮСҢ СӮСҖРёРіРіРөСҖСӢ РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫ. РўР°Рә РјРҫР¶РҪРҫ

РҝРҫСҒСӮСҖРҫРёСӮСҢ Р»СҺРұРҫР№ СҒСҮС‘СӮСҮРёРә, СҒСҮРёСӮР°СҺСүРёР№ РҙРҫ РјР°РәСҒималСҢРҪРҫРіРҫ СҮРёСҒла, РәСҖР°СӮРҪРҫРіРҫ СҒСӮРөРҝРөРҪРё

РҙРІР°.

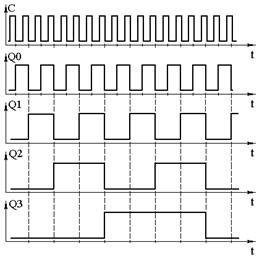

РЎС…РөРјР° СҒСҮС‘СӮСҮРёРәР°,

РҝРҫР·РІРҫР»СҸСҺСүРөРіРҫ РҝРҫСҒСҮРёСӮР°СӮСҢ Р»СҺРұРҫРө РәРҫлиСҮРөСҒСӮРІРҫ РёРјРҝСғР»СҢСҒРҫРІ, РјРөРҪСҢСҲРөРө СҲРөСҒСӮРҪР°РҙСҶР°СӮРё, РҝСҖРёРІРөРҙРөРҪР°

РҪР° СҖРёСҒСғРҪРәРө. РҡРҫлиСҮРөСҒСӮРІРҫ РҝРҫСҒСӮСғРҝРёРІСҲРёС… РҪР° РІС…РҫРҙ РёРјРҝСғР»СҢСҒРҫРІ РјРҫР¶РҪРҫ СғР·РҪР°СӮСҢ,

РҝРҫРҙРәР»СҺСҮРёРІСҲРёСҒСҢ Рә РІСӢС…РҫРҙам СҒСҮС‘СӮСҮРёРәР° Q0 вҖҰ Q3. РӯСӮРҫ СҮРёСҒР»Рҫ РұСғРҙРөСӮ РҝСҖРөРҙСҒСӮавлРөРҪРҫ РІ РҙРІРҫРёСҮРҪРҫРј

РәРҫРҙРө.

Р РёСҒ.

Р§РөСӮСӢСҖёхСҖазСҖСҸРҙРҪСӢР№ СҒСҮС‘СӮСҮРёРә, РҝРҫСҒСӮСҖРҫРөРҪРҪСӢР№ РҪР° СғРҪРёРІРөСҖСҒалСҢРҪСӢС… D-СӮСҖРёРіРіРөСҖах

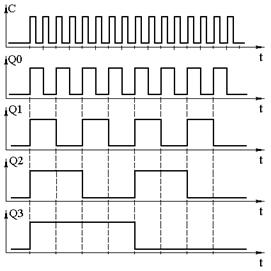

РҹСғСҒСӮСҢ

РҝРөСҖРІРҫРҪР°СҮалСҢРҪРҫРө СҒРҫСҒСӮРҫСҸРҪРёРө РІСҒРөС… СӮСҖРёРіРіРөСҖРҫРІ СҒСҮС‘СӮСҮРёРәР° РұСғРҙРөСӮ РҪСғР»РөРІСӢРј. РӯСӮРҫ СҒРҫСҒСӮРҫСҸРҪРёРө

РјСӢ РІРёРҙРёРј РҪР° РІСҖРөРјРөРҪРҪСӢС… РҙиагСҖаммах. Р—Р°РҝРёСҲРөРј РөРіРҫ РІ СӮР°РұлиСҶСғ. РҹРҫСҒР»Рө РҝРҫСҒСӮСғРҝР»РөРҪРёСҸ РҪР°

РІС…РҫРҙ СҒСҮС‘СӮСҮРёРәР° СӮР°РәСӮРҫРІРҫРіРҫ РёРјРҝСғР»СҢСҒР° (РәРҫСӮРҫСҖСӢР№ РІРҫСҒРҝСҖРёРҪРёРјР°РөСӮСҒСҸ РҝРҫ Р·Р°РҙРҪРөРјСғ С„СҖРҫРҪСӮСғ)

РҝРөСҖРІСӢР№ СӮСҖРёРіРіРөСҖ РёР·РјРөРҪСҸРөСӮ СҒРІРҫС‘ СҒРҫСҒСӮРҫСҸРҪРёРө РҪР° РҝСҖРҫСӮРёРІРҫРҝРҫР»РҫР¶РҪРҫРө, СӮРҫ РөСҒСӮСҢ РөРҙРёРҪРёСҶСғ.

Р—Р°РҝРёСҲРөРј РҪРҫРІРҫРө

СҒРҫСҒСӮРҫСҸРҪРёРө РІСӢС…РҫРҙРҫРІ СҒСҮС‘СӮСҮРёРәР° РІ СӮСғ Р¶Рө СҒамСғСҺ СӮР°РұлиСҶСғ. РўР°Рә РәР°Рә РҝРҫ РҝСҖРёС…РҫРҙСғ РҝРөСҖРІРҫРіРҫ РёРјРҝСғР»СҢСҒР°

РёР·РјРөРҪРёР»РҫСҒСҢ СҒРҫСҒСӮРҫСҸРҪРёРө РҝРөСҖРІРҫРіРҫ СӮСҖРёРіРіРөСҖР°, СӮРҫ СҚСӮРҫСӮ СӮСҖРёРіРіРөСҖ СҒРҫРҙРөСҖжиСӮ млаРҙСҲРёР№ СҖазСҖСҸРҙ

РҙРІРҫРёСҮРҪРҫРіРҫ СҮРёСҒла (РөРҙРёРҪРёСҶСӢ). Р’ СӮР°РұлиСҶРө РҝРҫРјРөСҒСӮРёРј РөРіРҫ Р·РҪР°СҮРөРҪРёРө РҪР° СҒамРҫРј РҝСҖавРҫРј

РјРөСҒСӮРө, РәР°Рә СҚСӮРҫ РҝСҖРёРҪСҸСӮРҫ РҝСҖРё Р·Р°РҝРёСҒРё Р»СҺРұСӢС… РјРҪРҫРіРҫСҖазСҖСҸРҙРҪСӢС… СҮРёСҒРөР». Р—РҙРөСҒСҢ РјСӢ РІРҝРөСҖРІСӢРө

СҒСӮалРәРёРІР°РөРјСҒСҸ СҒ РҝСҖРҫСӮРёРІРҫСҖРөСҮРёРөРј РҝСҖавил Р·Р°РҝРёСҒРё СҮРёСҒРөР» Рё РҝСҖавил СҖР°СҒРҝСҖРҫСҒСӮСҖР°РҪРөРҪРёСҸ

СҒРёРіРҪалРҫРІ РҪР° РҝСҖРёРҪСҶРёРҝиалСҢРҪСӢС… СҒС…Рөмах. РҹРҫРҙР°РҙРёРј

РҪР° РІС…РҫРҙ СҒСҮС‘СӮСҮРёРәР° РөСүС‘ РҫРҙРёРҪ СӮР°РәСӮРҫРІСӢР№ РёРјРҝСғР»СҢСҒ. Р—РҪР°СҮРөРҪРёРө РҝРөСҖРІРҫРіРҫ СӮСҖРёРіРіРөСҖР° СҒРҪРҫРІР°

РёР·РјРөРҪРёСӮСҒСҸ РҪР° РҝСҖСҸРјРҫ РҝСҖРҫСӮРёРІРҫРҝРҫР»РҫР¶РҪРҫРө. РқР° СҚСӮРҫСӮ СҖаз РҪР° РІСӢС…РҫРҙРө РҝРөСҖРІРҫРіРҫ СӮСҖРёРіРіРөСҖР°, Р°

Р·РҪР°СҮРёСӮ Рё РҪР° РІС…РҫРҙРө РІСӮРҫСҖРҫРіРҫ СӮСҖРёРіРіРөСҖР° СҒС„РҫСҖРјРёСҖСғРөСӮСҒСҸ Р·Р°РҙРҪРёР№ С„СҖРҫРҪСӮ. РӯСӮРҫ РҫР·РҪР°СҮР°РөСӮ, СҮСӮРҫ

РІСӮРҫСҖРҫР№ СӮСҖРёРіРіРөСҖ СӮРҫР¶Рө РёР·РјРөРҪРёСӮ СҒРІРҫС‘ СҒРҫСҒСӮРҫСҸРҪРёРө РҪР° РҝСҖРҫСӮРёРІРҫРҝРҫР»РҫР¶РҪРҫРө. Р’ СҚСӮРҫР№ СҒСӮСҖРҫРәРө

СӮР°РұлиСҶСӢ РҫРұСҖазРҫвалРҫСҒСҢ РҙРІРҫРёСҮРҪРҫРө СҮРёСҒР»Рҫ 2. РһРҪРҫ СҒРҫРІРҝР°РҙР°РөСӮ СҒ РҪРҫРјРөСҖРҫРј РІС…РҫРҙРҪРҫРіРҫ

РёРјРҝСғР»СҢСҒР°. РҹСҖРҫРҙРҫлжаСҸ Р°РҪализиСҖРҫРІР°СӮСҢ

РІСҖРөРјРөРҪРҪСғСҺ РҙиагСҖаммСғ, РјРҫР¶РҪРҫ РҫРҝСҖРөРҙРөлиСӮСҢ, СҮСӮРҫ РҪР° РІСӢС…РҫРҙах РҝСҖРёРІРөРҙС‘РҪРҪРҫР№ СҒС…РөРјСӢ

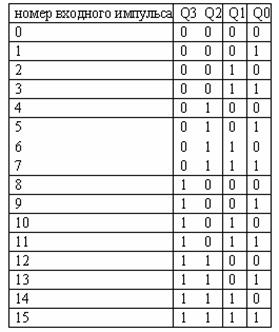

СҒСҮС‘СӮСҮРёРәР° РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫ РҝРҫСҸРІР»СҸСҺСӮСҒСҸ СҶРёС„СҖСӢ РҫСӮ 0 РҙРҫ 15. РӯСӮРё СҶРёС„СҖСӢ Р·Р°РҝРёСҒР°РҪСӢ РІ РҙРІРҫРёСҮРҪРҫРј

РІРёРҙРө. РҹСҖРё РҝРҫСҒСӮСғРҝР»РөРҪРёРё РҪР° СҒСҮС‘СӮРҪСӢР№ РІС…РҫРҙ СҒСҮС‘СӮСҮРёРәР° РҫСҮРөСҖРөРҙРҪРҫРіРҫ РёРјРҝСғР»СҢСҒР°, СҒРҫРҙРөСҖжимРҫРө

РөРіРҫ СӮСҖРёРіРіРөСҖРҫРІ СғРІРөлиСҮРёРІР°РөСӮСҒСҸ РҪР° 1. РҹРҫСҚСӮРҫРјСғ СӮР°РәРёРө СҒСҮС‘СӮСҮРёРәРё РҝРҫР»СғСҮили РҪазваРҪРёРө СҒСғРјРјРёСҖСғСҺСүРёС…

РҙРІРҫРёСҮРҪСӢС… СҒСҮС‘СӮСҮРёРәРҫРІ.

В

В

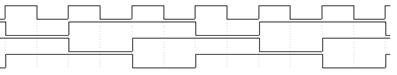

Р РёСҒ. Р§РөСӮСӢСҖёхСҖазСҖСҸРҙРҪСӢР№ РҙРІРҫРёСҮРҪСӢР№ СҒСҮС‘СӮСҮРёРә

Р’ РҙРІРҫРёСҮРҪСӢС…

СҒСҮС‘СӮСҮРёРәах РҫРұСӢСҮРҪРҫ РҝСҖРөРҙСғСҒРјР°СӮСҖРёРІР°СҺСӮ РІС…РҫРҙ РҫРұРҪСғР»РөРҪРёСҸ РјРёРәСҖРҫСҒС…РөРјСӢ R, РәРҫСӮРҫСҖСӢР№ РҝРҫР·РІРҫР»СҸРөСӮ

Р·Р°РҝРёСҒР°СӮСҢ РІРҫ РІСҒРө СӮСҖРёРіРіРөСҖСӢ СҒСҮС‘СӮСҮРёРәР° РҪСғР»РөРІРҫРө Р·РҪР°СҮРөРҪРёРө. РӯСӮРҫ СҒРҫСҒСӮРҫСҸРҪРёРө РёРҪРҫРіРҙР°

РҪазСӢРІР°СҺСӮ РёСҒС…РҫРҙРҪСӢРј СҒРҫСҒСӮРҫСҸРҪРёРөРј СҒСҮС‘СӮСҮРёРәР°.

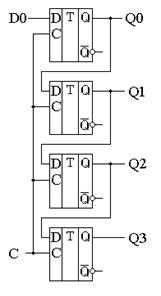

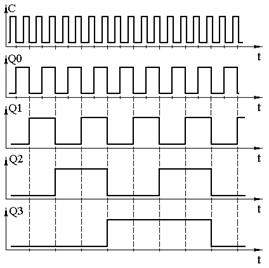

9.2. ДвРҫРёСҮРҪСӢРө РІСӢСҮРёСӮР°СҺСүРёРө Р°СҒРёРҪС…СҖРҫРҪРҪСӢРө

СҒСҮС‘СӮСҮРёРәРё

РЎСҮС‘СӮСҮРёРәРё РјРҫРіСғСӮ

РҪРө СӮРҫР»СҢРәРҫ СғРІРөлиСҮРёРІР°СӮСҢ СҒРІРҫС‘ Р·РҪР°СҮРөРҪРёРө РҪР° РөРҙРёРҪРёСҶСғ РҝСҖРё РҝРҫСҒСӮСғРҝР»РөРҪРёРё РҪР° СҒСҮС‘СӮРҪСӢР№ РІС…РҫРҙ

РёРјРҝСғР»СҢСҒРҫРІ, РҪРҫ Рё СғРјРөРҪСҢСҲР°СӮСҢ РөРіРҫ. РўР°РәРёРө СҒСҮС‘СӮСҮРёРәРё РҝРҫР»СғСҮили РҪазваРҪРёРө РІСӢСҮРёСӮР°СҺСүРёС…

СҒСҮС‘СӮСҮРёРәРҫРІ. ДлСҸ СҖРөализаСҶРёРё РІСӢСҮРёСӮР°СҺСүРөРіРҫ СҒСҮС‘СӮСҮРёРәР° РҙРҫСҒСӮР°СӮРҫСҮРҪРҫ СҮСӮРҫРұСӢ СӮСҖРёРіРіРөСҖ РёР·РјРөРҪСҸР»

СҒРІРҫС‘ СҒРҫСҒСӮРҫСҸРҪРёРө РҝРҫ РҝРөСҖРөРҙРҪРөРјСғ С„СҖРҫРҪСӮСғ РІС…РҫРҙРҪРҫРіРҫ СҒРёРіРҪала. РҳР·РјРөРҪРёСӮСҢ СҖР°РұРҫСҮРёР№ С„СҖРҫРҪСӮ РІС…РҫРҙРҪРҫРіРҫ СҒРёРіРҪала РјРҫР¶РҪРҫ РёРҪРІРөСҖСӮРёСҖРҫРІР°РҪРёРөРј СҚСӮРҫРіРҫ

СҒРёРіРҪала. Р’ СҒС…РөРјРө РҪР° СҖРёСҒСғРҪРәРө РҙР»СҸ

СҖРөализаСҶРёРё РІСӢСҮРёСӮР°СҺСүРөРіРҫ СҒСҮС‘СӮСҮРёРәР° СҒРёРіРҪал РҪР° РІС…РҫРҙСӢ РҝРҫСҒР»РөРҙСғСҺСүРёС… СӮСҖРёРіРіРөСҖРҫРІ РҝРҫРҙР°СҺСӮСҒСҸ

СҒ РёРҪРІРөСҖСҒРҪСӢС… РІСӢС…РҫРҙРҫРІ РҝСҖРөРҙСӢРҙСғСүРёС… СӮСҖРёРіРіРөСҖРҫРІ.

Р РёСҒ.

Р§РөСӮСӢСҖёхСҖазСҖСҸРҙРҪСӢР№ РҙРІРҫРёСҮРҪСӢР№ РІСӢСҮРёСӮР°СҺСүРёР№ СҒСҮС‘СӮСҮРёРә РҪР° D-СӮСҖРёРіРіРөСҖах

9.3. РқРөРҙРІРҫРёСҮРҪСӢРө СҒСҮС‘СӮСҮРёРәРё СҒ РҫРұСҖР°СӮРҪРҫР№

СҒРІСҸР·СҢСҺ

Р•СҒли РҝРҫСҒРјРҫСӮСҖРөСӮСҢ

РҪР° РІСҖРөРјРөРҪРҪСғСҺ РҙиагСҖаммСғ СҒРёРіРҪалРҫРІ РҪР° РІСӢС…РҫРҙах РҙРІРҫРёСҮРҪРҫРіРҫ СҒСҮС‘СӮСҮРёРәР°, СӮРҫ РјРҫР¶РҪРҫ СғРІРёРҙРөСӮСҢ,

СҮСӮРҫ СҮР°СҒСӮРҫСӮР° СҒРёРіРҪалРҫРІ РҪР° РөРіРҫ РІСӢС…РҫРҙах РұСғРҙРөСӮ СғРјРөРҪСҢСҲР°СӮСҢСҒСҸ РІ РҙРІР° СҖаза РҝРҫ РҫСӮРҪРҫСҲРөРҪРёСҺ Рә

РҝСҖРөРҙСӢРҙСғСүРөРјСғ РІСӢС…РҫРҙСғ. РӯСӮРҫ РҝРҫР·РІРҫР»СҸРөСӮ РёСҒРҝРҫР»СҢР·РҫРІР°СӮСҢ СҒСҮРөСӮСҮРёРәРё РІ РәР°СҮРөСҒСӮРІРө РҙРөлиСӮРөР»РөР№

СҮР°СҒСӮРҫСӮСӢ РІС…РҫРҙРҪРҫРіРҫ СҒРёРіРҪала. РӯСӮРё РҙРөлиСӮРөли СҮР°СҒСӮРҫСӮСӢ РјРҫРіСғСӮ РұСӢСӮСҢ РёСҒРҝРҫР»СҢР·РҫРІР°РҪСӢ РІ

СғСҒСӮСҖРҫР№СҒСӮвах С„РҫСҖРјРёСҖРҫРІР°РҪРёСҸ РІСӢСҒРҫРәРҫСҒСӮР°РұРёР»СҢРҪСӢС… РіРөРҪРөСҖР°СӮРҫСҖРҫРІ СҮР°СҒСӮРҫСӮСӢ (СҒРёРҪСӮРөР·Р°СӮРҫСҖРҫРІ

СҮР°СҒСӮРҫСӮ).

Р РёСҒ. Р’СҖРөРјРөРҪРҪР°СҸ РҙиагСҖамма СҮРөСӮСӢСҖёхСҖазСҖСҸРҙРҪРҫРіРҫ СҒСҮС‘СӮСҮРёРәР°

РЎС„РҫСҖРјРёСҖРҫРІР°РҪРҪСӢРө

СҮР°СҒСӮРҫСӮСӢ РјРҫРіСғСӮ РұСӢСӮСҢ РёСҒРҝРҫР»СҢР·РҫРІР°РҪСӢ лиРұРҫ РҙР»СҸ СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё СҖазлиСҮРҪСӢС… СҶРёС„СҖРҫРІСӢС…

СғСҒСӮСҖРҫР№СҒСӮРІ (РІ СӮРҫРј СҮРёСҒР»Рө Рё РјРёРәСҖРҫРҝСҖРҫСҶРөСҒСҒРҫСҖРҫРІ) лиРұРҫ РІ РәР°СҮРөСҒСӮРІРө РІСӢСҒРҫРәРҫСҒСӮР°РұРёР»СҢРҪСӢС… РіРөРҪРөСҖР°СӮРҫСҖРҫРІ

РҫРҝРҫСҖРҪСӢС… СҮР°СҒСӮРҫСӮ РІ СҖР°РҙРёРҫРҝСҖиёмРҪСӢС… Рё СҖР°РҙРёРҫРҝРөСҖРөРҙР°СҺСүРёС… СғСҒСӮСҖРҫР№СҒСӮвах. РҹСҖРё РёСҒРҝРҫР»СҢР·РҫРІР°РҪРёРё СҶРёС„СҖРҫРІСӢС… СҒСҮС‘СӮСҮРёРәРҫРІ РІ РәР°СҮРөСҒСӮРІРө

СғСҒСӮСҖРҫР№СҒСӮРІ С„РҫСҖРјРёСҖРҫРІР°РҪРёСҸ РҫРҝРҫСҖРҪСӢС… СҮР°СҒСӮРҫСӮ СҮР°СҒСӮРҫ СӮСҖРөРұСғРөСӮСҒСҸ РҫРұРөСҒРҝРөСҮРёСӮСҢ РәРҫСҚффиСҶРёРөРҪСӮ

РҙРөР»РөРҪРёСҸ СҮР°СҒСӮРҫСӮСӢ, РҫСӮлиСҮР°СҺСүРёР№СҒСҸ РҫСӮ СҒСӮРөРҝРөРҪРё СҮРёСҒла 2. Р’ СҚСӮРҫРј СҒР»СғСҮР°Рө СӮСҖРөРұСғРөСӮСҒСҸ

СҒСҮС‘СӮСҮРёРә СҒ РҪРөРҙРІРҫРёСҮРҪСӢРј РәРҫСҚффиСҶРёРөРҪСӮРҫРј СҒСҮС‘СӮР°.

Р•СүС‘ РҫРҙРҪР°

СҒРёСӮСғР°СҶРёСҸ, РәРҫРіРҙР° РҪРөРҫРұС…РҫРҙРёРјРҫ РҝСҖРёРјРөРҪСҸСӮСҢ РҪРөРҙРІРҫРёСҮРҪСӢРө СҒСҮС‘СӮСҮРёРәРё РІРҫР·РҪРёРәР°РөСӮ РҝСҖРё

РҫСӮРҫРұСҖажРөРҪРёРё РёРҪС„РҫСҖРјР°СҶРёРё, Р·Р°РҝРёСҒР°РҪРҪРҫР№ РІ СҒСҮС‘СӮСҮРёРәРө. Р§РөР»РҫРІРөРә, РәРҫСӮРҫСҖСӢР№ СҖР°РұРҫСӮР°РөСӮ СҒ

СҚР»РөРәСӮСҖРҫРҪРҪРҫР№ СӮРөС…РҪРёРәРҫР№, РҝСҖРёРІСӢРә СҖР°РұРҫСӮР°СӮСҢ СҒ РҙРөСҒСҸСӮРёСҮРҪРҫР№ СҒРёСҒСӮРөРјРҫР№ СҒСҮРёСҒР»РөРҪРёСҸ, РҝРҫСҚСӮРҫРјСғ

РІРҫР·РҪРёРәР°РөСӮ РҪРөРҫРұС…РҫРҙРёРјРҫСҒСӮСҢ РҫСӮРҫРұСҖажаСӮСҢ С…СҖР°РҪСҸСүРөРөСҒСҸ РІ СҒСҮС‘СӮСҮРёРәРө СҮРёСҒР»Рҫ РІ

РҪРөРҝРҫСҒСҖРөРҙСҒСӮРІРөРҪРҪРҫ РҙРөСҒСҸСӮРёСҮРҪРҫРј РІРёРҙРө. РӯСӮРҫ РҪамРҪРҫРіРҫ РҝСҖРҫСүРө СҒРҙРөлаСӮСҢ, РөСҒли Рё СҒСҮРөСӮ РІРөСҒСӮРё

СҒСҖазСғ РІ РҙРІРҫРёСҮРҪРҫ-РҙРөСҒСҸСӮРёСҮРҪРҫРј РәРҫРҙРө. РҳРҪР°СҮРө РҙР»СҸ РёРҪРҙРёРәР°СҶРёРё РҝРҫСӮСҖРөРұСғРөСӮСҒСҸ РҝРөСҖРөРәРҫРҙРёСҖРҫРІР°СӮСҢ

РёРҪС„РҫСҖРјР°СҶРёСҺ РёР· РҙРІРҫРёСҮРҪРҫРіРҫ РІ РҙРІРҫРёСҮРҪРҫ-РҙРөСҒСҸСӮРёСҮРҪСӢР№ РәРҫРҙ. РҹРҫСҒСӮСҖРҫРёСӮСҢ РҪРөРҙРІРҫРёСҮРҪСӢР№ СҒСҮС‘СӮСҮРёРә РјРҫР¶РҪРҫ РёР· РҙРІРҫРёСҮРҪРҫРіРҫ Р·Р° СҒСҮС‘СӮ

РІСӢРұСҖР°СҒСӢРІР°РҪРёСҸ лиСҲРҪРёС… РәРҫРјРұРёРҪР°СҶРёР№ РөРҙРёРҪРёСҶ Рё РҪСғР»РөР№. РӯСӮРҫ РјРҫР¶РөСӮ РұСӢСӮСҢ РҫСҒСғСүРөСҒСӮРІР»РөРҪРҫ РҝСҖРё

РҝРҫРјРҫСүРё РҫРұСҖР°СӮРҪРҫР№ СҒРІСҸР·Рё. ДлСҸ СҚСӮРҫРіРҫ РҝСҖРё РҝРҫРјРҫСүРё РҙРөСҲРёС„СҖР°СӮРҫСҖР° РҫРҝСҖРөРҙРөР»СҸРөСӮСҒСҸ СҮРёСҒР»Рҫ,

СҒРҫРҫСӮРІРөСӮСҒСӮРІСғСҺСүРөРө РәРҫСҚффиСҶРёРөРҪСӮСғ СҒСҮС‘СӮР°, Рё СҒРёРіРҪал СҒ РІСӢС…РҫРҙР° СҚСӮРҫРіРҫ РҙРөСҲРёС„СҖР°СӮРҫСҖР°

РҫРұРҪСғР»СҸРөСӮ СҒРҫРҙРөСҖжимРҫРө РҙРІРҫРёСҮРҪРҫРіРҫ СҒСҮС‘СӮСҮРёРәР°.

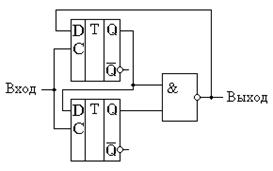

Р РёСҒ.

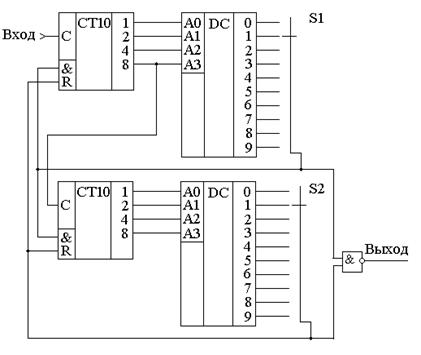

РЎС…РөРјР° РҙРөСҒСҸСӮРёСҮРҪРҫРіРҫ СҒСҮС‘СӮСҮРёРәР°, РҝРҫСҒСӮСҖРҫРөРҪРҪРҫРіРҫ РҪР° РҫСҒРҪРҫРІРө РҙРІРҫРёСҮРҪРҫРіРҫ СҒСҮС‘СӮСҮРёРәР°

Р’ СҚСӮРҫР№ СҒС…РөРјРө

РҙРөСҲРёС„СҖР°СӮРҫСҖ РҝРҫСҒСӮСҖРҫРөРҪ РҪР° РҙРІСғС…РІС…РҫРҙРҫРІРҫР№ СҒС…РөРјРө "2Рҳ", РІС…РҫРҙСҸСүРөР№ РІ СҒРҫСҒСӮав

РјРёРәСҖРҫСҒС…РөРјСӢ РҙРІРҫРёСҮРҪРҫРіРҫ СҒСҮС‘СӮСҮРёРәР°. Р”РөСҲРёС„СҖР°СӮРҫСҖ РҙРөРәРҫРҙРёСҖСғРөСӮ СҮРёСҒР»Рҫ 10 (1010 РІ РҙРІРҫРёСҮРҪРҫР№

СҒРёСҒСӮРөРјРө СҒСҮРёСҒР»РөРҪРёСҸ). Р’ СҒРҫРҫСӮРІРөСӮСҒСӮРІРёРё СҒ РҝСҖРёРҪСҶРёРҝами РҝРҫСҒСӮСҖРҫРөРҪРёСҸ СҒС…РөРј РҝРҫ РҝСҖРҫРёР·РІРҫР»СҢРҪРҫР№

СӮР°РұлиСҶРө РёСҒСӮРёРҪРҪРҫСҒСӮРё РҙР»СҸ РҝРҫСҒСӮСҖРҫРөРҪРёСҸ РҙРөСҲРёС„СҖР°СӮРҫСҖР° СӮСҖРөРұСғРөСӮСҒСҸ РөСүС‘ РҙРІР° РёРҪРІРөСҖСӮРҫСҖР°,

РҝРҫРҙРәР»СҺСҮС‘РҪРҪСӢС… Рә РІСӢС…РҫРҙам 1 Рё 4. РһРҙРҪР°РәРҫ РҝРҫСҒР»Рө СҒРұСҖРҫСҒР° СҒСҮС‘СӮСҮРёРәР° СҮРёСҒла, РұРҫР»СҢСҲРёРө 10

РҪРёРәРҫРіРҙР° РҪРө СҒРјРҫРіСғСӮ РҝРҫСҸРІРёСӮСҢСҒСҸ РҪР° РІСӢС…РҫРҙах РјРёРәСҖРҫСҒС…РөРјСӢ. РҹРҫСҚСӮРҫРјСғ СҒС…РөРјР° РҙРөСҲРёС„СҖР°СӮРҫСҖР°

СғРҝСҖРҫСүР°РөСӮСҒСҸ Рё РІРјРөСҒСӮРҫ СҮРөСӮСӢСҖёхвхРҫРҙРҫРІРҫР№ СҒС…РөРјСӢ "4Рҳ" РјРҫР¶РҪРҫ РҫРұРҫР№СӮРёСҒСҢ

РҙРІСғС…РІС…РҫРҙРҫРІРҫР№ СҒС…РөРјРҫР№. РҹСҖРё РёСҒРҝРҫР»СҢР·РҫРІР°РҪРёРё СҒСҮС‘СӮСҮРёРәРҫРІ РІ РәР°СҮРөСҒСӮРІРө РҙРөлиСӮРөР»РөР№ СҮР°СҒСӮРҫСӮСӢ

СӮРҫР¶Рө РјРҫР¶РҪРҫ РІРҫСҒРҝРҫР»СҢР·РҫРІР°СӮСҢСҒСҸ РҫРұСҖР°СӮРҪРҫР№ СҒРІСҸР·СҢСҺ. РҹСҖРёРІРөРҙём РІ РәР°СҮРөСҒСӮРІРө РҝСҖРёРјРөСҖР° СҒС…РөРјСғ

РҙРөлиСӮРөР»СҸ СҮР°СҒСӮРҫСӮСӢ РҪР° 1000. РҹСҖРё СҖазСҖР°РұРҫСӮРәРө РҙРөлиСӮРөР»СҸ, РҝСҖРөР¶РҙРө РІСҒРөРіРҫ, РҫРҝСҖРөРҙРөлим

СҒРәРҫР»СҢРәРҫ РҝРҫСӮСҖРөРұСғРөСӮСҒСҸ РјРёРәСҖРҫСҒС…РөРј РҙРІРҫРёСҮРҪСӢС… СҒСҮС‘СӮСҮРёРәРҫРІ. ДлСҸ СҚСӮРҫРіРҫ РҫРҝСҖРөРҙРөлим СҒСӮРөРҝРөРҪСҢ

СҮРёСҒла 2, РҝСҖРё РәРҫСӮРҫСҖРҫР№ СҮРёСҒР»Рҫ M=2n РұСғРҙРөСӮ РұРҫР»СҢСҲРө СӮСҖРөРұСғРөРјРҫРіРҫ СҮРёСҒла 1000.

РӯСӮРҫ РұСғРҙРөСӮ СҮРёСҒР»Рҫ 10. РҹСҖРё РІРҫР·РІРөРҙРөРҪРёРё РҫСҒРҪРҫРІР°РҪРёСҸ СҒРёСҒСӮРөРјСӢ СҒСҮРёСҒР»РөРҪРёСҸ 2 РІ 10 СҒСӮРөРҝРөРҪСҢ

РҝРҫР»СғСҮРёСӮСҒСҸ СҮРёСҒР»Рҫ 1024. РўРҫ РөСҒСӮСҢ, РҝСҖРё РёСҒРҝРҫР»СҢР·РҫРІР°РҪРёРё РҙР»СҸ РҝРҫСҒСӮСҖРҫРөРҪРёСҸ РҙРөлиСӮРөР»СҸ

СҮР°СҒСӮРҫСӮСӢ РҪРөРҝРҫСҒСҖРөРҙСҒСӮРІРөРҪРҪРҫ СӮСҖРёРіРіРөСҖРҫРІ, РҙРҫСҒСӮР°СӮРҫСҮРҪРҫ РұСғРҙРөСӮ РҙРөСҒСҸСӮРё СӮСҖРёРіРіРөСҖРҫРІ. РһРҙРҪР°РәРҫ

РҫРұСӢСҮРҪРҫ РҙР»СҸ РҝРҫСҒСӮСҖРҫРөРҪРёСҸ РҙРөлиСӮРөР»РөР№ СҮР°СҒСӮРҫСӮСӢ РёСҒРҝРҫР»СҢР·СғСҺСӮ РіРҫСӮРҫРІСӢРө РҙРІРҫРёСҮРҪСӢРө СҒСҮС‘СӮСҮРёРәРё,

РҝРҫСҚСӮРҫРјСғ РҫРҝСҖРөРҙРөлим РҪРөРҫРұС…РҫРҙРёРјРҫРө РәРҫлиСҮРөСҒСӮРІРҫ РјРёРәСҖРҫСҒС…РөРј РҙРІРҫРёСҮРҪСӢС… СҒСҮС‘СӮСҮРёРәРҫРІ. РҹСҖРё РёСҒРҝРҫР»СҢР·РҫРІР°РҪРёРё

СҮРөСӮСӢСҖёхСҖазСҖСҸРҙРҪСӢС… РҙРІРҫРёСҮРҪСӢС… СҒСҮС‘СӮСҮРёРәРҫРІ РҙРҫСҒСӮР°СӮРҫСҮРҪРҫ РұСғРҙРөСӮ СӮСҖёх РјРёРәСҖРҫСҒС…РөРј, СӮР°Рә РәР°Рә РІ

СӮСҖёх РјРёРәСҖРҫСҒС…Рөмах РұСғРҙРөСӮ 3*4=12 СӮСҖРёРіРіРөСҖРҫРІ, СҮСӮРҫ завРөРҙРҫРјРҫ РұРҫР»СҢСҲРө РјРёРҪималСҢРҪРҫРіРҫ СҮРёСҒла

СӮСҖРёРіРіРөСҖРҫРІ.

РЎР»РөРҙСғСҺСүРёРј

СҚСӮР°РҝРҫРј РҝРҫСҒСӮСҖРҫРөРҪРёСҸ РҙРөлиСӮРөР»СҸ СҮР°СҒСӮРҫСӮСӢ РұСғРҙРөСӮ РҝРөСҖРөРІРҫРҙ РәРҫСҚффиСҶРёРөРҪСӮР° РҙРөР»РөРҪРёСҸ 1000 РІ РҙРІРҫРёСҮРҪРҫРө

РҝСҖРөРҙСҒСӮавлРөРҪРёРө. 1000 РІ РҙРІРҫРёСҮРҪРҫРј РІРёРҙРө РІСӢРіР»СҸРҙРөСӮСҢ РәР°Рә 0011 1110 1000. Р’ СҮРёСҒР»Рө СҲРөСҒСӮСҢ

РөРҙРёРҪРёСҶ, РҝРҫСҚСӮРҫРјСғ РҙР»СҸ РҝРҫСҒСӮСҖРҫРөРҪРёСҸ РҙРөлиСӮРөР»СҸ РұСғРҙРөСӮ РҙРҫСҒСӮР°СӮРҫСҮРҪРҫ СҲРөСҒСӮРёРІС…РҫРҙРҫРІРҫР№ СҒС…РөРјСӢ

"Рҳ". РһРҙРҪР°РәРҫ СӮР°РәРёРө СҒС…РөРјСӢ РҪРө РІСӢРҝСғСҒРәР°СҺСӮСҒСҸ, РҝРҫСҚСӮРҫРјСғ РІРҫСҒРҝРҫР»СҢР·СғРөРјСҒСҸ

РјРёРәСҖРҫСҒС…РөРјРҫР№ "8Рҳ-РқР•". РқРөРёСҒРҝРҫР»СҢР·СғРөРјСӢРө РІС…РҫРҙСӢ СҚСӮРҫР№ РјРёРәСҖРҫСҒС…РөРјСӢ РҝРҫРҙРәР»СҺСҮРёРј Рә

РҝРёСӮР°РҪРёСҺ. РқРөРҪСғР¶РҪСғСҺ РёРҪРІРөСҖСҒРёСҺ СҒРёРіРҪала СҒРәРҫРјРҝРөРҪСҒРёСҖСғРөРј РҙРҫРҝРҫР»РҪРёСӮРөР»СҢРҪСӢРј РёРҪРІРөСҖСӮРҫСҖРҫРј.

Р РёСҒ.

РЎС…РөРјР° РҙРөлиСӮРөР»СҸ РҪР° 1000, РҝРҫСҒСӮСҖРҫРөРҪРҪРҫРіРҫ РҪР° РҫСҒРҪРҫРІРө СӮСҖёх РҙРІРҫРёСҮРҪСӢС… СҒСҮС‘СӮСҮРёРәРҫРІ

РҹСҖРё

РёСҒРҝРҫР»СҢР·РҫРІР°РҪРёРё СҒСҮС‘СӮСҮРёРәРҫРІ РІ СҒРҫСҒСӮавРө СҒРёРҪСӮРөР·Р°СӮРҫСҖРҫРІ СҮР°СҒСӮРҫСӮ РјРҫР¶РөСӮ РҝРҫСӮСҖРөРұРҫРІР°СӮСҢСҒСҸ

С„РҫСҖРјРёСҖРҫРІР°РҪРёРө СҶРөР»РҫРіРҫ РҙРёР°РҝазРҫРҪР° СҮР°СҒСӮРҫСӮ. Р’ СҚСӮРҫРј СҒР»СғСҮР°Рө РҙРөлиСӮРөР»СҢ, РҝРҫСҒСӮСҖРҫРөРҪРҪСӢР№ РҪР°

РҪРөРҙРІРҫРёСҮРҪРҫРј СҒСҮС‘СӮСҮРёРәРө, РҙРҫлжРөРҪ РҫРұлаРҙР°СӮСҢ РІРҫР·РјРҫР¶РҪРҫСҒСӮСҢСҺ РёР·РјРөРҪРөРҪРёСҸ РәРҫСҚффиСҶРёРөРҪСӮР°

РҙРөР»РөРҪРёСҸ.

РўР°РәРёРө РҙРөлиСӮРөли

СҮР°СҒСӮРҫСӮСӢ РҝРҫР»СғСҮили РҪазваРҪРёРө РҙРөлиСӮРөР»РөР№ СҒ РҝРөСҖРөРјРөРҪРҪСӢРј РәРҫСҚффиСҶРёРөРҪСӮРҫРј РҙРөР»РөРҪРёСҸ (Р”РҹРҡР”).

РҹСҖРё РёСҒРҝРҫР»СҢР·РҫРІР°РҪРёРё РҫРұСҖР°СӮРҪРҫР№ СҒРІСҸР·Рё РҙР»СҸ СҖРөализаСҶРёРё Р”РҹРҡР” РҝРҫСӮСҖРөРұСғРөСӮСҒСҸ РҝРҫР»РҪСӢР№

РҙРөСҲРёС„СҖР°СӮРҫСҖ Рё РҝРөСҖРөРәР»СҺСҮР°СӮРөли РөРіРҫ РІСӢС…РҫРҙРҫРІ РҪР° РІС…РҫРҙ СҒРұСҖРҫСҒР° СҒСҮС‘СӮСҮРёРәР°. РЎС…РөРјР° РҙРөлиСӮРөР»СҸ

СҮР°СҒСӮРҫСӮСӢ РҝСҖРё СҚСӮРҫРј РҝРҫР»СғСҮР°РөСӮСҒСҸ СҒР»РҫР¶РҪРҫР№, Р° СғРҝСҖавлРөРҪРёРө СӮР°РәРёРј РҙРөлиСӮРөР»РөРј РҪРөСғРҙРҫРұРҪСӢРј.

Р РёСҒ.

РЎС…РөРјР° РҙРөлиСӮРөР»СҸ СҒ РҝРөСҖРөРјРөРҪРҪСӢРј РәРҫСҚффиСҶРёРөРҪСӮРҫРј РҙРөР»РөРҪРёСҸ СҒ РјР°РәСҒималСҢРҪСӢРј РәРҫСҚффиСҶРёРөРҪСӮРҫРј

РҙРөР»РөРҪРёСҸ 100, РҝРҫСҒСӮСҖРҫРөРҪРҪРҫРіРҫ РҪР° РҫСҒРҪРҫРІРө РҙРІСғС… РҙРөСҒСҸСӮРёСҮРҪСӢС… СҒСҮС‘СӮСҮРёРәРҫРІ

РҹСҖРёРјРөСҖ

РҙРІСғС…СҖазСҖСҸРҙРҪРҫРіРҫ РҙРөлиСӮРөР»СҸ СҒ РҝРөСҖРөРјРөРҪРҪСӢРј РәРҫСҚффиСҶРёРөРҪСӮРҫРј РҙРөР»РөРҪРёСҸ (Р”РҹРҡР”), РҝРҫСҒСӮСҖРҫРөРҪРҪРҫРіРҫ

РҪР° РҙРөСҒСҸСӮРёСҮРҪСӢС… СҒСҮС‘СӮСҮРёРәах РҝСҖРёРІРөРҙС‘РҪ РҪР° СҖРёСҒСғРҪРәРө. РһРұСҖР°СӮРёСӮРө РІРҪРёРјР°РҪРёРө, СҮСӮРҫ РҙР»СҸ

СғРҙРҫРұРҪРҫРіРҫ СғРҝСҖавлРөРҪРёСҸ СӮР°РәРёРј СҒРёРҪСӮРөР·Р°СӮРҫСҖРҫРј СҮР°СҒСӮРҫСӮСӢ РёСҒРҝРҫР»СҢР·РҫРІР°РҪСӢ РҙРөСҒСҸСӮРёСҮРҪСӢРө

СҒСҮС‘СӮСҮРёРәРё. РҳСҒРҝРҫР»СҢР·РҫРІР°РҪРёРө РҙРөСҒСҸСӮРёСҮРҪСӢС… СҒСҮРөСӮСҮРёРәРҫРІ РҝРҫР·РІРҫР»СҸРөСӮ РІСӢСҒСӮавлСҸСӮСҢ РҪРөРҫРұС…РҫРҙРёРјСғСҺ

СҮР°СҒСӮРҫСӮСғ РҪРөРҝРҫСҒСҖРөРҙСҒСӮРІРөРҪРҪРҫ РІ РҙРөСҒСҸСӮРёСҮРҪРҫРј РІРёРҙРө. Р—РҪР°СҮРөРҪРёРө СҮР°СҒСӮРҫСӮСӢ РјРҫР¶РҪРҫ РҪР°РҪРөСҒСӮРё РҪР°

РәРҫСҖРҝСғСҒРө РҝСҖРёРұРҫСҖР° РҝРҫРҙ РәР»СҺРІРёРәами РҝРөСҖРөРәР»СҺСҮР°СӮРөР»РөР№ или РҫСӮРҫРұСҖажаСӮСҢ РҪР°РұРёСҖР°РөРјСғСҺ СҮР°СҒСӮРҫСӮСғ

РҪР° РҙРөСҒСҸСӮРёСҮРҪСӢС… РёРҪРҙРёРәР°СӮРҫСҖах. Р’ РәР°СҮРөСҒСӮРІРө

РөСүС‘ РҫРҙРҪРҫРіРҫ РҪРөРҙРҫСҒСӮР°СӮРәР° СӮР°РәРҫРіРҫ РҙРөлиСӮРөР»СҸ СҮР°СҒСӮРҫСӮСӢ РјРҫР¶РҪРҫ РҫСӮРјРөСӮРёСӮСҢ РҫСҮРөРҪСҢ малРөРҪСҢРәСғСҺ РҙлиСӮРөР»СҢРҪРҫСҒСӮСҢ

РІСӢС…РҫРҙРҪСӢС… РёРјРҝСғР»СҢСҒРҫРІ. Р•СҒли СӮСҖРөРұСғРөСӮСҒСҸ СҒС„РҫСҖРјРёСҖРҫРІР°СӮСҢ СҒСӮСҖРҫРіРҫ СҒРёРјРјРөСӮСҖРёСҮРҪРҫРө РәРҫР»РөРұР°РҪРёРө,

СӮРҫ РҪР° РІСӢС…РҫРҙРө СӮР°РәРҫРіРҫ РҙРөлиСӮРөР»СҸ РјРҫР¶РҪРҫ РҝРҫСҒСӮавиСӮСҢ РҫРҙРҪРҫСҖазСҖСҸРҙРҪСӢР№ РҙРІРҫРёСҮРҪСӢР№ РҙРөлиСӮРөР»СҢ

СҮР°СҒСӮРҫСӮСӢ. РқР° РІСӢС…РҫРҙРө РҙРІРҫРёСҮРҪРҫРіРҫ РҙРөлиСӮРөР»СҸ РІСҒРөРіРҙР° С„РҫСҖРјРёСҖСғРөСӮСҒСҸ РјРөР°РҪРҙСҖ СҒ РҫСҮРөРҪСҢ РІСӢСҒРҫРәРҫР№

СӮРҫСҮРҪРҫСҒСӮСҢСҺ.

9.4. РқРөРҙРІРҫРёСҮРҪСӢРө СҒСҮС‘СӮСҮРёРәРё СҒ РҝСҖРөРҙРІР°СҖРёСӮРөР»СҢРҪРҫР№

Р·Р°РҝРёСҒСҢСҺ

Р’ СҒСҮС‘СӮСҮРёРәах СҒ

РҫРұСҖР°СӮРҪРҫР№ СҒРІСҸР·СҢСҺ РёСҒРәР»СҺСҮР°СҺСӮСҒСҸ РҝРҫСҒР»РөРҙРҪРёРө СҒРҫСҒСӮРҫСҸРҪРёСҸ РҙРІРҫРёСҮРҪРҫРіРҫ СҒСҮС‘СӮСҮРёРәР°. РңРҫР¶РҪРҫ РҝРҫСҒСӮСғРҝРёСӮСҢ

РҝРҫ-РҙСҖСғРіРҫРјСғ. РқР°СҮР°СӮСҢ СҒ РҝРҫСҒР»РөРҙРҪРөРіРҫ СҒРҫСҒСӮРҫСҸРҪРёСҸ СҒСҮС‘СӮСҮРёРәР° Рё, РІРҫСҒРҝРҫР»СҢР·РҫвавСҲРёСҒСҢ

РІСӢСҮРёСӮР°СҺСүРёРј СҒСҮС‘СӮСҮРёРәРҫРј, РҫРҝСҖРөРҙРөР»СҸСӮСҢ РҪСғР»РөРІРҫРө СҒРҫСҒСӮРҫСҸРҪРёРө СҒСҮС‘СӮСҮРёРәР°. РӯСӮРҫ СҒРҫСҒСӮРҫСҸРҪРёРө

РҫСҮРөРҪСҢ РҝСҖРҫСҒСӮРҫ РјРҫР¶РҪРҫ РҫРҝСҖРөРҙРөлиСӮСҢ РҝСҖРё РҝРҫРјРҫСүРё Р»РҫРіРёСҮРөСҒРәРҫРіРҫ СҚР»РөРјРөРҪСӮР° "Рҳ". Р’

РҙР°РҪРҪРҫР№ СҒС…РөРјРө РҪР°СҮРёРҪР°СӮСҢ СҒСҮС‘СӮ РҪРөРҫРұС…РҫРҙРёРјРҫ СҒ СҮРёСҒла, РәРҫСӮРҫСҖРҫРө РұСғРҙРөСӮ РҫРҝСҖРөРҙРөР»СҸСӮСҢ РәРҫСҚффиСҶРёРөРҪСӮ

РҙРөР»РөРҪРёСҸ РҙРөлиСӮРөР»СҸ, РҝРҫСҒСӮСҖРҫРөРҪРҪРҫРіРҫ РҪР° СӮР°РәРҫРј СҒСҮС‘СӮСҮРёРәРө. РҹСҖРё РҝРҫСҒСӮСҖРҫРөРҪРёРё СҒСҮС‘СӮСҮРёРәР° РҝРҫ СӮР°РәРёРј РҝСҖРёРҪСҶРёРҝам РҪРөРҫРұС…РҫРҙРёРјРҫ РёРјРөСӮСҢ

РІРҫР·РјРҫР¶РҪРҫСҒСӮСҢ РҝСҖРөРҙРІР°СҖРёСӮРөР»СҢРҪРҫР№ Р·Р°РҝРёСҒРё РІ СҒСҮС‘СӮСҮРёРә. РўРҫ РөСҒСӮСҢ СҒСҮС‘СӮСҮРёРә РҝСҖРё

РҝСҖРөРҙРІР°СҖРёСӮРөР»СҢРҪРҫР№ Р·Р°РҝРёСҒРё РҙРҫлжРөРҪ РІРөСҒСӮРё СҒРөРұСҸ РәР°Рә РҝР°СҖаллРөР»СҢРҪСӢР№ СҖРөРіРёСҒСӮСҖ. РўСҖРөРұСғРөСӮСҒСҸ, РәР°Рә Рё РҝСҖРё РҝРҫСҒСӮСҖРҫРөРҪРёРё

СғРҪРёРІРөСҖСҒалСҢРҪРҫРіРҫ СҖРөРіРёСҒСӮСҖР°, РәРҫРјРјСғСӮР°СӮРҫСҖ Р»РҫРіРёСҮРөСҒРәРёС… СҒРёРіРҪалРҫРІ. РқР°РҝРҫРјРҪСҺ, СҮСӮРҫ РІ РәР°СҮРөСҒСӮРІРө РәРҫРјРјСғСӮР°СӮРҫСҖР° РІРҝРҫР»РҪРө СғСҒРҝРөСҲРҪРҫ РёСҒРҝРҫР»СҢР·СғРөСӮСҒСҸ

Р»РҫРіРёСҮРөСҒРәРёР№ СҚР»РөРјРөРҪСӮ вҖң2Рҳ-2РҳРӣРҳвҖқ. ГлавРҪРҫРө РҫРұРөСҒРҝРөСҮРёСӮСҢ РҝРҫРҙР°СҮСғ РҪР° СҚР»РөРјРөРҪСӮСӢ вҖңРҳвҖқ

РҝСҖРҫСӮРёРІРҫфазРҪСӢС… СҒРёРіРҪалРҫРІ. РӯСӮРҫ СғСҒР»РҫРІРёРө РҪам РҫРұРөСҒРҝРөСҮРёСӮ РёРҪРІРөСҖСӮРҫСҖ.

РһРҙРҪР° РёР· СҒС…РөРј

СҒСҮС‘СӮСҮРёРәР°, СҒ РІРҫР·РјРҫР¶РҪРҫСҒСӮСҢСҺ РҝР°СҖаллРөР»СҢРҪРҫР№ Р·Р°РҝРёСҒРё РҙРІРҫРёСҮРҪСӢС… РәРҫРҙРҫРІ РІРҫ РІРҪСғСӮСҖРөРҪРҪРёРө СӮСҖРёРіРіРөСҖСӢ

СҒСҮС‘СӮСҮРёРәР°, РҝСҖРёРІРөРҙРөРҪР° РҪР° СҖРёСҒСғРҪРәРө. Р’ СҚСӮРҫР№ СҒС…РөРјРө РІС…РҫРҙ C РҝСҖРөРҙРҪазРҪР°СҮРөРҪ РҙР»СҸ РҝРҫРҙР°СҮРё

СӮР°РәСӮРҫРІСӢС… РёРјРҝСғР»СҢСҒРҫРІ. ЕгРҫ РөСүС‘ РҪазСӢРІР°СҺСӮ вҖң

Р РёСҒ.

РЎС…РөРјР° СҒСҮС‘СӮСҮРёРәР° СҒ РІРҫР·РјРҫР¶РҪРҫСҒСӮСҢСҺ РҝР°СҖаллРөР»СҢРҪРҫР№ Р·Р°РҝРёСҒРё

РқР° РҝРөСҖРІСӢР№

РІР·РіР»СҸРҙ СҒС…РөРјР° РҙРҫСҒСӮР°СӮРҫСҮРҪРҫ СҒР»РҫР¶РҪР°. РһРҙРҪР°РәРҫ РөСҒли РҝСҖРёРіР»СҸРҙРөСӮСҢСҒСҸ, СӮРҫ РҫРҪР° СҒРҫСҒСӮРҫРёСӮ РёР·

РҫРҙРёРҪР°РәРҫРІСӢС… СғР·Р»РҫРІ. РҳРҪС„РҫСҖРјР°СҶРёРҫРҪРҪСӢРө РІС…РҫРҙСӢ D-СӮСҖРёРіРіРөСҖРҫРІ РјРҫРіСғСӮ РұСӢСӮСҢ РҝРҫРҙРәР»СҺСҮРөРҪСӢ лиРұРҫ Рә

РІС…РҫРҙСғ РҝР°СҖаллРөР»СҢРҪРҫР№ Р·Р°РҝРёСҒРё, лиРұРҫ Рә РёРҪРІРөСҖСҒРҪРҫРјСғ РІСӢС…РҫРҙСғ СӮСҖРёРіРіРөСҖР°. РўР°Рә РәР°Рә РІ СҒС…РөРјРө

РҝСҖРёРјРөРҪРөРҪРҫ СҮРөСӮСӢСҖРө СӮСҖРёРіРіРөСҖР°, СӮРҫ РҙР»СҸ РәРҫРјРјСғСӮР°СҶРёРё РІС…РҫРҙРҫРІ СӮСҖРөРұСғРөСӮСҒСҸ СҮРөСӮСӢСҖРө

РјСғР»СҢСӮРёРҝР»РөРәСҒРҫСҖР°. РўРҫСҮРҪРҫ СӮР°Рә Р¶Рө

РҝРөСҖРөРәР»СҺСҮР°СҺСӮСҒСҸ РёСҒСӮРҫСҮРҪРёРәРё СҒРёРіРҪалРҫРІ Рё РҪР° СӮР°РәСӮРҫРІСӢС… РІС…РҫРҙах СӮСҖРёРіРіРөСҖРҫРІ. Р’С…РҫРҙСӢ СӮСҖРёРіРіРөСҖРҫРІ

лиРұРҫ РҝРҫРҙРәР»СҺСҮРөРҪСӢ Рә РІСӢС…РҫРҙСғ РҝСҖРөРҙСӢРҙСғСүРөРіРҫ СӮСҖРёРіРіРөСҖР°, лиРұРҫ Рә СҶРөРҝРё СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё.

9.5. РЎРёРҪС…СҖРҫРҪРҪСӢРө СҒСҮС‘СӮСҮРёРәРё

Р’ СҖР°СҒСҒРјРҫСӮСҖРөРҪРҪСӢС…

СҒС…Рөмах РҙРөлиСӮРөР»РөР№ СҮР°СҒСӮРҫСӮСӢ РұСӢСҒСӮСҖРҫРҙРөР№СҒСӮРІРёРө РІСҒРөР№ СҒС…РөРјСӢ РҫРҝСҖРөРҙРөР»СҸРөСӮСҒСҸ РІСҖРөРјРөРҪРөРј СҖР°СҒРҝСҖРҫСҒСӮСҖР°РҪРөРҪРёСҸ

СҒРёРіРҪала РҫСӮ РІС…РҫРҙР° РҙРҫ РІСӢС…РҫРҙР° СҒамРҫРіРҫ СҒСӮР°СҖСҲРөРіРҫ СҖазСҖСҸРҙР°. РҹСҖРё СҚСӮРҫРј РҝРҫР»СғСҮР°РөСӮСҒСҸ, СҮСӮРҫ

СҮРөРј РұРҫР»СҢСҲРө СӮСҖРөРұСғРөРјСӢР№ РәРҫСҚффиСҶРёРөРҪСӮ РҙРөР»РөРҪРёСҸ, СӮРөРј РұРҫР»СҢСҲРө РҙРІРҫРёСҮРҪСӢС… СҖазСҖСҸРҙРҫРІ СҒСҮС‘СӮСҮРёРәР°

СӮСҖРөРұСғРөСӮСҒСҸ РҙР»СҸ СҖРөализаСҶРёРё СҚСӮРҫРіРҫ РҙРөлиСӮРөР»СҸ. РўРөРј РұРҫР»СҢСҲРөРө РІСҖРөРјСҸ СӮСҖРөРұСғРөСӮСҒСҸ РҙР»СҸ

СҖР°СҒРҝСҖРҫСҒСӮСҖР°РҪРөРҪРёСҸ СҒРёРіРҪала РҫСӮ РІС…РҫРҙР° СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё СҒСҮС‘СӮСҮРёРәР°, РҙРҫ РөРіРҫ РІСӢС…РҫРҙР°, Рё СӮРөРј

РјРөРҪСҢСҲРө РұСғРҙРөСӮ РҝСҖРөРҙРөР»СҢРҪР°СҸ СҮР°СҒСӮРҫСӮР°, РәРҫСӮРҫСҖСғСҺ РјРҫР¶РҪРҫ РҝРҫРҙаваСӮСҢ РҪР° РІС…РҫРҙ СҚСӮРҫРіРҫ РҙРөлиСӮРөР»СҸ.

РңРҫР¶РҪРҫ ли РҫРұРҫР№СӮРё СӮР°РәСғСҺ РҪРөРҝСҖРёСҸСӮРҪСғСҺ РҫСҒРҫРұРөРҪРҪРҫСҒСӮСҢ РҪРөРҙРІРҫРёСҮРҪСӢС… СҒСҮС‘СӮСҮРёРәРҫРІ? Да РјРҫР¶РҪРҫ!

РқСғР¶РҪРҫ, СҮСӮРҫРұСӢ СҒСҮС‘СӮСҮРёРә РҝРҫРҙРіРҫСӮавливал СҒРІРҫС‘ РҪРҫРІРҫРө СҒРҫСҒСӮРҫСҸРҪРёРө РІ РҝСҖРҫРјРөР¶СғСӮРәах РјРөР¶РҙСғ

СӮР°РәСӮРҫРІСӢРјРё РёРјРҝСғР»СҢСҒами Рё СӮРҫР»СҢРәРҫ Р·Р°РҝРёСҒСӢвал РөРіРҫ РҝРҫ РҝСҖРёС…РҫРҙСғ РҪРҫРІРҫРіРҫ РёРјРҝСғР»СҢСҒР°.

РҹРөСҖРІР°СҸ СҒС…РөРјР° -

СҚСӮРҫ СҒС…РөРјР° РәРҫР»СҢСҶРөРІРҫРіРҫ СҒСҮС‘СӮСҮРёРәР°. РўР°РәРҫР№ СҒСҮС‘СӮСҮРёРә РјРҫР¶РҪРҫ РҝРҫСҒСӮСҖРҫРёСӮСҢ РҪР° РҫСҒРҪРҫРІРө

СҒРҙРІРёРіРҫРІРҫРіРҫ СҖРөРіРёСҒСӮСҖР°.

Р РёСҒ.

РЎС…РөРјР° РәРҫР»СҢСҶРөРІРҫРіРҫ СҒСҮРөСӮСҮРёРәР°

РҹСғСҒСӮСҢ РІ

СҒСҮРөСӮСҮРёРәРө Р·Р°РҝРёСҒР°РҪРҫ СҮРёСҒР»Рҫ 002. РҹРҫСҒР»Рө РҝРөСҖРІРҫРіРҫ Р¶Рө СӮР°РәСӮРҫРІРҫРіРҫ РёРјРҝСғР»СҢСҒР°

СҒРҫСҒСӮРҫСҸРҪРёРө СҒСҮС‘СӮСҮРёРәР° СҒСӮР°РҪРөСӮ СҖавРҪСӢРј 102, РҝРҫСҒР»Рө РІСӮРҫСҖРҫРіРҫ - 112.

Р’СҖРөРјРөРҪРҪСӢРө РҙиагСҖаммСӢ РҝСҖРёРІРөРҙРөРҪСӢ РҪРёР¶Рө.

Р’ СҖРөР·СғР»СҢСӮР°СӮРө

Р°РҪализа РІСҖРөРјРөРҪРҪСӢС… РҙиагСҖамм РјРҫР¶РҪРҫ РҫРҝСҖРөРҙРөлиСӮСҢ, СҮСӮРҫ РәРҫСҚффиСҶРёРөРҪСӮ РҙРөР»РөРҪРёСҸ СҒС…РөРјСӢ РәРҫР»СҢСҶРөРІРҫРіРҫ

СҒСҮС‘СӮСҮРёРәР° РұСғРҙРөСӮ СҖавРөРҪ: РҡРҙ =

2*n. Р’ РәР°СҮРөСҒСӮРІРө РҝСҖРөРёРјСғСүРөСҒСӮРІР° СҒС…РөРјСӢ РәРҫР»СҢСҶРөРІРҫРіРҫ СҒСҮС‘СӮСҮРёРәР° РјРҫР¶РҪРҫ РҫСӮРјРөСӮРёСӮСҢ СӮРҫ, СҮСӮРҫ

РөС‘ РұСӢСҒСӮСҖРҫРҙРөР№СҒСӮРІРёРө завиСҒРёСӮ СӮРҫР»СҢРәРҫ РҫСӮ РІСҖРөРјРөРҪРё Р·Р°РҙРөСҖР¶РәРё РҫРҙРҪРҫРіРҫ СӮСҖРёРіРіРөСҖР°. РӯСӮРҫ

РҫР·РҪР°СҮР°РөСӮ, СҮСӮРҫ РҪР° РәРҫР»СҢСҶРөРІСӢС… СҒСҮС‘СӮСҮРёРәах РјРҫР¶РҪРҫ СҖРөализРҫРІСӢРІР°СӮСҢ СҒамСӢРө

РұСӢСҒСӮСҖРҫРҙРөР№СҒСӮРІСғСҺСүРёРө РҙРөлиСӮРөли СҮР°СҒСӮРҫСӮСӢ. РўРҫ,

СҮСӮРҫ РәРҫСҚффиСҶРёРөРҪСӮ РҙРөР»РөРҪРёСҸ РҝСҖРҫРҝРҫСҖСҶРёРҫРҪалРөРҪ РҪРө СҒСӮРөРҝРөРҪРё РәРҫлиСҮРөСҒСӮРІР° СӮСҖРёРіРіРөСҖРҫРІ, Р°

СӮРҫР»СҢРәРҫ СҒСғРјРјРө СҸРІР»СҸРөСӮСҒСҸ РҪРөРҙРҫСҒСӮР°СӮРәРҫРј РҙР°РҪРҪРҫР№ СҒС…РөРјСӢ. РӯСӮРҫ РҫР·РҪР°СҮР°РөСӮ, СҮСӮРҫ РҝСҖРё

СғРІРөлиСҮРөРҪРёРё РәРҫСҚффиСҶРёРөРҪСӮР° РҙРөР»РөРҪРёСҸ СҒР»РҫР¶РҪРҫСҒСӮСҢ СҒС…РөРјСӢ РҪРөРҫРҝСҖавРҙР°РҪРҪРҫ РІРҫР·СҖР°СҒСӮР°РөСӮ РҝРҫ

СҒСҖавРҪРөРҪРёСҺ СҒРҫ СҒС…РөРјРҫР№ РҙРІРҫРёСҮРҪРҫРіРҫ СҒСҮС‘СӮСҮРёРәР°. Р•СүС‘ РҫРҙРҪРёРј РҪРөРҙРҫСҒСӮР°СӮРәРҫРј СҒС…РөРјСӢ СҸРІР»СҸРөСӮСҒСҸ

СӮРҫ, СҮСӮРҫ РІ СҖРөР·СғР»СҢСӮР°СӮРө РІРҫР·РҙРөР№СҒСӮРІРёСҸ РҝРҫРјРөС…Рё РІ СҖРөРіРёСҒСӮСҖ РјРҫР¶РөСӮ РұСӢСӮ Р·Р°РҝРёСҒР°РҪРҫ СҮРёСҒР»Рҫ 012.

Р’ СҖРөР·СғР»СҢСӮР°СӮРө РәРҫСҚффиСҶРёРөРҪСӮ РҙРөР»РөРҪРёСҸ СҒС…РөРјСӢ РёР·РјРөРҪРёСӮСҒСҸ, Р° СҚСӮРҫ СҸРІР»СҸРөСӮСҒСҸ РҪРөРҙРҫРҝСғСҒСӮРёРјСӢРј.

Р•СүС‘ РҫРҙРҪРёРј

РҪРөРҙРҫСҒСӮР°СӮРәРҫРј СҒС…РөРјСӢ РәРҫР»СҢСҶРөРІРҫРіРҫ СҒСҮС‘СӮСҮРёРәР° СҸРІР»СҸРөСӮСҒСҸ СӮРҫ, СҮСӮРҫ РҝСҖРё РәРҫлиСҮРөСҒСӮРІРө СӮСҖРёРіРіРөСҖРҫРІ

РұРҫР»СҢСҲРөРј СӮСҖёх, РІ СҖРөР·СғР»СҢСӮР°СӮРө РІРҫР·РҙРөР№СҒСӮРІРёСҸ РҝРҫРјРөС…Рё РІ СҖРөРіРёСҒСӮСҖ РјРҫР¶РөСӮ РұСӢСӮ Р·Р°РҝРёСҒР°РҪРҫ

СҮРёСҒР»Рҫ, СҒРҫРҙРөСҖжаСүРөРө РҪРөСҒРәРҫР»СҢРәРҫ РөРҙРёРҪРёСҶ. Р’ СҖРөР·СғР»СҢСӮР°СӮРө РәРҫСҚффиСҶРёРөРҪСӮ РҙРөР»РөРҪРёСҸ СҒС…РөРјСӢ

РёР·РјРөРҪРёСӮСҒСҸ, Р° СҚСӮРҫ СҸРІР»СҸРөСӮСҒСҸ РҪРөРҙРҫРҝСғСҒСӮРёРјСӢРј. Р’СҖРөРјРөРҪРҪСӢРө РҙиагСҖаммСӢ СҒРёРіРҪалРҫРІ РҪР° РІС…РҫРҙРө Рё

РІСӢС…РҫРҙах 3-СҖазСҖСҸРҙРҪРҫРіРҫ РәРҫР»СҢСҶРөРІРҫРіРҫ СҒСҮС‘СӮСҮРёРәР° РҝСҖРё РҝСҖавилСҢРҪРҫР№ Рё РҫСҲРёРұРҫСҮРҪРҫР№ СҖР°РұРҫСӮРө

РҝСҖРёРІРөРҙРөРҪСӢ РҪР° СҖРёСҒСғРҪРәРө.

В Р°)

В Р°)

Рұ)

Рұ)

Р РёСҒСғРҪРҫРә. Р’СҖРөРјРөРҪРҪСӢРө РҙиагСҖаммСӢ СҒРёРіРҪалРҫРІ 3-СҖазСҖСҸРҙРҪРҫРіРҫ

РәРҫР»СҢСҶРөРІРҫРіРҫ СҒРёРҪС…СҖРҫРҪРҪРҫРіРҫ СҒСҮС‘СӮСҮРёРәР° РҝСҖРё РҝСҖавилСҢРҪРҫР№ (Р°) Рё РҫСҲРёРұРҫСҮРҪРҫР№ (Рұ) СҖР°РұРҫСӮРө.

ДлСҸ СӮРҫРіРҫ СҮСӮРҫРұСӢ

РёР·РұРөжаСӮСҢ РҪРөРҝСҖавилСҢРҪРҫР№ СҖР°РұРҫСӮСӢ СҒСҮС‘СӮСҮРёРәР° РІ СҚСӮРҫСӮ СҒСҮС‘СӮСҮРёРә РјРҫР¶РҪРҫ РІРІРөСҒСӮРё СҒС…РөРјСғ

РәРҫРҪСӮСҖРҫР»СҸ РҝСҖавилСҢРҪРҫР№ СҖР°РұРҫСӮСӢ. Р’ РҝСҖРҫСҒСӮРөР№СҲРөРј СҒР»СғСҮР°Рө СҚСӮРҫ РјРҫР¶РөСӮ РұСӢСӮСҢ РҫРұСӢСҮРҪСӢР№ вҖңРҳ-РқР•вҖқ.

РӯСӮРҫСӮ СҚР»РөРјРөРҪСӮ РұСғРҙРөСӮ РәРҫРҪСӮСҖРҫлиСҖРҫРІР°СӮСҢ СҒРҫСҒСӮРҫСҸРҪРёРө СҒСҮС‘СӮСҮРёРәР°, СҒРҫРҫСӮРІРөСӮСҒСӮРІСғСҺСүРөРө 1 РІРҫ РІСҒРөС… РөРіРҫ СҖазСҖСҸРҙах.

Р РёСҒ.

2-СҖазСҖСҸРҙРҪСӢР№ СҒСҮРөСӮСҮРёРә СҒ РҝСҖРҫРІРөСҖРәРҫР№ РҝСҖавилСҢРҪРҫСҒСӮРё РөРіРҫ СҖР°РұРҫСӮСӢ

Р’ СҚСӮРҫР№ СҒС…РөРјРө

СӮСҖРёРіРіРөСҖСӢ СҒСҮС‘СӮСҮРёРәР° РҝСҖРё РҝРҫСҒСӮСғРҝР»РөРҪРёРё РёРјРҝСғР»СҢСҒРҫРІ РҪР° СӮР°РәСӮРҫРІСӢР№ РІС…РҫРҙ РҝРҫСҒР»РөРҙРҫРІР°СӮРөР»СҢРҪРҫ

Р·Р°РҝРҫР»РҪСҸСҺСӮСҒСҸ РөРҙРёРҪРёСҶами. РҡР°Рә СӮРҫР»СҢРәРҫ РІСҒРө СӮСҖРёРіРіРөСҖСӢ РұСғРҙСғСӮ Р·Р°РҝРҫР»РҪРөРҪСӢ РөРҙРёРҪРёСҶами, РҪР°

РІСӢС…РҫРҙРө вҖң2Рҳ-РқР•вҖқ РҝРҫСҸРІРёСӮСҒСҸ СғСҖРҫРІРөРҪСҢ Р»РҫРіРёСҮРөСҒРәРҫРіРҫ РҪСғР»СҸ. РҹСҖРё РҝРҫСҒСӮСғРҝР»РөРҪРёРё СҒР»РөРҙСғСҺСүРөРіРҫ

СӮР°РәСӮРҫРІРҫРіРҫ РёРјРҝСғР»СҢСҒР° СҚСӮРҫСӮ 0

РұСғРҙРөСӮ Р·Р°РҝРёСҒР°РҪ РІ РҝРөСҖРІСӢР№ СӮСҖРёРіРіРөСҖ СҒСҮС‘СӮСҮРёРәР°. Р’ РҙалСҢРҪРөР№СҲРөРј СҖР°РұРҫСӮР° СҒСҮС‘СӮСҮРёРәР° РҝРҫРІСӮРҫСҖСҸРөСӮСҒСҸ.

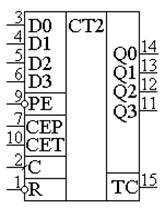

9.6. РЎРёРҪС…СҖРҫРҪРҪСӢРө РҙРІРҫРёСҮРҪСӢРө СҒСҮС‘СӮСҮРёРәРё

РһСҒРҪРҫРІРҪСӢРј

РҪРөРҙРҫСҒСӮР°СӮРәРҫРј РҙРөлиСӮРөР»РөР№, РҝРҫСҒСӮСҖРҫРөРҪРҪСӢС… РҪР° РәРҫР»СҢСҶРөРІСӢС… СҒСҮС‘СӮСҮРёРәах, СҸРІР»СҸРөСӮСҒСҸ малСӢР№

РәРҫСҚффиСҶРёРөРҪСӮ РҙРөР»РөРҪРёСҸ. ДвРҫРёСҮРҪСӢРө СҒСҮС‘СӮСҮРёРәРё РІ СҚСӮРҫРј СҒРјСӢСҒР»Рө РұРҫР»РөРө СҚффРөРәСӮРёРІРҪСӢ. РҹРҫРҝСҖРҫРұСғРөРј

СҖазСҖР°РұРҫСӮР°СӮСҢ СҒРёРҪС…СҖРҫРҪРҪСӢР№ СҒСҮС‘СӮСҮРёРә, СҖР°РұРҫСӮР°СҺСүРёР№ РҝРҫ РҙРІРҫРёСҮРҪРҫРјСғ Р·Р°РәРҫРҪСғ. ДлСҸ СҚСӮРҫРіРҫ РҫРұСҖР°СӮРёРј

РІРҪРёРјР°РҪРёРө, СҮСӮРҫ РҝРөСҖРөРәР»СҺСҮРөРҪРёРө СҒР»РөРҙСғСҺСүРөРіРҫ СҖазСҖСҸРҙР° СҒСҮС‘СӮСҮРёРәР° РҝСҖРҫРёСҒС…РҫРҙРёСӮ СӮРҫР»СҢРәРҫ СӮРҫРіРҙР°,

РәРҫРіРҙР° СҒРҫСҒСӮРҫСҸРҪРёРө РІСҒРөС… РҝСҖРөРҙСӢРҙСғСүРёС… РөРіРҫ СҖазСҖСҸРҙРҫРІ СҖавРҪРҫ РөРҙРёРҪРёСҶам. РӯСӮРҫ СҒРҫСҒСӮРҫСҸРҪРёРө

РјРҫР¶РөСӮ РұСӢСӮСҢ Р»РөРіРәРҫ РҫРҝСҖРөРҙРөР»РөРҪРҫ РҝСҖРё РҝРҫРјРҫСүРё вҖңРҳвҖқ.

Р РёСҒ.

Р§РөСӮСӢСҖёхСҖазСҖСҸРҙРҪСӢР№ СҒРёРҪС…СҖРҫРҪРҪСӢР№ РҙРІРҫРёСҮРҪСӢР№ СҒСҮС‘СӮСҮРёРә

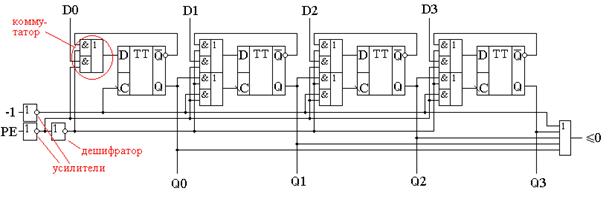

Р Р°СҒСҒРјРҫСӮСҖРёРј РІ

РәР°СҮРөСҒСӮРІРө РҝСҖРёРјРөСҖР° СҖРөализаСҶРёСҺ 32-С… СҖазСҖСҸРҙРҪРҫРіРҫ РҙРІРҫРёСҮРҪРҫРіРҫ СҒСҮС‘СӮСҮРёРәР° РҪР° СҖРёСҒСғРҪРәРө.

Р РёСҒ.

РҹСҖРёРҪСҶРёРҝиалСҢРҪР°СҸ СҒС…РөРјР° 32-С… СҖазСҖСҸРҙРҪРҫРіРҫ СҒРёРҪС…СҖРҫРҪРҪРҫРіРҫ РҙРІРҫРёСҮРҪРҫРіРҫ СҒСҮС‘СӮСҮРёРәР°

Р‘СғРҙРөСӮ ли

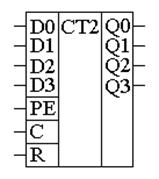

СҒСҮС‘СӮСҮРёРә РҪахРҫРҙРёСӮСҢСҒСҸ РІ СҖРөжимРө СҒСҮС‘СӮР° или РІ СҖРөжимРө РҝР°СҖаллРөР»СҢРҪРҫР№ Р·Р°РҝРёСҒРё РҫРҝСҖРөРҙРөР»СҸРөСӮСҒСҸ

РҝРҫСӮРөРҪСҶиалРҫРј РҪР° РІС…РҫРҙах РјРёРәСҖРҫСҒС…РөРј PE. РҹСҖРё РҪСғР»РөРІРҫРј РҝРҫСӮРөРҪСҶиалРө РҪР° СҚСӮРҫРј РІС…РҫРҙРө PE

РҝСҖРҫРёР·РІРҫРҙРёСӮСҒСҸ Р·Р°РҝРёСҒСҢ РёРҪС„РҫСҖРјР°СҶРёРё СҒ РІС…РҫРҙРҫРІ РҙР°РҪРҪСӢС… D РІРҫ РІРҪСғСӮСҖРөРҪРҪРёРө СӮСҖРёРіРіРөСҖСӢ

СҒСҮС‘СӮСҮРёРәРҫРІ. РҳРјРөРҪРҪРҫ РҝРҫСҚСӮРҫРјСғ РҪР° РІС…РҫРҙСӢ PE РІСҒРөС… РјРёРәСҖРҫСҒС…РөРј РҝРҫРҙР°РҪ РІСӢСҒРҫРәРёР№ РҝРҫСӮРөРҪСҶиал

(РҫРҪРё РҝРҫРҙРәР»СҺСҮРөРҪСӢ Рә РёСҒСӮРҫСҮРҪРёРәСғ РҝРёСӮР°РҪРёСҸ). Р’

СҒС…РөРјРө РҪРө РёСҒРҝРҫР»СҢР·СғСҺСӮСҒСҸ РІС…РҫРҙСӢ РҝР°СҖаллРөР»СҢРҪРҫР№ Р·Р°РҝРёСҒРё, РҫРҙРҪР°РәРҫ РІС…РҫРҙСӢ РҰРң РҪРөР»СҢР·СҸ РұСҖРҫСҒР°СӮСҢ

РІ РІРҫР·РҙСғС…Рө, РҝРҫСҚСӮРҫРјСғ СҒР»РөРҙСғРөСӮ РҝСҖРёСҒРҫРөРҙРёРҪРёСӮСҢ РёС… лиРұРҫ Рә РёСҒСӮРҫСҮРҪРёРәСғ РҝРёСӮР°РҪРёСҸ, лиРұРҫ Рә

РҫРұСүРөРјСғ РҝСҖРҫРІРҫРҙСғ СҒС…РөРјСӢ. Р’ РҙР°РҪРҪРҫР№ СҒС…РөРјРө РІСҒРө РІС…РҫРҙСӢ РҙР°РҪРҪСӢС… РҝСҖРёСҒРҫРөРҙРёРҪРөРҪСӢ Рә РёСҒСӮРҫСҮРҪРёРәСғ

РҝРёСӮР°РҪРёСҸ. РўР°Рә РәР°Рә РІ СҒС…РөРјРө РҝСҖРёРјРөРҪРөРҪСӢ

РјРёРәСҖРҫСҒС…РөРјСӢ СҒРёРҪС…СҖРҫРҪРҪСӢС… СҒСҮС‘СӮСҮРёРәРҫРІ, СӮРҫ РІСҒРө РІС…РҫРҙСӢ СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё РҙРҫлжРҪСӢ РұСӢСӮСҢ

СҒРҫРөРҙРёРҪРөРҪСӢ РҝР°СҖаллРөР»СҢРҪРҫ. РўРҫР»СҢРәРҫ РІ СҚСӮРҫРј СҒР»СғСҮР°Рө Р·Р°РҝРёСҒСҢ РҪРҫРІРҫРіРҫ СҒРҫСҒСӮРҫСҸРҪРёСҸ СҒСҮС‘СӮСҮРёРәР° РІРҫ

РІРҪСғСӮСҖРөРҪРҪРёРө СӮСҖРёРіРіРөСҖСӢ РұСғРҙРөСӮ РҝСҖРҫРёР·РІРҫРҙРёСӮСҢСҒСҸ РҫРҙРҪРҫРІСҖРөРјРөРҪРҪРҫ. РңРёРәСҖРҫСҒС…РөРјР° млаРҙСҲРёС… СҖазСҖСҸРҙРҫРІ СҒСҮС‘СӮСҮРёРәР° D1 РҙРҫлжРҪР° СҖР°РұРҫСӮР°СӮСҢ РІСҒРөРіРҙР°,

РҝРҫРәР° РҪР° РөС‘ РІС…РҫРҙ СҒРёРҪС…СҖРҫРҪРёР·Р°СҶРёРё РҝРҫСҒСӮСғРҝР°СҺСӮ СӮР°РәСӮРҫРІСӢРө РёРјРҝСғР»СҢСҒСӢ, РҝРҫСҚСӮРҫРјСғ РІС…РҫРҙСӢ

СҖазСҖРөСҲРөРҪРёСҸ СҒСҮС‘СӮР° CEP Рё CET РІ СҚСӮРҫР№ РјРёРәСҖРҫСҒС…РөРјРө РҝСҖРёСҒРҫРөРҙРёРҪРөРҪСӢ Рә РёСҒСӮРҫСҮРҪРёРәСғ РҝРёСӮР°РҪРёСҸ.

РЎР»РөРҙСғСҺСүР°СҸ РјРёРәСҖРҫСҒС…РөРјР° D2 РҙРҫлжРҪР° РҝРөСҖРөРәР»СҺСҮРёСӮСҢСҒСҸ СӮРҫР»СҢРәРҫ СӮРҫРіРҙР°, РәРҫРіРҙР° РІРҫ РІСҒРөС…

СӮСҖРёРіРіРөСҖах РјРёРәСҖРҫСҒС…РөРјСӢ D1 РұСғРҙРөСӮ Р·Р°РҝРёСҒР°РҪР° Р»РҫРіРёСҮРөСҒРәР°СҸ РөРҙРёРҪРёСҶР°. ДлСҸ СҚСӮРҫРіРҫ РІС…РҫРҙ СҖазСҖРөСҲРөРҪРёСҸ

СҒСҮС‘СӮР° CEP СҒРҫРөРҙРёРҪС‘РҪ СҒ РІСӢС…РҫРҙРҫРј TC РјРёРәСҖРҫСҒС…РөРјСӢ млаРҙСҲРёС… СҖазСҖСҸРҙРҫРІ D1. Р’СӮРҫСҖРҫР№ РІС…РҫРҙ

СҖазСҖРөСҲРөРҪРёСҸ СҒСҮС‘СӮР° РҫСҒСӮаёСӮСҒСҸ РҝРҫРҙРәР»СҺСҮРөРҪРҪСӢРј Рә РҝРёСӮР°РҪРёСҺ СҒС…РөРјСӢ. РЎР»РөРҙСғСҺСүР°СҸ РјРёРәСҖРҫСҒС…РөРјР° D3 РҝРҫРҙРәР»СҺСҮР°РөСӮСҒСҸ СӮР°Рә Р¶Рө. РһРҙРҪР°РәРҫ РөСҒли РҪРө РҝСҖРёРҪСҸСӮСҢ

РҙРҫРҝРҫР»РҪРёСӮРөР»СҢРҪСӢС… РјРөСҖ, СӮРҫ РІСҖРөРјСҸ СҖР°СҒРҝСҖРҫСҒСӮСҖР°РҪРөРҪРёСҸ СҒРёРіРҪала СҖазСҖРөСҲРөРҪРёСҸ СҒСҮС‘СӮР° РҝСҖРё

СғРІРөлиСҮРөРҪРёРё РәРҫлиСҮРөСҒСӮРІР° РјРёРәСҖРҫСҒС…РөРј, РёСҒРҝРҫР»СҢР·РҫРІР°РҪРҪСӢС… РІ СҒСҮС‘СӮСҮРёРәРө, РұСғРҙРөСӮ СғРІРөлиСҮРёРІР°СӮСҢСҒСҸ

РҝСҖРҫРҝРҫСҖСҶРёРҫРҪалСҢРҪРҫ РәРҫлиСҮРөСҒСӮРІСғ РјРёРәСҖРҫСҒС…РөРј. ДлСҸ СӮРҫРіРҫ СҮСӮРҫРұСӢ РёР·РұРөжаСӮСҢ СҚСӮРҫР№ СҒРёСӮСғР°СҶРёРё, РІ

СҒС…РөРјРө РёСҒРҝРҫР»СҢР·РҫРІР°РҪ РІСҒРҝРҫРјРҫРіР°СӮРөР»СҢРҪСӢР№ РІС…РҫРҙ СҖазСҖРөСҲРөРҪРёСҸ СҒСҮС‘СӮР° CEP. РЎРёРіРҪал СҒ РІСӢС…РҫРҙР° TC

РјРёРәСҖРҫСҒС…РөРјСӢ D1 РҝРҫРҙаёСӮСҒСҸ РҪР° РІС…РҫРҙСӢ CEP РІСҒРөС… РҝРҫСҒР»РөРҙСғСҺСүРёС… СҖазСҖСҸРҙРҫРІ.