–ė–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā

–ł –Ķ–≥–ĺ —Ą—É–Ĺ–ļ—Ü–ł–ł (–õ–Ķ–ļ—Ü–ł–ł)

–ü–õ–ź–Ě –õ–ē–ö–¶–ė–ė

1. –ě–Ī—Č–ł–Ķ —Ā–≤–Ķ–ī–Ķ–Ĺ–ł—Ź –ĺ–Ī

–ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į—Ö

2. –ė–Ķ—Ä–į—Ä—Ö–ł—Ź —ą–ł–Ĺ

3. –®–ł–Ĺ–Ĺ—č–Ķ

—Ą–ĺ—Ä–ľ–ł—Ä–ĺ–≤–į—ā–Ķ–Ľ–ł –ł –Ī—É—Ą–Ķ—Ä–Ĺ—č–Ķ —Ä–Ķ–≥–ł—Ā—ā—Ä—č

4. –ü–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ—č–Ķ

–Ņ–Ķ—Ä–ł—Ą–Ķ—Ä–ł–Ļ–Ĺ—č–Ķ –į–ī–į–Ņ—ā–Ķ—Ä—č

5. –ü—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä—É–Ķ–ľ—č–Ķ

—Ā–≤—Ź–∑–Ĺ—č–Ķ –į–ī–į–Ņ—ā–Ķ—Ä—č

6. –ü—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä—É–Ķ–ľ—č–Ķ

–ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä—č –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ

7. –ö–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä—č –Ņ—Ä—Ź–ľ–ĺ–≥–ĺ –ī–ĺ—Ā—ā—É–Ņ–į –ļ –Ņ–į–ľ—Ź—ā–ł

8. –ü—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä—É–Ķ–ľ—č–Ķ –ł–Ĺ—ā–Ķ—Ä–≤–į–Ľ—Ć–Ĺ—č–Ķ —ā–į–Ļ–ľ–Ķ—Ä—č

1. –ě–Ī—Č–ł–Ķ —Ā–≤–Ķ–ī–Ķ–Ĺ–ł—Ź –ĺ–Ī –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į—Ö

–Ē–Ľ—Ź

–ĺ–Ņ–ł—Ā–į–Ĺ–ł—Ź —Ā–ĺ–≤–ĺ–ļ—É–Ņ–Ĺ–ĺ—Ā—ā–ł —Ā—Ö–Ķ–ľ–ĺ—ā–Ķ—Ö–Ĺ–ł—á–Ķ—Ā–ļ–ł—Ö —Ā—Ä–Ķ–ī—Ā—ā–≤ –ł —Ą—É–Ĺ–ļ—Ü–ł–Ļ, –ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–ł–≤–į—é—Č–ł—Ö

–Ĺ–Ķ–Ņ–ĺ—Ā—Ä–Ķ–ī—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ–Ķ –≤–∑–į–ł–ľ–ĺ–ī–Ķ–Ļ—Ā—ā–≤–ł–Ķ —Ā–ĺ—Ā—ā–į–≤–Ĺ—č—Ö —ć–Ľ–Ķ–ľ–Ķ–Ĺ—ā–ĺ–≤ —Ā—Ä–Ķ–ī—Ā—ā–≤ –≤—č—á–ł—Ā–Ľ–ł—ā–Ķ–Ľ—Ć–Ĺ–ĺ–Ļ

—ā–Ķ—Ö–Ĺ–ł–ļ–ł (–°–í–Ę), –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É—é—ā—Ā—Ź –Ņ–ĺ–Ĺ—Ź—ā–ł—Ź "–ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā", "—Ā—ā—č–ļ",

"–Ņ—Ä–ĺ—ā–ĺ–ļ–ĺ–Ľ".

–°—ā–į–Ĺ–ī–į—Ä—ā–Ĺ—č–Ļ –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā - —Ā–ĺ–≤–ĺ–ļ—É–Ņ–Ĺ–ĺ—Ā—ā—Ć —É–Ĺ–ł—Ą–ł—Ü–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č—Ö —ā–Ķ—Ö–Ĺ–ł—á–Ķ—Ā–ļ–ł—Ö, –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–Ĺ—č—Ö –ł

–ļ–ĺ–Ĺ—Ā—ā—Ä—É–ļ—ā–ł–≤–Ĺ—č—Ö —Ā—Ä–Ķ–ī—Ā—ā–≤, –Ĺ–Ķ–ĺ–Ī—Ö–ĺ–ī–ł–ľ—č—Ö –ī–Ľ—Ź —Ä–Ķ–į–Ľ–ł–∑–į—Ü–ł–ł –≤–∑–į–ł–ľ–ĺ–ī–Ķ–Ļ—Ā—ā–≤–ł—Ź —Ä–į–∑–Ľ–ł—á–Ĺ—č—Ö —Ą—É–Ĺ–ļ—Ü–ł–ĺ–Ĺ–į–Ľ—Ć–Ĺ—č—Ö —ć–Ľ–Ķ–ľ–Ķ–Ĺ—ā–ĺ–≤ –≤ –į–≤—ā–ĺ–ľ–į—ā–ł—á–Ķ—Ā–ļ–ł—Ö —Ā–ł—Ā—ā–Ķ–ľ–į—Ö

–ĺ–Ī—Ä–į–Ī–ĺ—ā–ļ–ł –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł (–°–ě–ė) –Ņ—Ä–ł —É—Ā–Ľ–ĺ–≤–ł—Ź—Ö, –Ņ—Ä–Ķ–ī–Ņ–ł—Ā–į–Ĺ–Ĺ—č—Ö —Ā—ā–į–Ĺ–ī–į—Ä—ā–ĺ–ľ –ł –Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–Ĺ—č—Ö

–Ĺ–į –ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–Ķ–Ĺ–ł–Ķ –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ĺ–Ĺ–Ĺ–ĺ–Ļ, —ć–Ľ–Ķ–ļ—ā—Ä–ł—á–Ķ—Ā–ļ–ĺ–Ļ –ł –ļ–ĺ–Ĺ—Ā—ā—Ä—É–ļ—ā–ł–≤–Ĺ–ĺ–Ļ —Ā–ĺ–≤–ľ–Ķ—Ā—ā–ł–ľ–ĺ—Ā—ā–ł

—É–ļ–į–∑–į–Ĺ–Ĺ—č—Ö —ć–Ľ–Ķ–ľ–Ķ–Ĺ—ā–ĺ–≤.

–ė–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā—č

–ļ–Ľ–į—Ā—Ā–ł—Ą–ł—Ü–ł—Ä—É—é—ā—Ā—Ź:

-

–Ņ–ĺ –Ņ—Ä–ł–∑–Ĺ–į–ļ–į–ľ –ļ–ĺ–Ĺ—Ą–ł–≥—É—Ä–į—Ü–ł–ł

—Ü–Ķ–Ņ–Ķ–Ļ —Ā–≤—Ź–∑–ł –ľ–Ķ–∂–ī—É –ĺ–Ī—ä–Ķ–ļ—ā–į–ľ–ł (–ľ–į–≥–ł—Ā—ā—Ä–į–Ľ—Ć–Ĺ—č–Ķ, —Ä–į–ī–ł–į–Ľ—Ć–Ĺ—č–Ķ –ł –ī—Ä.);

-

—Ā–Ņ–ĺ—Ā–ĺ–Ī—É –Ņ–Ķ—Ä–Ķ–ī–į—á–ł

–ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł (–Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ—č–Ķ, –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č–Ķ, –ł –ī—Ä.);

-

—Ä–Ķ–∂–ł–ľ—É –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –ī–į–Ĺ–Ĺ—č—Ö

(–ī—É–Ņ–Ľ–Ķ–ļ—Ā–Ĺ—č–Ļ, –Ņ–ĺ–Ľ—É–ī—É–Ņ–Ľ–Ķ–ļ—Ā–Ĺ—č–Ļ, —Ā–ł–ľ–Ņ–Ľ–Ķ–ļ—Ā–Ĺ—č–Ļ);

-

—Ā–Ņ–ĺ—Ā–ĺ–Ī—É –ĺ–Ī–ľ–Ķ–Ĺ–į (—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ—č–Ļ, –į—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ—č–Ļ).

–°—ā—č–ļ -

–ľ–Ķ—Ā—ā–ĺ —Ā–ĺ–Ķ–ī–ł–Ĺ–Ķ–Ĺ–ł—Ź —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤ –Ņ–Ķ—Ä–Ķ–ī–į—á–ł —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ –ī–į–Ĺ–Ĺ—č—Ö, –≤—Ö–ĺ–ī—Ź—Č–ł—Ö –≤ —Ā–Ķ—ā–ł –Ņ–Ķ—Ä–Ķ–ī–į—á–ł

–ī–į–Ĺ–Ĺ—č—Ö (–°–ü–Ē). –≠—ā–ĺ –Ņ–ĺ–Ĺ—Ź—ā–ł–Ķ –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ—ā—Ā—Ź –ī–Ľ—Ź –ĺ–Ņ–ł—Ā–į–Ĺ–ł—Ź —Ą—É–Ĺ–ļ—Ü–ł–Ļ –ł —Ā—Ä–Ķ–ī—Ā—ā–≤

—Ā–ĺ–Ņ—Ä—Ź–∂–Ķ–Ĺ–ł—Ź —ć–Ľ–Ķ–ľ–Ķ–Ĺ—ā–ĺ–≤ –°–ü–Ē.

–ü—Ä–ĺ—ā–ĺ–ļ–ĺ–Ľ—č

- —Ā—ā—Ä–ĺ–≥–ĺ –∑–į–ī–į–Ĺ–Ĺ–į—Ź –Ņ—Ä–ĺ—Ü–Ķ–ī—É—Ä–į –ł–Ľ–ł —Ā–ĺ–≤–ĺ–ļ—É–Ņ–Ĺ–ĺ—Ā—ā—Ć –Ņ—Ä–į–≤–ł–Ľ, –ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ—Ź—é—Č–į—Ź —Ā–Ņ–ĺ—Ā–ĺ–Ī –≤—č–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł—Ź

–ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ–Ķ–Ĺ–Ĺ–ĺ–≥–ĺ –ļ–Ľ–į—Ā—Ā–į —Ą—É–Ĺ–ļ—Ü–ł–Ļ —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–ł–ľ–ł (–°–í–Ę). –ü—Ä–į–ļ—ā–ł—á–Ķ—Ā–ļ–ł –Ľ—é–Ī–ĺ–Ļ

–ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā —Ā–ĺ–ī–Ķ—Ä–∂–ł—ā –Ī–ĺ–Ľ—Ć—ą–Ķ –ł–Ľ–ł –ľ–Ķ–Ĺ—Ć—ą–Ķ —ć–Ľ–Ķ–ľ–Ķ–Ĺ—ā–ĺ–≤ –Ņ—Ä–ĺ—ā–ĺ–ļ–ĺ–Ľ–į, –ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ—Ź–Ķ–ľ—č—Ö

–Ņ—Ä–ĺ—Ü–Ķ–ī—É—Ä–Ĺ—č–ľ–ł –ł —Ą—É–Ĺ–ļ—Ü–ł–ĺ–Ĺ–į–Ľ—Ć–Ĺ—č–ľ–ł –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į–ľ–ł.

–ě—Ā–Ĺ–ĺ–≤–Ĺ–ĺ–Ķ

–Ĺ–į–∑–Ĺ–į—á–Ķ–Ĺ–ł–Ķ –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–ĺ–≤, —Ā—ā—č–ļ–ĺ–≤ –ł –Ņ—Ä–ĺ—ā–ĺ–ļ–ĺ–Ľ–ĺ–≤ - —É–Ĺ–ł—Ą–ł–ļ–į—Ü–ł—Ź –≤–Ĺ—É—ā—Ä–ł —Ā–ł—Ā—ā–Ķ–ľ–Ĺ—č—Ö –ł

–ľ–Ķ–∂—Ā–ł—Ā—ā–Ķ–ľ–Ĺ—č—Ö —Ā–≤—Ź–∑–Ķ–Ļ, –≤–Ĺ—É—ā—Ä–ł—Ā–Ķ—ā–Ķ–≤—č—Ö –ł –ľ–Ķ–∂—Ā–Ķ—ā–Ķ–≤—č—Ö —Ā–≤—Ź–∑–Ķ–Ļ

—Ā —Ü–Ķ–Ľ—Ć—é —ć—Ą—Ą–Ķ–ļ—ā–ł–≤–Ĺ–ĺ–Ļ —Ä–Ķ–į–Ľ–ł–∑–į—Ü–ł–ł –Ņ—Ä–ĺ–≥—Ä–Ķ—Ā—Ā–ł–≤–Ĺ—č—Ö –ľ–Ķ—ā–ĺ–ī–ĺ–≤ –Ņ—Ä–ĺ–Ķ–ļ—ā–ł—Ä–ĺ–≤–į–Ĺ–ł—Ź –°–í–Ę.

–ě—Ā–Ĺ–ĺ–≤–Ĺ–į—Ź

—Ą—É–Ĺ–ļ—Ü–ł—Ź –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–ĺ–≤ –ł —Ā—ā—č–ļ–ĺ–≤ - –ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–Ķ–Ĺ–ł–Ķ –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ĺ–Ĺ–Ĺ–ĺ–Ļ, —ć–Ľ–Ķ–ļ—ā—Ä–ł—á–Ķ—Ā–ļ–ĺ–Ļ –ł

–ļ–ĺ–Ĺ—Ā—ā—Ä—É–ļ—ā–ł–≤–Ĺ–ĺ–Ļ —Ā–ĺ–≤–ľ–Ķ—Ā—ā–ł–ľ–ĺ—Ā—ā–ł –°–í–Ę.

–ė–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ĺ–Ĺ–Ĺ–į—Ź —Ā–ĺ–≤–ľ–Ķ—Ā—ā–ł–ľ–ĺ—Ā—ā—Ć - —Ā–ĺ–≥–Ľ–į—Ā–ĺ–≤–į–Ĺ–Ĺ–ĺ—Ā—ā—Ć –ī–Ķ–Ļ—Ā—ā–≤–ł–Ļ —Ą—É–Ĺ–ļ—Ü–ł–ĺ–Ĺ–į–Ľ—Ć–Ĺ—č—Ö —ć–Ľ–Ķ–ľ–Ķ–Ĺ—ā–ĺ–≤ –≤

—Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤–ł–ł —Ā —Ā–ĺ–≤–ĺ–ļ—É–Ņ–Ĺ–ĺ—Ā—ā—Ć—é –Ľ–ĺ–≥–ł—á–Ķ—Ā–ļ–ł—Ö —É—Ā–Ľ–ĺ–≤–ł–Ļ.

–õ–ĺ–≥–ł—á–Ķ—Ā–ļ–ł–Ķ

—É—Ā–Ľ–ĺ–≤–ł—Ź –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ĺ–Ĺ–Ĺ–ĺ–Ļ —Ā–ĺ–≤–ľ–Ķ—Ā—ā–ł–ľ–ĺ—Ā—ā–ł –ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ—Ź—é—ā —Ą—É–Ĺ–ļ—Ü–ł–ĺ–Ĺ–į–Ľ—Ć–Ĺ—É—é –ł —Ā—ā—Ä—É–ļ—ā—É—Ä–Ĺ—É—é

–ĺ—Ä–≥–į–Ĺ–ł–∑–į—Ü–ł—é –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į.

–≠–Ľ–Ķ–ļ—ā—Ä–ł—á–Ķ—Ā–ļ–į—Ź —Ā–ĺ–≤–ľ–Ķ—Ā—ā–ł–ľ–ĺ—Ā—ā—Ć - —Ā–ĺ–≥–Ľ–į—Ā–ĺ–≤–į–Ĺ–Ĺ–ĺ—Ā—ā—Ć —Ā—ā–į—ā–ł—Ā—ā–ł—á–Ķ—Ā–ļ–ł—Ö –ł –ī–ł–Ĺ–į–ľ–ł—á–Ķ—Ā–ļ–ł—Ö –Ņ–į—Ä–į–ľ–Ķ—ā—Ä–ĺ–≤

—ć–Ľ–Ķ–ļ—ā—Ä–ł—á–Ķ—Ā–ļ–ł—Ö —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ –≤ —Ā–ł—Ā—ā–Ķ–ľ–Ķ —ą–ł–Ĺ —Ā —É—á–Ķ—ā–ĺ–ľ –ĺ–≥—Ä–į–Ĺ–ł—á–Ķ–Ĺ–ł–Ļ –Ĺ–į –Ņ—Ä–ĺ—Ā—ā—Ä–į–Ĺ—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ–Ķ

—Ä–į–∑–ľ–Ķ—Č–Ķ–Ĺ–ł–Ķ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤ –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į –ł —ā–Ķ—Ö–Ĺ–ł—á–Ķ—Ā–ļ—É—é —Ä–Ķ–į–Ľ–ł–∑–į—Ü–ł—é –Ņ—Ä–ł–Ķ–ľ–ĺ–Ņ–Ķ—Ä–Ķ–ī–į—é—Č–ł—Ö

—ć–Ľ–Ķ–ľ–Ķ–Ĺ—ā–ĺ–≤ (–ü–ü–≠).

–ö–ĺ–Ĺ—Ā—ā—Ä—É–ļ—ā–ł–≤–Ĺ–į—Ź —Ā–ĺ–≤–ľ–Ķ—Ā—ā–ł–ľ–ĺ—Ā—ā—Ć - —Ā–ĺ–≥–Ľ–į—Ā–ĺ–≤–į–Ĺ–Ĺ–ĺ—Ā—ā—Ć –ļ–ĺ–Ĺ—Ā—ā—Ä—É–ļ—ā–ł–≤–Ĺ—č—Ö.

—ć–Ľ–Ķ–ľ–Ķ–Ĺ—ā–ĺ–≤ –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į, –Ņ—Ä–Ķ–ī–Ĺ–į–∑–Ĺ–į—á–Ķ–Ĺ–Ĺ—č—Ö –ī–Ľ—Ź –ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–Ķ–Ĺ–ł—Ź

–ľ–Ķ—Ö–į–Ĺ–ł—á–Ķ—Ā–ļ–ĺ–≥–ĺ –ļ–ĺ–Ĺ—ā–į–ļ—ā–į —Ā–ĺ–Ķ–ī–ł–Ĺ–Ķ–Ĺ–ł–Ļ –ł –ľ–Ķ—Ö–į–Ĺ–ł—á–Ķ—Ā–ļ–ĺ–Ļ –∑–į–ľ–Ķ–Ĺ—č —Ā—Ö–Ķ–ľ–Ĺ—č—Ö —ć–Ľ–Ķ–ľ–Ķ–Ĺ—ā–ĺ–≤,

–Ī–Ľ–ĺ–ļ–ĺ–≤ –ł —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤.

–õ–ł–Ĺ–ł–ł –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–ĺ–≤ ‚Äď —ć–Ľ–Ķ–ļ—ā—Ä–ł—á–Ķ—Ā–ļ–ł–Ķ —Ü–Ķ–Ņ–ł, —Ź–≤–Ľ—Ź—é—Č–ł–Ķ—Ā—Ź —Ā–ĺ—Ā—ā–į–≤–Ĺ—č–ľ–ł —Ą–ł–∑–ł—á–Ķ—Ā–ļ–ł–ľ–ł

—Ā–≤—Ź–∑—Ź–ľ–ł –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į.

–ú–į–≥–ł—Ā—ā—Ä–į–Ľ—Ć

- —Ā–ĺ–≤–ĺ–ļ—É–Ņ–Ĺ–ĺ—Ā—ā—Ć –≤—Ā–Ķ—Ö –Ľ–ł–Ĺ–ł–Ļ –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į. –í—č–ī–Ķ–Ľ—Ź—é—ā—Ā—Ź –ī–≤–Ķ –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ–ł:

-

–ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ĺ–Ĺ–Ĺ–ĺ–≥–ĺ –ļ–į–Ĺ–į–Ľ–į;

- —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź

–ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ĺ–Ĺ–Ĺ—č–ľ –ļ–į–Ĺ–į–Ľ–ĺ–ľ.

–ü–ĺ

–ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ĺ–Ĺ–Ĺ–ĺ–Ļ –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ–ł –Ņ–Ķ—Ä–Ķ–ī–į—é—ā—Ā—Ź –ļ–ĺ–ī—č –į–ī—Ä–Ķ—Ā–ĺ–≤, –ļ–ĺ–ľ–į–Ĺ–ī, –ī–į–Ĺ–Ĺ—č—Ö, —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź.

2. –ė–Ķ—Ä–į—Ä—Ö–ł—Ź —ą–ł–Ĺ

–®–ł–Ĺ–į -

—Ā–ĺ–≤–ĺ–ļ—É–Ņ–Ĺ–ĺ—Ā—ā—Ć –Ľ–ł–Ĺ–ł–Ļ, —Ā–≥—Ä—É–Ņ–Ņ–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č—Ö –Ņ–ĺ —Ą—É–Ĺ–ļ—Ü–ł–ĺ–Ĺ–į–Ľ—Ć–Ĺ–ĺ–ľ—É –Ĺ–į–∑–Ĺ–į—á–Ķ–Ĺ–ł—é. –ě–Ņ–Ķ—Ä–į—Ü–ł–ł –Ĺ–į

—ą–ł–Ĺ–Ķ –Ĺ–į–∑—č–≤–į—é—ā—Ā—Ź —ā—Ä–į–Ĺ–∑–į–ļ—Ü–ł—Ź–ľ–ł. –ě—Ā–Ĺ–ĺ–≤–Ĺ—č–Ķ

–≤–ł–ī—č —ā—Ä–į–Ĺ–∑–į–ļ—Ü–ł–Ļ ‚Äď —ā—Ä–į–Ĺ–∑–į–ļ—Ü–ł–ł –∑–į–Ņ–ł—Ā–ł

–ł —ā—Ä–į–Ĺ–∑–į–ļ—Ü–ł–ł —á—ā–Ķ–Ĺ–ł—Ź. –ē—Ā–Ľ–ł –≤ –ĺ–Ī–ľ–Ķ–Ĺ–Ķ —É—á–į—Ā—ā–≤—É—é—ā —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į –≤–≤–ĺ–ī–į /–≤—č–≤–ĺ–ī–į, –≥–ĺ–≤–ĺ—Ä—Ź—ā

–ĺ —ā—Ä–į–Ĺ–∑–į–ļ—Ü–ł—Ź—Ö –≤–≤–ĺ–ī–į/–≤—č–≤–ĺ–ī–į. –®–ł–Ĺ—č –į–ī—Ä–Ķ—Ā–į –Ņ—Ä–Ķ–ī–Ĺ–į–∑–Ĺ–į—á–Ķ–Ĺ—č –ī–Ľ—Ź –≤—č–Ī–ĺ—Ä–ļ–ł –≤ –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ–ł

—É–∑–Ľ–ĺ–≤ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į, —Ź—á–Ķ–Ķ–ļ –Ņ–į–ľ—Ź—ā–ł. –®–ł–Ĺ—č –ļ–ĺ–ľ–į–Ĺ–ī –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É—é—ā—Ā—Ź –ī–Ľ—Ź —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź

–ĺ–Ņ–Ķ—Ä–į—Ü–ł—Ź–ľ–ł –Ĺ–į –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ–ł. –í —Ā—ā–į–Ĺ–ī–į—Ä—ā–į—Ö –Ĺ–į –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā —Ä–Ķ–≥–Ľ–į–ľ–Ķ–Ĺ—ā–ł—Ä—É–Ķ—ā—Ā—Ź –ľ–ł–Ĺ–ł–ľ–į–Ľ—Ć–Ĺ–ĺ

–Ĺ–Ķ–ĺ–Ī—Ö–ĺ–ī–ł–ľ—č–Ļ –Ĺ–į–Ī–ĺ—Ä –ļ–ĺ–ľ–į–Ĺ–ī.

–®–ł–Ĺ—č

–ī–į–Ĺ–Ĺ—č—Ö –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É—é—ā—Ā—Ź –ī–Ľ—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –≤ –ĺ—Ā–Ĺ–ĺ–≤–Ĺ–ĺ–ľ –ī–≤–ĺ–ł—á–Ĺ—č—Ö –ļ–ĺ–ī–ĺ–≤ (–≤ —Ą–ĺ—Ä–ľ–į—ā–Ķ –ľ–į—ą–ł–Ĺ–Ĺ—č—Ö

–ļ–ĺ–ī–ĺ–≤ –≤–ĺ –≤–Ĺ—É—ā—Ä–ł—Ā–ł—Ā—ā–Ķ–ľ–Ĺ—č—Ö –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į—Ö, —Ā—ā–į–Ĺ–ī–į—Ä—ā–Ĺ—č—Ö –ļ–ĺ–ī–ĺ–≤ —ā–ł–Ņ–į ASCII –≤ –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į—Ö –ł–∑–ľ–Ķ—Ä–ł—ā–Ķ–Ľ—Ć–Ĺ—č—Ö —Ā–ł—Ā—ā–Ķ–ľ). –®–ł–Ĺ—č —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É—é—ā—Ā—Ź

–ī–Ľ—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á–ł —Ā–ĺ–ĺ–Ī—Č–Ķ–Ĺ–ł–Ļ, –ĺ–Ņ–ł—Ā—č–≤–į—é—Č–ł—Ö —Ä–Ķ–∑—É–Ľ—Ć—ā–į—ā –≤—č–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł—Ź –ĺ–Ņ–Ķ—Ä–į—Ü–ł–ł –Ĺ–į –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–Ķ

–ł–Ľ–ł —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤ —Ā–ĺ–Ņ—Ä—Ź–∂–Ķ–Ĺ–ł—Ź.

–®–ł–Ĺ–į

–Ņ–Ķ—Ä–Ķ–ī–į—á–ł —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ—ā—Ā—Ź –ī–Ľ—Ź —Ä–Ķ–į–Ľ–ł–∑–į—Ü–ł–ł –ĺ–Ņ–Ķ—Ä–į—Ü–ł–Ļ –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–Ĺ–ĺ–≥–ĺ –∑–į–Ĺ—Ź—ā–ł—Ź

–ľ–į–≥–ł—Ā—ā—Ä–į–Ľ–ł (–į—Ä–Ī–ł—ā—Ä–į–∂–į —Ä–Ķ—Ā—É—Ä—Ā–ĺ–≤ —ą–ł–Ĺ—č). –°–ĺ—Ā—ā–į–≤ –ł –ļ–ĺ–Ĺ—Ą–ł–≥—É—Ä–į—Ü–ł—Ź —ą–ł–Ĺ—č –∑–į–≤–ł—Ā—Ź—ā –ĺ—ā —Ā—ā—Ä—É–ļ—ā—É—Ä—č

—É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–ĺ–ľ. –†–į–∑–Ľ–ł—á–į—é—ā –ī–Ķ—Ü–Ķ–Ĺ—ā—Ä–į–Ľ–ł–∑–ĺ–≤–į–Ĺ–Ĺ—É—é –ł —Ü–Ķ–Ĺ—ā—Ä–į–Ľ–ł–∑–ĺ–≤–į–Ĺ–Ĺ—É—é

—Ā—ā—Ä—É–ļ—ā—É—Ä—č. –í –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į—Ö –ī–≤—É—Ö—ā–ĺ—á–Ķ—á–Ĺ–ĺ–≥–ĺ –Ņ–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł—Ź –ī–≤—É—Ö —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤ (—ā–ł–Ņ–į –ė–†–ü–†,

–ė–†–ü–°) —ą–ł–Ĺ–į –Ņ–Ķ—Ä–Ķ–ī–į—á–ł —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –ĺ—ā—Ā—É—ā—Ā—ā–≤—É–Ķ—ā.

–®–ł–Ĺ–į

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź –Ņ—Ä–ł–ľ–Ķ–Ĺ—Ź–Ķ—ā—Ā—Ź –≤ –ĺ—Ā–Ĺ–ĺ–≤–Ĺ–ĺ–ľ –≤ —Ā–ł—Ā—ā–Ķ–ľ–Ĺ—č—Ö –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į—Ö –≠–í–ú –ł –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–Ĺ–ĺ -

–ľ–ĺ–ī—É–Ľ—Ć–Ĺ—č—Ö —Ā–ł—Ā—ā–Ķ–ľ–į—Ö —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –ł –ł–∑–ľ–Ķ—Ä–Ķ–Ĺ–ł—Ź –ī–Ľ—Ź –ł–ī–Ķ–Ĺ—ā–ł—Ą–ł–ļ–į—Ü–ł–ł —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į,

–∑–į–Ņ—Ä–į—ą–ł–≤–į—é—Č–Ķ–≥–ĺ —Ā–Ķ–į–Ĺ—Ā —Ā–≤—Ź–∑–ł. –£—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–ĺ –ł–ī–Ķ–Ĺ—ā–ł—Ą–ł—Ü–ł—Ä—É–Ķ—ā—Ā—Ź –Ľ–ł–Ī–ĺ –į–ī—Ä–Ķ—Ā–ĺ–ľ –ł—Ā—ā–ĺ—á–Ĺ–ł–ļ–į

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź, –Ľ–ł–Ī–ĺ –į–ī—Ä–Ķ—Ā–ĺ–ľ –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—č –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź, —ā–į–ļ –Ĺ–į–∑—č–≤–į–Ķ–ľ—č–ľ –≤–Ķ–ļ—ā–ĺ—Ä–ĺ–ľ

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź.

–®–ł–Ĺ—č

—É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź —Ä–Ķ–∂–ł–ľ–ĺ–ľ —Ä–į–Ī–ĺ—ā—č –ł —Ā–Ņ–Ķ—Ü–ł–į–Ľ—Ć–Ĺ—č—Ö —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł—Ö —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ —Ā–ĺ–ī–Ķ—Ä–∂–į—ā –Ľ–ł–Ĺ–ł–ł,

–ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–ł–≤–į—é—Č–ł–Ķ —Ä–į–Ī–ĺ—ā–ĺ—Ā–Ņ–ĺ—Ā–ĺ–Ī–Ĺ–ĺ—Ā—ā—Ć –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į, –≤ —ā–ĺ–ľ —á–ł—Ā–Ľ–Ķ –Ņ—Ä–ł–≤–Ķ–ī–Ķ–Ĺ–ł–Ķ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤ –≤

–ł—Ā—Ö–ĺ–ī–Ĺ–ĺ–Ķ —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł–Ķ, –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ—Ć –ł—Ā—ā–ĺ—á–Ĺ–ł–ļ–ĺ–≤ –Ņ–ł—ā–į–Ĺ–ł—Ź, –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ—Ć –ł —Ā–Ľ—É–∂–Ī—É –≤—Ä–Ķ–ľ–Ķ–Ĺ–ł –ł

—ā.–Ņ.

–ē—Ā–Ľ–ł –ļ

—ą–ł–Ĺ–Ķ –Ņ–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ĺ –Ī–ĺ–Ľ—Ć—ą–ĺ–Ķ —á–ł—Ā–Ľ–ĺ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤, –Ķ–Ķ –Ņ—Ä–ĺ–Ņ—É—Ā–ļ–Ĺ–į—Ź —Ā–Ņ–ĺ—Ā–ĺ–Ī–Ĺ–ĺ—Ā—ā—Ć –Ņ–į–ī–į–Ķ—ā,

–Ņ–ĺ—Ā–ļ–ĺ–Ľ—Ć–ļ—É —Ā–Ľ–ł—ą–ļ–ĺ–ľ —á–į—Ā—ā–į—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á–į –Ņ—Ä–į–≤ —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź —ą–ł–Ĺ–ĺ–Ļ –ĺ—ā –ĺ–ī–Ĺ–ĺ–≥–ĺ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į –ļ

–ī—Ä—É–≥–ĺ–ľ—É –Ņ—Ä–ł–≤–ĺ–ī–ł—ā –ļ –ĺ—Č—É—ā–ł–ľ—č–ľ –∑–į–ī–Ķ—Ä–∂–ļ–į–ľ. –ü–ĺ —ć—ā–ĺ–Ļ –Ņ—Ä–ł—á–ł–Ĺ–Ķ –≤–ĺ –ľ–Ĺ–ĺ–≥–ł—Ö –í–ú

–Ņ—Ä–Ķ–ī–Ņ–ĺ—á—ā–Ķ–Ĺ–ł–Ķ –ĺ—ā–ī–į–Ķ—ā—Ā—Ź –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł—é –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ł—Ö —ą–ł–Ĺ, –ĺ–Ī—Ä–į–∑—É—é—Č–ł—Ö –ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ–Ķ–Ĺ–Ĺ—É—é –ł–Ķ—Ä–į—Ä—Ö–ł—é. –°–Ĺ–į—á–į–Ľ–į —Ä–į—Ā—Ā–ľ–ĺ—ā—Ä–ł–ľ –í–ú —Ā –ĺ–ī–Ĺ–ĺ–Ļ —ą–ł–Ĺ–ĺ–Ļ.

–í—č—á–ł—Ā–Ľ–ł—ā–Ķ–Ľ—Ć–Ĺ–į—Ź –ľ–į—ą–ł–Ĺ–į —Ā –ĺ–ī–Ĺ–ĺ–Ļ —ą–ł–Ĺ–ĺ–Ļ. –í —Ā—ā—Ä—É–ļ—ā—É—Ä–į—Ö –≤–∑–į–ł–ľ–ĺ—Ā–≤—Ź–∑–Ķ–Ļ —Ā –ĺ–ī–Ĺ–ĺ–Ļ —ą–ł–Ĺ–ĺ–Ļ

–ł–ľ–Ķ–Ķ—ā—Ā—Ź –ĺ–ī–Ĺ–į —Ā–ł—Ā—ā–Ķ–ľ–Ĺ–į—Ź —ą–ł–Ĺ–į, –ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–ł–≤–į—é—Č–į—Ź –ĺ–Ī–ľ–Ķ–Ĺ –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–Ķ–Ļ –ľ–Ķ–∂–ī—É –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ

–ł –Ņ–į–ľ—Ź—ā—Ć—é, –į —ā–į–ļ–∂–Ķ –ľ–Ķ–∂–ī—É –£–í–í —Ā –ĺ–ī–Ĺ–ĺ–Ļ —Ā—ā–ĺ—Ä–ĺ–Ĺ—č, –ł –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ –Ľ–ł–Ī–ĺ –Ņ–į–ľ—Ź—ā—Ć—é - —Ā

–ī—Ä—É–≥–ĺ–Ļ (–†–ł—Ā—É–Ĺ–ĺ–ļ 39). –Ē–Ľ—Ź —ā–į–ļ–ĺ–≥–ĺ –Ņ–ĺ–ī—Ö–ĺ–ī–į —Ö–į—Ä–į–ļ—ā–Ķ—Ä–Ĺ—č

–Ņ—Ä–ĺ—Ā—ā–ĺ—ā–į –ł –Ĺ–ł–∑–ļ–į—Ź —Ā—ā–ĺ–ł–ľ–ĺ—Ā—ā—Ć. –ě–ī–Ĺ–į–ļ–ĺ –ĺ–ī–Ĺ–ĺ—ą–ł–Ĺ–Ĺ–į—Ź –ĺ—Ä–≥–į–Ĺ–ł–∑–į—Ü–ł—Ź –Ĺ–Ķ –≤ —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł–ł

–ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–ł—ā—Ć –≤—č—Ā–ĺ–ļ—É—é –ł–Ĺ—ā–Ķ–Ĺ—Ā–ł–≤–Ĺ–ĺ—Ā—ā—Ć –ł —Ā–ļ–ĺ—Ä–ĺ—Ā—ā—Ć —ā—Ä–į–Ĺ–∑–į–ļ—Ü–ł–Ļ, –Ņ—Ä–ł—á–Ķ–ľ ¬ę—É–∑–ļ–ł–ľ –ľ–Ķ—Ā—ā–ĺ–ľ¬Ľ

—Ā—ā–į–Ĺ–ĺ–≤–ł—ā—Ā—Ź –ł–ľ–Ķ–Ĺ–Ĺ–ĺ —ą–ł–Ĺ–į.

–†–ł—Ā.¬† –°—ā—Ä—É–ļ—ā—É—Ä–į –≤–∑–į–ł–ľ–ĺ—Ā–≤—Ź–∑–Ķ–Ļ —Ā –ĺ–ī–Ĺ–ĺ–Ļ —ą–ł–Ĺ–ĺ–Ļ

–í—č—á–ł—Ā–Ľ–ł—ā–Ķ–Ľ—Ć–Ĺ–į—Ź –ľ–į—ą–ł–Ĺ–į —Ā –ī–≤—É–ľ—Ź –≤–ł–ī–į–ľ–ł —ą–ł–Ĺ. –•–ĺ—ā—Ź –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä—č —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤ –≤–≤–ĺ–ī–į/–≤—č–≤–ĺ–ī–į

(–£–í–í) –ľ–ĺ–≥—É—ā –Ī—č—ā—Ć –Ņ–ĺ–ī—Ā–ĺ–Ķ–ī–ł–Ĺ–Ķ–Ĺ—č –Ĺ–Ķ –Ņ–ĺ—Ā—Ä–Ķ–ī—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ –ļ —Ā–ł—Ā—ā–Ķ–ľ–Ĺ–ĺ–Ļ —ą–ł–Ĺ–Ķ, –Ī–ĺ–Ľ—Ć—ą–ł–Ļ —ć—Ą—Ą–Ķ–ļ—ā

–ī–ĺ—Ā—ā–ł–≥–į–Ķ—ā—Ā—Ź –Ņ—Ä–ł–ľ–Ķ–Ĺ–Ķ–Ĺ–ł–Ķ–ľ –ĺ–ī–Ĺ–ĺ–Ļ –ł–Ľ–ł –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ł—Ö —ą–ł–Ĺ –≤–≤–ĺ–ī–į/–≤—č–≤–ĺ–ī–į (–†–ł—Ā—É–Ĺ–ĺ–ļ 40). –£–í–í

–Ņ–ĺ–ī–ļ–Ľ—é—á–į—é—ā—Ā—Ź –ļ —ą–ł–Ĺ–į–ľ –≤–≤–ĺ–ī–į/–≤—č–≤–ĺ–ī–į, –ļ–ĺ—ā–ĺ—Ä—č–Ķ –Ī–Ķ—Ä—É—ā –Ĺ–į —Ā–Ķ–Ī—Ź –ĺ—Ā–Ĺ–ĺ–≤–Ĺ–ĺ–Ļ —ā—Ä–į—Ą–ł–ļ, –Ĺ–Ķ

—Ā–≤—Ź–∑–į–Ĺ–Ĺ—č–Ļ —Ā –≤—č—Ö–ĺ–ī–ĺ–ľ –Ĺ–į –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –ł–Ľ–ł –Ņ–į–ľ—Ź—ā—Ć. –ź–ī–į–Ņ—ā–Ķ—Ä—č —ą–ł–Ĺ –ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–ł–≤–į—é—ā

–Ī—É—Ą–Ķ—Ä–ł–∑–į—Ü–ł—é –ī–į–Ĺ–Ĺ—č—Ö –Ņ—Ä–ł –Ņ–Ķ—Ä–Ķ—Ā—č–Ľ–ļ–Ķ –ľ–Ķ–∂–ī—É —Ā–ł—Ā—ā–Ķ–ľ–Ĺ–ĺ–Ļ —ą–ł–Ĺ–ĺ–Ļ –ł –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–į–ľ–ł –£–í–í.

–†–ł—Ā. ¬†–°—ā—Ä—É–ļ—ā—É—Ä–į –≤–∑–į–ł–ľ–ĺ—Ā–≤—Ź–∑–Ķ–Ļ —Ā

–ī–≤—É–ľ—Ź –≤–ł–ī–į–ľ–ł —ą–ł–Ĺ

–≠—ā–ĺ

–Ņ–ĺ–∑–≤–ĺ–Ľ—Ź–Ķ—ā –í–ú –Ņ–ĺ–ī–ī–Ķ—Ä–∂–ł–≤–į—ā—Ć —Ä–į–Ī–ĺ—ā—É –ľ–Ĺ–ĺ–∂–Ķ—Ā—ā–≤–į —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤ –≤–≤–ĺ–ī–į/–≤—č–≤–ĺ–ī–į

–ł –ĺ–ī–Ĺ–ĺ–≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ–ĺ ¬ę—Ä–į–∑–≤—Ź–∑–į—ā—ƬĽ –ĺ–Ī–ľ–Ķ–Ĺ –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–Ķ–Ļ –Ņ–ĺ —ā—Ä–į–ļ—ā—É –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä - –Ņ–į–ľ—Ź—ā—Ć –ł

–ĺ–Ī–ľ–Ķ–Ĺ –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–Ķ–Ļ —Ā –£–í–í. –ü–ĺ–ī–ĺ–Ī–Ĺ–į—Ź —Ā—Ö–Ķ–ľ–į —Ā—É—Č–Ķ—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ —Ā–Ĺ–ł–∂–į–Ķ—ā –Ĺ–į–≥—Ä—É–∑–ļ—É –Ĺ–į

—Ā–ļ–ĺ—Ä–ĺ—Ā—ā–Ĺ—É—é —ą–ł–Ĺ—É ¬ę–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä-–Ņ–į–ľ—Ź—ā—ƬĽ –ł —Ā–Ņ–ĺ—Ā–ĺ–Ī—Ā—ā–≤—É–Ķ—ā –Ņ–ĺ–≤—č—ą–Ķ–Ĺ–ł—é –ĺ–Ī—Č–Ķ–Ļ

–Ņ—Ä–ĺ–ł–∑–≤–ĺ–ī–ł—ā–Ķ–Ľ—Ć–Ĺ–ĺ—Ā—ā–ł –í–ú.

–í—č—á–ł—Ā–Ľ–ł—ā–Ķ–Ľ—Ć–Ĺ–į—Ź –ľ–į—ą–ł–Ĺ–į —Ā —ā—Ä–Ķ–ľ—Ź –≤–ł–ī–į–ľ–ł —ą–ł–Ĺ. –Ē–Ľ—Ź –Ņ–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł—Ź –Ī—č—Ā—ā—Ä–ĺ–ī–Ķ–Ļ—Ā—ā–≤—É—é—Č–ł—Ö

–Ņ–Ķ—Ä–ł—Ą–Ķ—Ä–ł–Ļ–Ĺ—č—Ö —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤ –≤ —Ā–ł—Ā—ā–Ķ–ľ—É —ą–ł–Ĺ –ľ–ĺ–∂–Ķ—ā –Ī—č—ā—Ć –ī–ĺ–Ī–į–≤–Ľ–Ķ–Ĺ–į –≤—č—Ā–ĺ–ļ–ĺ—Ā–ļ–ĺ—Ä–ĺ—Ā—ā–Ĺ–į—Ź

—ą–ł–Ĺ–į —Ä–į—Ā—ą–ł—Ä–Ķ–Ĺ–ł—Ź.

–†–ł—Ā. –°—ā—Ä—É–ļ—ā—É—Ä–į –≤–∑–į–ł–ľ–ĺ—Ā–≤—Ź–∑–Ķ–Ļ —Ā —ā—Ä–Ķ–ľ—Ź –≤–ł–ī–į–ľ–ł —ą–ł–Ĺ

–®–ł–Ĺ—č

–≤–≤–ĺ–ī–į/–≤—č–≤–ĺ–ī–į –Ņ–ĺ–ī–ļ–Ľ—é—á–į—é—ā—Ā—Ź –ļ —ą–ł–Ĺ–Ķ —Ä–į—Ā—ą–ł—Ä–Ķ–Ĺ–ł—Ź, –į —É–∂–Ķ —Ā –Ĺ–Ķ–Ķ —á–Ķ—Ä–Ķ–∑ –į–ī–į–Ņ¬≠—ā–Ķ—Ä –ļ —ą–ł–Ĺ–Ķ

¬ę–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä-–Ņ–į–ľ—Ź—ā—ƬĽ. –°—Ö–Ķ–ľ–į –Ķ—Č–Ķ –Ī–ĺ–Ľ–Ķ–Ķ —Ā–Ĺ–ł–∂–į–Ķ—ā –Ĺ–į–≥—Ä—É–∑–ļ—É –Ĺ–į —ą–ł–Ĺ—É ¬ę–Ņ—Ä–ĺ¬≠—Ü–Ķ—Ā—Ā–ĺ—Ä-–Ņ–į–ľ—Ź—ā—ƬĽ.

–Ę–į–ļ—É—é –ĺ—Ä–≥–į–Ĺ–ł–∑–į—Ü–ł—é —ą–ł–Ĺ –Ĺ–į–∑—č–≤–į—é—ā –į—Ä—Ö–ł—ā–Ķ–ļ—ā—É—Ä–ĺ–Ļ

—Ā ¬ę–Ņ—Ä–ł—Ā—ā—Ä–ĺ–Ļ–ļ–ĺ–Ļ¬Ľ (mezzanine architecture).

–ė–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā (—ą–ł–Ĺ–į) Microbus. –ė–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā (—ą–ł–Ĺ–į) Microbus –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ľ—Ā—Ź –ī–Ľ—Ź –Ņ–ĺ—Ā—ā—Ä–ĺ–Ķ–Ĺ–ł—Ź 8 —Ä–į–∑—Ä—Ź–ī–Ĺ—č—Ö –ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–≤ Intel, Motorola 6800.

–ě–Ĺ —Ź–≤–Ľ—Ź–Ķ—ā—Ā—Ź —Ā–ł—Ā—ā–Ķ–ľ–Ĺ—č–ľ,

–ĺ–ī–Ĺ–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–Ĺ—č–ľ, –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ—Ć–Ĺ—č–ľ, –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ—č–ľ, –į—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ—č–ľ –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–ĺ–ľ —Ā

–Ņ–ĺ–Ľ—É–ī—É–Ņ–Ľ–Ķ–ļ—Ā–Ĺ–ĺ–Ļ (–ī–≤—É—Ā—ā–ĺ—Ä–ĺ–Ĺ–Ĺ–Ķ–Ļ –Ņ–ĺ–ĺ—á–Ķ—Ä–Ķ–ī–Ĺ–ĺ–Ļ) –Ņ–Ķ—Ä–Ķ–ī–į—á–Ķ–Ļ –ī–į–Ĺ–Ĺ—č—Ö. –ė–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā –Ņ–ĺ–Ľ—É—á–ł–Ľ

—ą–ł—Ä–ĺ–ļ–ĺ–Ķ —Ä–į—Ā–Ņ—Ä–ĺ—Ā—ā—Ä–į–Ĺ–Ķ–Ĺ–ł–Ķ –Ņ—Ä–ł –ĺ–Ī—ä–Ķ–ī–ł–Ĺ–Ķ–Ĺ–ł–ł –≤ —Ā–ł—Ā—ā–Ķ–ľ—É –Ĺ–Ķ –Ī–ĺ–Ľ–Ķ–Ķ 10 –Ņ–ĺ–ī–ļ–Ľ—é—á–į–Ķ–ľ—č—Ö –ļ

–ľ–į–≥–ł—Ā—ā—Ä–į–Ľ–ł –ė–°, —Ä–į—Ā–Ņ–ĺ–Ľ–ĺ–∂–Ķ–Ĺ–Ĺ—č—Ö –≤ –Ĺ–Ķ–Ņ–ĺ—Ā—Ä–Ķ–ī—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ–Ļ –Ī–Ľ–ł–∑–ĺ—Ā—ā–ł –ī—Ä—É–≥ –ĺ—ā –ī—Ä—É–≥–į.

–ė–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā Microbus –ł–ľ–Ķ–Ķ—ā 36 –Ľ–ł–Ĺ–ł–Ļ, –≤ —á–ł—Ā–Ľ–Ķ –ļ–ĺ—ā–ĺ—Ä—č—Ö 16-—Ä–į–∑—Ä—Ź–ī–Ĺ–į—Ź —ą–ł–Ĺ–į –į–ī—Ä–Ķ—Ā–į,

8-—Ä–į–∑—Ä—Ź–ī–Ĺ–į—Ź —ą–ł–Ĺ–į –ī–į–Ĺ–Ĺ—č—Ö –ł 12 –Ľ–ł–Ĺ–ł–Ļ —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź. –í –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–Ķ –į–ī—Ä–Ķ—Ā–Ĺ—č–Ķ

–Ņ—Ä–ĺ—Ā—ā—Ä–į–Ĺ—Ā—ā–≤–į –Ņ–į–ľ—Ź—ā–ł –ł –í–£ —Ä–į–∑–ī–Ķ–Ľ–Ķ–Ĺ—č, –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—é—ā—Ā—Ź –Ņ—Ä–ĺ—ā–ĺ–ļ–ĺ–Ľ—č –į–ī—Ä–Ķ—Ā–Ĺ–ĺ–≥–ĺ

(–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–Ĺ–ĺ–≥–ĺ) –ĺ–Ī–ľ–Ķ–Ĺ–į, –ĺ–Ī–ľ–Ķ–Ĺ–į –Ņ–ĺ –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź–ľ –ł –Ņ—Ä—Ź–ľ–ĺ–≥–ĺ –ī–ĺ—Ā—ā—É–Ņ–į –ļ –Ņ–į–ľ—Ź—ā–ł.

–ė–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā –ė-41

–ė–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā —Ä–į–∑—Ä–į–Ī–ĺ—ā–į–Ĺ —Ą–ł—Ä–ľ–ĺ–Ļ Intel Multibus –ł –Ĺ–į –Ķ–≥–ĺ –ĺ—Ā–Ĺ–ĺ–≤–Ķ —Ā–ĺ–∑–ī–į–Ĺ –ĺ—ā–Ķ—á–Ķ—Ā—ā–≤–Ķ–Ĺ–Ĺ—č–Ļ –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā –ė-41. –≠—ā–ĺ—ā

–ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā —Ź–≤–Ľ—Ź–Ķ—ā—Ā—Ź –ľ–Ĺ–ĺ–≥–ĺ–ľ–į—ą–ł–Ĺ–Ĺ—č–ľ, —Ā–ł—Ā—ā–Ķ–ľ–Ĺ—č–ľ, –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ—Ć–Ĺ—č–ľ, –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ—č–ľ,

–Ņ–ĺ–Ľ—É–ī—É–Ņ–Ľ–Ķ–ļ—Ā–Ĺ—č–ľ. –Ē–ĺ–Ņ—É—Ā–ļ–į–Ķ—ā—Ā—Ź –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł–Ķ 8- –ł 16-—Ä–į–∑—Ä—Ź–ī–Ĺ—č—Ö –ľ–ĺ–ī—É–Ľ–Ķ–Ļ, –ĺ–ī–ł–Ĺ –ł–∑

–ļ–ĺ—ā–ĺ—Ä—č—Ö (–į–ļ—ā–ł–≤–Ĺ—č–Ļ) –ł–≥—Ä–į–Ķ—ā —Ä–ĺ–Ľ—Ć –∑–į–ī–į—ā—á–ł–ļ–į, –ī—Ä—É–≥–ĺ–Ļ

(–Ņ–į—Ā—Ā–ł–≤–Ĺ—č–Ļ) - –ł—Ā–Ņ–ĺ–Ľ–Ĺ–ł—ā–Ķ–Ľ—Ź. –ü—Ä–ł –∑–į–Ņ—Ä–ĺ—Ā–į—Ö —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ—Ć—é –ĺ–ī–Ĺ–ĺ–≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ–ĺ –ĺ—ā

–Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ł—Ö –∑–į–ī–į—ā—á–ł–ļ–ĺ–≤ —Ä–Ķ—ą–į–Ķ—ā—Ā—Ź –∑–į–ī–į—á–į –į—Ä–Ī–ł—ā—Ä–į–∂–į. –í

—Ā–ĺ—Ā—ā–į–≤ –Ľ–ł–Ĺ–ł–Ļ –≤—Ö–ĺ–ī—Ź—ā 25-—Ä–į–∑—Ä—Ź–ī–Ĺ–į—Ź —ą–ł–Ĺ–į –į–ī—Ä–Ķ—Ā–į (–ĺ–ī–Ĺ–į –ł–∑ –Ķ–Ķ –Ľ–ł–Ĺ–ł–Ļ –Ņ–Ķ—Ä–Ķ–ī–į–Ķ—ā –Ņ—Ä–ł–∑–Ĺ–į–ļ

–ī–≤—É—Ö–Ī–į–Ļ—ā–Ĺ–ĺ–Ļ –Ņ–Ķ—Ä–Ķ–ī–į—á–ł), 16-—Ä–į–∑—Ä—Ź–ī–Ĺ–į—Ź —ą–ł–Ĺ–į –ī–į–Ĺ–Ĺ—č—Ö –ł –ī–≤–Ķ –Ľ–ł–Ĺ–ł–ł –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ—Ź –ļ–į–∂–ī–ĺ–≥–ĺ

–Ī–į–Ļ—ā–į –Ĺ–į —á–Ķ—ā–Ĺ–ĺ—Ā—ā—Ć, 8-—Ä–į–∑—Ä—Ź–ī–Ĺ–į—Ź —ą–ł–Ĺ–į —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –į–ī—Ä–Ķ—Ā–Ĺ—č–ľ (–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–Ĺ—č–ľ) –ĺ–Ī–ľ–Ķ–Ĺ–ĺ–ľ,

9-—Ä–į–∑—Ä—Ź–ī–Ĺ–į—Ź —ą–ł–Ĺ–į –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ, 7-—Ä–į–∑—Ä—Ź–ī–Ĺ–į—Ź —ą–ł–Ĺ–į —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–ĺ–ľ,

10-—Ä–į–∑—Ä—Ź–ī–Ĺ–į—Ź –≤—Ā–Ņ–ĺ–ľ–ĺ–≥–į—ā–Ķ–Ľ—Ć–Ĺ–į—Ź —ą–ł–Ĺ–į –ł —ą–ł–Ĺ–į –ł—Ā—ā–ĺ—á–Ĺ–ł–ļ–ĺ–≤ –Ņ–ł—ā–į–Ĺ–ł—Ź. –Ě–į –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–Ķ –ė-41

–∑–į–ī–į–Ĺ—č –Ņ—Ä–ĺ—ā–ĺ–ļ–ĺ–Ľ—č:

- –į–ī—Ä–Ķ—Ā–Ĺ–ĺ–≥–ĺ –ĺ–Ī–ľ–Ķ–Ĺ–į (—Ā –≤–ĺ–∑–ľ–ĺ–∂–Ĺ—č–ľ –∑–į–Ņ—Ä–Ķ—ā–ĺ–ľ –ĺ–Ī—Ä–į—Č–Ķ–Ĺ–ł—Ź);

- –į—Ä–Ī–ł—ā—Ä–į–∂–į –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤ –∑–į–ī–į—ā—á–ł–ļ–ĺ–≤ –Ĺ–į

—É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł–Ķ –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ—Ć—é –ł —Ā–ľ–Ķ–Ĺ—č –∑–į–ī–į—ā—á–ł–ļ–į;

- –ĺ–Ī—Ä–į–Ī–ĺ—ā–ļ–ł –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ;

- –į–≤–į—Ä–ł–ł –≤ —Ā–ł—Ā—ā–Ķ–ľ–Ķ —ć–Ľ–Ķ–ļ—ā—Ä–ĺ–Ņ–ł—ā–į–Ĺ–ł—Ź.

–ė–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā –ú–ü–ė

–ė–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā –ú–ü–ė (–Ĺ–į –ĺ—Ā–Ĺ–ĺ–≤–Ķ Q-bus) - –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ—Ć–Ĺ—č–Ļ, –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ—č–Ļ, –Ņ–ĺ–Ľ—É–ī—É–Ņ–Ľ–Ķ–ļ—Ā–Ĺ—č–Ļ,

–į—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ—č–Ļ –Ņ—Ä–ł –Ņ–Ķ—Ä–Ķ–ī–į—á–Ķ –ī–į–Ĺ–Ĺ—č—Ö –ł —Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ—č–Ļ –Ņ—Ä–ł –Ņ–Ķ—Ä–Ķ–ī–į—á–Ķ –į–ī—Ä–Ķ—Ā–į. –ź–ī—Ä–Ķ—Ā –ł

–ī–į–Ĺ–Ĺ—č–Ķ –Ņ–Ķ—Ä–Ķ–ī–į—é—ā—Ā—Ź –Ņ–ĺ –ĺ–ī–Ĺ–ĺ–Ļ –ł —ā–ĺ–Ļ –∂–Ķ —ą–ł–Ĺ–Ķ —Ā —Ä–į–∑–ī–Ķ–Ľ–Ķ–Ĺ–ł–Ķ–ľ –≤–ĺ –≤—Ä–Ķ–ľ–Ķ–Ĺ–ł

(–ľ—É–Ľ—Ć—ā–ł–Ņ–Ľ–Ķ–ļ—Ā–ł—Ä—É–Ķ–ľ–ĺ–Ļ —ą–ł–Ĺ–Ķ –į–ī—Ä–Ķ—Ā–ĺ–≤-–ī–į–Ĺ–Ĺ—č—Ö). –ě—Ā–Ĺ–ĺ–≤–Ĺ–ĺ–Ķ –Ĺ–į–∑–Ĺ–į—á–Ķ–Ĺ–ł–Ķ –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į -

–Ņ–ĺ—Ā—ā—Ä–ĺ–Ķ–Ĺ–ł–Ķ –ĺ–ī–Ĺ–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–Ĺ—č—Ö —Ā–ł—Ā—ā–Ķ–ľ, —ā–ĺ—á–Ĺ–Ķ–Ķ, —Ā–ł—Ā—ā–Ķ–ľ —Ā –ĺ–ī–Ĺ–ł–ľ –≤–Ķ–ī—É—Č–ł–ľ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ.

–í—č–Ņ–ĺ–Ľ–Ĺ—Ź—é—ā—Ā—Ź –į–ī—Ä–Ķ—Ā–Ĺ—č–Ļ –ĺ–Ī–ľ–Ķ–Ĺ (–≤ —ā–ĺ–ľ —á–ł—Ā–Ľ–Ķ –ł –Ī–Ľ–ĺ—á–Ĺ—č–Ļ), –∑–į—Ö–≤–į—ā –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ–ł –ł

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź. –ź–ī—Ä–Ķ—Ā–Ĺ–ĺ–Ķ –Ņ—Ä–ĺ—Ā—ā—Ä–į–Ĺ—Ā—ā–≤–ĺ –Ņ–į–ľ—Ź—ā–ł –ł –í–£ - –ĺ–Ī—Č–Ķ–Ķ (–ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā "—Ā –ĺ–Ī—Č–Ķ–Ļ

—ą–ł–Ĺ–ĺ–Ļ") –ł –ľ–ĺ–∂–Ķ—ā —Ā–ĺ—Ā—ā–į–≤–Ľ—Ź—ā—Ć 64 –ö (16-—Ä–į–∑—Ä—Ź–ī–Ĺ—č–Ļ

–į–ī—Ä–Ķ—Ā) –ł–Ľ–ł 16 –ú (24-—Ä–į–∑—Ä—Ź–ī–Ĺ—č–Ļ –į–ī—Ä–Ķ—Ā). –§–ĺ—Ä–ľ–į—ā –ī–į–Ĺ–Ĺ—č—Ö - –Ī–į–Ļ—ā –ł–Ľ–ł –ī–≤–į –Ī–į–Ļ—ā–į. –Ē–Ľ—Ź

–į–ī—Ä–Ķ—Ā–į—Ü–ł–ł –í–£ –ĺ—ā–≤–ĺ–ī–ł—ā—Ā—Ź 8–ö –≤ –ļ–ĺ–Ĺ—Ü–Ķ –ź–ü. –ú—É–Ľ—Ć—ā–ł–Ņ–Ľ–Ķ–ļ—Ā–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ –į–ī—Ä–Ķ—Ā–ĺ–≤ –ł –ī–į–Ĺ–Ĺ—č—Ö

—Ā–Ĺ–ł–∂–į–Ķ—ā –Ņ—Ä–ĺ–Ņ—É—Ā–ļ–Ĺ—É—é —Ā–Ņ–ĺ—Ā–ĺ–Ī–Ĺ–ĺ—Ā—ā—Ć –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į, –Ĺ–ĺ –∑–Ĺ–į—á–ł—ā–Ķ–Ľ—Ć–Ĺ–ĺ —É–ľ–Ķ–Ĺ—Ć—ą–į–Ķ—ā —á–ł—Ā–Ľ–ĺ –Ľ–ł–Ĺ–ł–Ļ

—Ā–≤—Ź–∑–ł, —É–Ņ—Ä–ĺ—Č–į—Ź –ł —É–ī–Ķ—ą–Ķ–≤–Ľ—Ź—Ź —ą–ł–Ĺ—É.

–í –≠–í–ú IBM PC/AT –Ņ—Ä–ł–ľ–Ķ–Ĺ—Ź—é—ā—Ā—Ź –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā—č (—ą–ł–Ĺ—č) ISA,

EISA (Extended ISA) –ł–Ľ–ł MCA (–ľ–ł–ļ—Ä–ĺ–ļ–į–Ĺ–į–Ľ). –Ě–į —É—Ä–ĺ–≤–Ĺ–Ķ –Ľ–ĺ–ļ–į–Ľ—Ć–Ĺ—č—Ö —ą–ł–Ĺ —Ā–Ķ–Ļ—á–į—Ā —ą–ł—Ä–ĺ–ļ–ĺ

–Ņ—Ä–ł–ľ–Ķ–Ĺ—Ź–Ķ—ā—Ā—Ź —ą–ł–Ĺ–į PCI (—Ą–ł—Ä–ľ—č Intel), –ł–∑–≤–Ķ—Ā—ā–Ĺ–į —ą–ł–Ĺ–į VL-bus

–ł –ī—Ä. –Ę–į–ļ—ā–ĺ–≤–į—Ź —á–į—Ā—ā–ĺ—ā–į —Ā–ĺ–≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ—č—Ö —Ā–ł—Ā—ā–Ķ–ľ–Ĺ—č—Ö —ą–ł–Ĺ —Ā–ĺ—Ā—ā–į–≤–Ľ—Ź–Ķ—ā 66... 133 –ú–ď—Ü –ł

–≤—č—ą–Ķ.

3. –®–ł–Ĺ–Ĺ—č–Ķ —Ą–ĺ—Ä–ľ–ł—Ä–ĺ–≤–į—ā–Ķ–Ľ–ł –ł

–Ī—É—Ą–Ķ—Ä–Ĺ—č–Ķ —Ä–Ķ–≥–ł—Ā—ā—Ä—č

–®–ł–Ĺ–Ĺ—č–Ķ —Ą–ĺ—Ä–ľ–ł—Ä–ĺ–≤–į—ā–Ķ–Ľ–ł (–®–§), –Ĺ–į–∑—č–≤–į–Ķ–ľ—č–Ķ —ā–į–ļ–∂–Ķ –Ņ—Ä–ł–Ķ–ľ–ĺ–Ņ–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ–į–ľ–ł, —ą–ł–Ĺ–Ĺ—č–ľ–ł

–ī—Ä–į–Ļ–≤–Ķ—Ä–į–ľ–ł –ł–Ľ–ł –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ—Ć–Ĺ—č–ľ–ł –≤–Ķ–Ĺ—ā–ł–Ľ—Ć - –Ī—É—Ą–Ķ—Ä–į–ľ–ł, –≤–ļ–Ľ—é—á–į—é—ā—Ā—Ź –ľ–Ķ–∂–ī—É –ł—Ā—ā–ĺ—á–Ĺ–ł–ļ–ĺ–ľ

–ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł –ł —ą–ł–Ĺ–ĺ–Ļ. –ě–Ĺ–ł —É—Ā–ł–Ľ–ł–≤–į—é—ā —Ā–ł–≥–Ĺ–į–Ľ—č –Ņ–ĺ –ľ–ĺ—Č–Ĺ–ĺ—Ā—ā–ł –Ņ—Ä–ł —Ä–į–Ī–ĺ—ā–Ķ –Ĺ–į —ą–ł–Ĺ—É,

–ĺ—ā–ļ–Ľ—é—á–į—é—ā –ł—Ā—ā–ĺ—á–Ĺ–ł–ļ –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł –ĺ—ā —ą–ł–Ĺ—č, –ļ–ĺ–≥–ī–į –ĺ–Ĺ –Ĺ–Ķ —É—á–į—Ā—ā–≤—É–Ķ—ā –≤ –ĺ–Ī–ľ–Ķ–Ĺ–Ķ,

—Ą–ĺ—Ä–ľ–ł—Ä—É—é—ā –Ņ—Ä–ł –Ĺ–Ķ–ĺ–Ī—Ö–ĺ–ī–ł–ľ–ĺ—Ā—ā–ł —ā—Ä–Ķ–Ī—É–Ķ–ľ—č–Ķ —É—Ä–ĺ–≤–Ĺ–ł —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ –Ľ–ĺ–≥–ł—á–Ķ—Ā–ļ–ĺ–Ļ 1 –ł–Ľ–ł 0.

–Ē–≤—É–Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–Ĺ—č–Ķ –®–§ –Ņ–ĺ–∑–≤–ĺ–Ľ—Ź—é—ā –≤ –∑–į–≤–ł—Ā–ł–ľ–ĺ—Ā—ā–ł –ĺ—ā —Ā–ł–≥–Ĺ–į–Ľ–į —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –Ņ–Ķ—Ä–Ķ–ī–į–≤–į—ā—Ć

—Ā–ł–≥–Ĺ–į–Ľ—č –≤ —ą–ł–Ĺ—É –ł–Ľ–ł, –Ĺ–į–Ņ—Ä–ĺ—ā–ł–≤, –Ņ—Ä–ł–Ĺ–ł–ľ–į—ā—Ć –ł—Ö —Ā —ą–ł–Ĺ—č –ł –Ņ–Ķ—Ä–Ķ–ī–į–≤–į—ā—Ć –Ņ—Ä–ł–Ķ–ľ–Ĺ–ł–ļ—É

–ī–į–Ĺ–Ĺ—č—Ö.

–Ď—É—Ą–Ķ—Ä–Ĺ—č–Ķ —Ä–Ķ–≥–ł—Ā—ā—Ä—č. –Ď—É—Ą–Ķ—Ä–Ĺ—č–Ķ

—Ä–Ķ–≥–ł—Ā—ā—Ä—č —Ā–Ľ—É–∂–į—ā –ī–Ľ—Ź –Ņ–ĺ–ī–ļ–Ľ—é—á–Ķ–Ĺ–ł—Ź –ļ –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ–ł –≤–Ĺ–Ķ—ą–Ĺ–Ķ–≥–ĺ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į. –í –ĺ—ā–Ľ–ł—á–ł–Ķ –ĺ—ā

–®–§, –Ī—É—Ą–Ķ—Ä–Ĺ—č–Ķ —Ä–Ķ–≥–ł—Ā—ā—Ä—č —Ā–Ņ–ĺ—Ā–ĺ–Ī–Ĺ—č —Ö—Ä–į–Ĺ–ł—ā—Ć –ī–į–Ĺ–Ĺ—č–Ķ. –Ď–Ľ–į–≥–ĺ–ī–į—Ä—Ź —ć—ā–ĺ–ľ—É –ĺ–Ĺ–ł –ľ–ĺ–≥—É—ā

–≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—ā—Ć –≤—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ—É—é –Ī—É—Ą–Ķ—Ä–ł–∑–į—Ü–ł—é –ī–į–Ĺ–Ĺ—č—Ö, —á—ā–ĺ —Ā–ĺ—Ā—ā–į–≤–Ľ—Ź–Ķ—ā –≤–į–∂–Ĺ–Ķ–Ļ—ą—É—é —Ą—É–Ĺ–ļ—Ü–ł—é

–Ņ–ĺ—Ä—ā–ĺ–≤. –Ď—É—Ą–Ķ—Ä–Ĺ—č–Ķ –ļ–į—Ā–ļ–į–ī—č —Ā —ā—Ä–Ķ–ľ—Ź —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź–ľ–ł –Ĺ–į –≤—č—Ö–ĺ–ī–į—Ö —Ä–Ķ–≥–ł—Ā—ā—Ä–į –ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–ł–≤–į—é—ā

–Ņ–ĺ—Ä—ā–į–ľ –≤–ĺ–∑–ľ–ĺ–∂–Ĺ–ĺ—Ā—ā—Ć –ĺ—ā–ļ–Ľ—é—á–Ķ–Ĺ–ł—Ź –ĺ—ā –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ–ł –Ņ–ĺ–ī –ī–Ķ–Ļ—Ā—ā–≤–ł–Ķ–ľ —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł—Ö —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤,

–į —ā–į–ļ–∂–Ķ –Ĺ–Ķ–ĺ–Ī—Ö–ĺ–ī–ł–ľ—É—é –Ĺ–į–≥—Ä—É–∑–ĺ—á–Ĺ—É—é —Ā–Ņ–ĺ—Ā–ĺ–Ī–Ĺ–ĺ—Ā—ā—Ć.

–ß–Ķ—Ä–Ķ–∑ –Ņ–ĺ—Ä—ā—č –≤–≤–ĺ–ī–į

–ī–į–Ĺ–Ĺ—č–Ķ –ĺ—ā –í–£ –Ņ–ĺ—Ā—ā—É–Ņ–į—é—ā –≤ –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ—Ć, –į —á–Ķ—Ä–Ķ–∑ –Ņ–ĺ—Ä—ā—č –≤—č–≤–ĺ–ī–į –ī–į–Ĺ–Ĺ—č–Ķ —Ā –ľ–į–≥–ł—Ā—ā—Ä–į–Ľ–ł

–Ņ–Ķ—Ä–Ķ–ī–į—é—ā—Ā—Ź —ā–ĺ–ľ—É –ł–Ľ–ł –ł–Ĺ–ĺ–ľ—É –ľ–ĺ–ī—É–Ľ—é. –ü–ĺ—Ä—ā—č –≤–≤–ĺ–ī–į-–≤—č–≤–ĺ–ī–į –ľ–ĺ–≥—É—ā –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—ā—Ć –ĺ–Ī–Ķ

—É–ļ–į–∑–į–Ĺ–Ĺ—č–Ķ –ĺ–Ņ–Ķ—Ä–į—Ü–ł–ł.

4. –ü–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ—č–Ķ –Ņ–Ķ—Ä–ł—Ą–Ķ—Ä–ł–Ļ–Ĺ—č–Ķ –į–ī–į–Ņ—ā–Ķ—Ä—č

–°–Ľ–ĺ–∂–Ĺ—č–Ķ –ĺ–Ņ–Ķ—Ä–į—Ü–ł–ł –Ņ–ĺ –Ņ–Ķ—Ä–Ķ–ī–į—á–Ķ –ī–į–Ĺ–Ĺ—č—Ö –Ņ–ĺ —ą–ł–Ĺ–Ķ

–≤—č–Ņ–ĺ–Ľ–Ĺ—Ź—é—ā—Ā—Ź –Ņ–Ķ—Ä–ł—Ą–Ķ—Ä–ł–Ļ–Ĺ—č–ľ–ł –į–ī–į–Ņ—ā–Ķ—Ä–į–ľ–ł. –ü—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä—É–Ķ–ľ–ĺ—Ā—ā—Ć –į–ī–į–Ņ—ā–Ķ—Ä–ĺ–≤ –ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–ł–≤–į–Ķ—ā

–ł–ľ —ą–ł—Ä–ĺ–ļ—É—é –ĺ–Ī–Ľ–į—Ā—ā—Ć –Ņ—Ä–ł–ľ–Ķ–Ĺ–Ķ–Ĺ–ł—Ź –≤—Ā–Ľ–Ķ–ī—Ā—ā–≤–ł–Ķ –ł–∑–ľ–Ķ–Ĺ—Ź–Ķ–ľ–ĺ—Ā—ā–ł –Ņ—Ä–ĺ—Ü–Ķ–ī—É—Ä –ĺ–Ī–ľ–Ķ–Ĺ–į –Ī–Ķ–∑ –ł–∑–ľ–Ķ–Ĺ–Ķ–Ĺ–ł–Ļ

–≤ —Ā—Ö–Ķ–ľ–Ķ (—Ā –Ņ–ĺ–ľ–ĺ—Č—Ć—é –ļ–ĺ–ľ–į–Ĺ–ī –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—č), –≤ —ā–ĺ–ľ —á–ł—Ā–Ľ–Ķ –ł –≤–ĺ –≤—Ä–Ķ–ľ—Ź —Ä–į–Ī–ĺ—ā—č

–ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–Ĺ–ĺ–Ļ —Ā–ł—Ā—ā–Ķ–ľ—č.

–ü–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ—č–Ļ –Ņ–Ķ—Ä–ł—Ą–Ķ—Ä–ł–Ļ–Ĺ—č–Ļ –į–ī–į–Ņ—ā–Ķ—Ä (–ü–ü–ź, PPI) —ā–ł–Ņ–į Intel 8255–ź, –ł–ľ–Ķ—é—Č–ł–Ļ –ĺ—ā–Ķ—á–Ķ—Ā—ā–≤–Ķ–Ĺ–Ĺ—č–Ļ –į–Ĺ–į–Ľ–ĺ–≥ –ö580–í–í55–į (–†–ł—Ā—É–Ĺ–ĺ–ļ 42)

–ł–ľ–Ķ–Ķ—ā —ā—Ä–ł –ī–≤—É–Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–Ĺ—č—Ö 8-—Ä–į–∑—Ä—Ź–ī–Ĺ—č—Ö –Ņ–ĺ—Ä—ā–į –†–ź, –†–í –ł PC,

–Ņ—Ä–ł—á–Ķ–ľ –Ņ–ĺ—Ä—ā PC —Ä–į–∑–ī–Ķ–Ľ–Ķ–Ĺ –Ĺ–į –ī–≤–į —á–Ķ—ā—č—Ä–Ķ—Ö—Ä–į–∑—Ä—Ź–ī–Ĺ—č—Ö –ļ–į–Ĺ–į–Ľ–į: —Ā—ā–į—Ä—ą–ł–Ļ –†–°H –ł –ľ–Ľ–į–ī—ą–ł–Ļ PCL. –ě–Ī–ľ–Ķ–Ĺ

–ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–Ķ–Ļ –ľ–Ķ–∂–ī—É –ļ–į–Ĺ–į–Ľ–į–ľ–ł –ź, –í, –° –ł —ą–ł–Ĺ–ĺ–Ļ –ī–į–Ĺ–Ĺ—č—Ö –ú–ü–°

–Ņ—Ä–ĺ–ł–∑–≤–ĺ–ī–ł—ā—Ā—Ź —á–Ķ—Ä–Ķ–∑ –Ī—É—Ą–Ķ—Ä –ī–į–Ĺ–Ĺ—č—Ö BD –≤ —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤–ł–ł —Ā

—Ā–ł–≥–Ĺ–į–Ľ–į–ľ–ł —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź. –Ď–Ľ–ĺ–ļ —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź —á—ā–Ķ–Ĺ–ł–Ķ–ľ/–∑–į–Ņ–ł—Ā—Ć—é –Ņ–ĺ–Ľ—É—á–į–Ķ—ā —Ā—ā—Ä–ĺ–Ī—č —á—ā–Ķ–Ĺ–ł—Ź –ł

–∑–į–Ņ–ł—Ā–ł ![]() ¬†–ł

¬†–ł ![]() ¬†(—ć—ā–ĺ —Ā–ł–≥–Ĺ–į–Ľ—č

¬†(—ć—ā–ĺ —Ā–ł–≥–Ĺ–į–Ľ—č ![]() ¬†–ł

¬†–ł ![]() ¬†—Ā—ā–į–Ĺ–ī–į—Ä—ā–Ĺ–ĺ–≥–ĺ –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į), —Ā–ł–≥–Ĺ–į–Ľ —Ā–Ī—Ä–ĺ—Ā–į RESET, —Ā–ł–≥–Ĺ–į–Ľ –≤—č–Ī–ĺ—Ä–į –į–ī–į–Ņ—ā–Ķ—Ä–į

¬†—Ā—ā–į–Ĺ–ī–į—Ä—ā–Ĺ–ĺ–≥–ĺ –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į), —Ā–ł–≥–Ĺ–į–Ľ —Ā–Ī—Ä–ĺ—Ā–į RESET, —Ā–ł–≥–Ĺ–į–Ľ –≤—č–Ī–ĺ—Ä–į –į–ī–į–Ņ—ā–Ķ—Ä–į ![]() , –Ņ–ĺ–Ľ—É—á–į–Ķ–ľ—č–Ļ –ī–Ķ–ļ–ĺ–ī–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ–ľ

—Ā—ā–į—Ä—ą–ł—Ö —Ä–į–∑—Ä—Ź–ī–ĺ–≤ –Ķ–≥–ĺ –į–ī—Ä–Ķ—Ā–į, –ł –ī–≤–į –ľ–Ľ–į–ī—ą–ł—Ö —Ä–į–∑—Ä—Ź–ī–į –į–ī—Ä–Ķ—Ā–į A1 –ł –ź0 –ī–Ľ—Ź –į–ī—Ä–Ķ—Ā–į—Ü–ł–ł –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–ł—Ö

—Ä–Ķ–≥–ł—Ā—ā—Ä–ĺ–≤. –ź–ī—Ä–Ķ—Ā—É–Ķ–ľ—č—Ö –ĺ–Ī—ä–Ķ–ļ—ā–ĺ–≤ 5: —ā—Ä–ł –Ņ–ĺ—Ä—ā–į (–ź, –í –ł –°), —Ä–Ķ–≥–ł—Ā—ā—Ä —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–Ķ–≥–ĺ

—Ā–Ľ–ĺ–≤–į –†–£–° –ł –ļ–ĺ–ľ–į–Ĺ–ī–į —É—Ā—ā–į–Ĺ–ĺ–≤–ļ–ł/—Ā–Ī—Ä–ĺ—Ā–į –Ī–ł—ā–ĺ–≤ –Ņ–ĺ—Ä—ā–į –° BSR (Bit-Set/Reset).

, –Ņ–ĺ–Ľ—É—á–į–Ķ–ľ—č–Ļ –ī–Ķ–ļ–ĺ–ī–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ–ľ

—Ā—ā–į—Ä—ą–ł—Ö —Ä–į–∑—Ä—Ź–ī–ĺ–≤ –Ķ–≥–ĺ –į–ī—Ä–Ķ—Ā–į, –ł –ī–≤–į –ľ–Ľ–į–ī—ą–ł—Ö —Ä–į–∑—Ä—Ź–ī–į –į–ī—Ä–Ķ—Ā–į A1 –ł –ź0 –ī–Ľ—Ź –į–ī—Ä–Ķ—Ā–į—Ü–ł–ł –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–ł—Ö

—Ä–Ķ–≥–ł—Ā—ā—Ä–ĺ–≤. –ź–ī—Ä–Ķ—Ā—É–Ķ–ľ—č—Ö –ĺ–Ī—ä–Ķ–ļ—ā–ĺ–≤ 5: —ā—Ä–ł –Ņ–ĺ—Ä—ā–į (–ź, –í –ł –°), —Ä–Ķ–≥–ł—Ā—ā—Ä —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–Ķ–≥–ĺ

—Ā–Ľ–ĺ–≤–į –†–£–° –ł –ļ–ĺ–ľ–į–Ĺ–ī–į —É—Ā—ā–į–Ĺ–ĺ–≤–ļ–ł/—Ā–Ī—Ä–ĺ—Ā–į –Ī–ł—ā–ĺ–≤ –Ņ–ĺ—Ä—ā–į –° BSR (Bit-Set/Reset).

–†–ł—Ā.

–°—ā—Ä—É–ļ—ā—É—Ä–į –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ–ĺ–≥–ĺ –Ņ–Ķ—Ä–ł—Ą–Ķ—Ä–ł–Ļ–Ĺ–ĺ–≥–ĺ –į–ī–į–Ņ—ā–Ķ—Ä–į

–ź–ī—Ä–Ķ—Ā–į—Ü–ł—Ź –ł –Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł–Ķ

–Ņ–Ķ—Ä–Ķ–ī–į—á –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł –ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ—Ź—é—ā—Ā—Ź —Ā–ĺ–≥–Ľ–į—Ā–Ĺ–ĺ —ā–į–Ī–Ľ–ł—Ü–Ķ 1. –ö–į–ļ –≤–ł–ī–Ĺ–ĺ –ł–∑ —ā–į–Ī–Ľ–ł—Ü—č, –į–ī—Ä–Ķ—Ā

A1A0 = 11 —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É–Ķ—ā –Ņ–Ķ—Ä–Ķ–ī–į—á–Ķ

—É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł—Ö —Ā–Ľ–ĺ–≤ –†–£–° (–£–°1) –ł–Ľ–ł BSR (–£–°2), –Ņ—Ä–ł—á–Ķ–ľ —á—ā–Ķ–Ĺ–ł–Ķ –Ņ–ĺ —ć—ā–ĺ–ľ—É –į–ī—Ä–Ķ—Ā—É –∑–į–Ņ—Ä–Ķ—Č–Ķ–Ĺ–ĺ,

–ī–ĺ–Ņ—É—Ā–ļ–į–Ķ—ā—Ā—Ź —ā–ĺ–Ľ—Ć–ļ–ĺ –∑–į–Ņ–ł—Ā—Ć. –ü–Ķ—Ä–Ķ–ī–į—á–į –ī–≤—É—Ö —Ä–į–∑–Ĺ—č—Ö –£–° –Ņ—Ä–ł –ĺ–ī–Ĺ–ĺ–ľ –ł —ā–ĺ–ľ –∂–Ķ –į–ī—Ä–Ķ—Ā–Ķ

–≤–ĺ–∑–ľ–ĺ–∂–Ĺ–į —ā–ĺ–Ľ—Ć–ļ–ĺ –Ņ–ĺ—ā–ĺ–ľ—É, —á—ā–ĺ –Ņ—Ä–ł–∑–Ĺ–į–ļ–ĺ–ľ —ā–ĺ–≥–ĺ –ł–Ľ–ł –ł–Ĺ–ĺ–≥–ĺ –£–° —Ā–Ľ—É–∂–ł—ā –∑–Ĺ–į—á–Ķ–Ĺ–ł–Ķ

—Ā—ā–į—Ä—ą–Ķ–≥–ĺ –Ī–ł—ā–į —Ā–Ľ–ĺ–≤ D7. –Ę–į–ļ–ł–ľ –ĺ–Ī—Ä–į–∑–ĺ–ľ, —ć—ā–ĺ—ā –Ī–ł—ā –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā –ī–ĺ–Ņ–ĺ–Ľ–Ĺ–ł—ā–Ķ–Ľ—Ć–Ĺ—É—é

–į–ī—Ä–Ķ—Ā–į—Ü–ł—é —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł—Ö —Ā–Ľ–ĺ–≤.

–†–į–Ī–ĺ—ā–į –į–ī–į–Ņ—ā–Ķ—Ä–į –Ĺ–į—á–ł–Ĺ–į–Ķ—ā—Ā—Ź –Ņ–ĺ—Ā–Ľ–Ķ –∑–į–≥—Ä—É–∑–ļ–ł —Ā –®–Ē –≤

–†–£–° —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–Ķ–≥–ĺ —Ā–Ľ–ĺ–≤–į –£–°1, –∑–į–ī–į—é—Č–Ķ–≥–ĺ –Ņ–ĺ—Ä—ā–į–ľ –į–ī–į–Ņ—ā–Ķ—Ä–į

–ĺ–ī–ł–Ĺ –ł–∑ —ā—Ä–Ķ—Ö –≤–ĺ–∑–ľ–ĺ–∂–Ĺ—č—Ö —Ä–Ķ–∂–ł–ľ–ĺ–≤ –ł –Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–Ĺ–ĺ—Ā—ā—Ć –Ņ–ĺ—Ä—ā–į (–≤–≤–ĺ–ī –ł–Ľ–ł –≤—č–≤–ĺ–ī).

–í–ĺ–∑–ľ–ĺ–∂–Ĺ—č —ā—Ä–ł —Ä–Ķ–∂–ł–ľ–į —Ä–į–Ī–ĺ—ā—č –Ņ–ĺ—Ä—ā–ĺ–≤: 0, 1 –ł 2, –Ņ—Ä–ł—á–Ķ–ľ –Ņ–ĺ—Ä—ā –ź

–ľ–ĺ–∂–Ķ—ā —Ä–į–Ī–ĺ—ā–į—ā—Ć –≤ –Ľ—é–Ī–ĺ–ľ –ł–∑ —ā—Ä–Ķ—Ö —Ä–Ķ–∂–ł–ľ–ĺ–≤, –Ņ–ĺ—Ä—ā –í —ā–ĺ–Ľ—Ć–ļ–ĺ –≤ –ī–≤—É—Ö (0 –ł 1), –į —Ä–Ķ–∂–ł–ľ

–Ņ–ĺ—Ä—ā–į –° –∑–į–≤–ł—Ā–ł—ā –ĺ—ā —Ä–Ķ–∂–ł–ľ–ĺ–≤ –Ņ–ĺ—Ä—ā–ĺ–≤ –ź –ł –í.

–ü–ĺ—Ä—ā –°

–ł–ľ–Ķ–Ķ—ā –ĺ—Ā–ĺ–Ī–Ķ–Ĺ–Ĺ–ĺ—Ā—ā–ł, –≤ –ĺ—ā–Ľ–ł—á–ł–Ķ –ĺ—ā –Ņ–ĺ—Ä—ā–ĺ–≤ –ź –ł –í, –ļ–ĺ—ā–ĺ—Ä—č–Ķ –ĺ–Ņ–Ķ—Ä–ł—Ä—É—é—ā —Ā–ĺ —Ā–Ľ–ĺ–≤–į–ľ–ł –≤

—Ü–Ķ–Ľ–ĺ–ľ, —Ä–į–∑—Ä—Ź–ī—č –Ņ–ĺ—Ä—ā–į –° –ľ–ĺ–≥—É—ā –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä–ĺ–≤–į—ā—Ć—Ā—Ź –ł –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į—ā—Ć—Ā—Ź –Ņ–ĺ–ĺ–ī–ł–Ĺ–ĺ—á–ļ–Ķ. –í

—á–į—Ā—ā–Ĺ–ĺ—Ā—ā–ł, –Ľ—é–Ī–ĺ–Ļ –ł–∑ –≤–ĺ—Ā—Ć–ľ–ł —Ä–į–∑—Ä—Ź–ī–ĺ–≤ –Ņ–ĺ—Ä—ā–į –° –ľ–ĺ–∂–Ķ—ā –Ī—č—ā—Ć

—É—Ā—ā–į–Ĺ–ĺ–≤–Ľ–Ķ–Ĺ –ł–Ľ–ł —Ā–Ī—Ä–ĺ—ą–Ķ–Ĺ –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–Ĺ—č–ľ —Ā–Ņ–ĺ—Ā–ĺ–Ī–ĺ–ľ. –≠—ā–ĺ –Ĺ—É–∂–Ĺ–ĺ –ī–Ľ—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤

–ļ–≤–ł—ā–ł—Ä–ĺ–≤–į–Ĺ–ł—Ź –Ņ—Ä–ł –ĺ–Ī–ľ–Ķ–Ĺ–Ķ —á–Ķ—Ä–Ķ–∑ –Ņ–ĺ—Ä—ā—č –ź –ł –í –≤ —Ä–Ķ–∂–ł–ľ–į—Ö 1 –ł 2. –ü—Ä–ł —Ä–į–Ī–ĺ—ā–Ķ –Ņ–ĺ—Ä—ā–į –≤ —Ä–Ķ–∂–ł–ľ–Ķ 1 –ī–Ľ—Ź –Ĺ–Ķ–≥–ĺ

—ā—Ä–Ķ–Ī—É—é—ā—Ā—Ź —ā—Ä–ł –Ľ–ł–Ĺ–ł–ł –Ņ–ĺ–ī —Ā–ł–≥–Ĺ–į–Ľ—č —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź, –≤ —Ä–Ķ–∂–ł–ľ–Ķ 2 - –Ņ—Ź—ā—Ć.

–†–Ķ–∂–ł–ľ—č —Ä–į–Ī–ĺ—ā—č –Ņ–ĺ—Ä—ā–ĺ–≤:

- —Ä–Ķ–∂–ł–ľ 0 -

–ĺ–ī–Ĺ–ĺ–Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–Ĺ—č–Ļ –≤–≤–ĺ–ī/–≤—č–≤–ĺ–ī –Ī–Ķ–∑ –ļ–≤–ł—ā–ł—Ä–ĺ–≤–į–Ĺ–ł—Ź, –≤ —ć—ā–ĺ–ľ —Ä–Ķ–∂–ł–ľ–Ķ –ľ–ĺ–≥—É—ā —Ä–į–Ī–ĺ—ā–į—ā—Ć

–Ņ–ĺ—Ä—ā—č –ź –ł –í, –į —ā–į–ļ–∂–Ķ —Ā–≤–ĺ–Ī–ĺ–ī–Ĺ—č–Ķ (–Ĺ–Ķ –∑–į–Ĺ—Ź—ā—č–Ķ –Ņ–Ķ—Ä–Ķ–ī–į—á–Ķ–Ļ

—Ā–Ľ—É–∂–Ķ–Ī–Ĺ—č—Ö —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ –ī–Ľ—Ź –Ņ–ĺ—Ä—ā–ĺ–≤ –ź –ł –í) –Ľ–ł–Ĺ–ł–ł –Ņ–ĺ—Ä—ā–į –°;

–Ę–į–Ī–Ľ–ł—Ü–į 1

|

–ź1 |

–ź0 |

|

|

|

–ě–Ņ–Ķ—Ä–į—Ü–ł—Ź

|

|

0 |

0 |

0 |

1 |

0 |

–ü–ĺ—Ä—ā –ź -> –®–Ē |

|

0 |

1 |

0 |

1 |

0 |

–ü–ĺ—Ä—ā –í -> –®–Ē |

|

1 |

0 |

0 |

1 |

0 |

–ü–ĺ—Ä—ā –° -> –®–Ē |

|

1 |

1 |

0 |

1 |

0 |

–ó–į–Ņ—Ä–Ķ—Č–Ķ–Ĺ–Ĺ–į—Ź

–ļ–ĺ–ľ–Ī–ł–Ĺ–į—Ü–ł—Ź |

|

0 |

0 |

1 |

0 |

0 |

–®–Ē -> –ü–ĺ—Ä—ā –ź |

|

0 |

1 |

1 |

0 |

0 |

–®–Ē -> –ü–ĺ—Ä—ā –í |

|

1 |

0 |

1 |

0 |

0 |

–®–Ē -> –ü–ĺ—Ä—ā –° |

|

1 |

1 |

1 |

0 |

0 |

–®–Ē -> –†–£–° –Ņ—Ä–ł

D7 = 1 |

|

|

|

|

|

|

–®–Ē -> BSR –Ņ—Ä–ł D7 = 0 |

|

X |

X |

1 |

1 |

0 |

–®–ł–Ĺ—č –ĺ—ā–ļ–Ľ—é—á–Ķ–Ĺ—č |

|

X |

X |

X |

X |

1 |

–®–ł–Ĺ—č –ĺ—ā–ļ–Ľ—é—á–Ķ–Ĺ—č |

- —Ä–Ķ–∂–ł–ľ 1 - –ĺ–ī–Ĺ–ĺ–Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–Ĺ—č–Ļ –≤–≤–ĺ–ī/–≤—č–≤–ĺ–ī —Ā –ļ–≤–ł—ā–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ–ľ;

- —Ä–Ķ–∂–ł–ľ 2 - –ī–≤—É–Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–Ĺ—č–Ļ –≤–≤–ĺ–ī/–≤—č–≤–ĺ–ī —Ā –ļ–≤–ł—ā–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ–ľ.

–ö–≤–ł—ā–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ, –ļ–į–ļ –ł–∑–≤–Ķ—Ā—ā–Ĺ–ĺ,

–Ņ–ĺ–∑–≤–ĺ–Ľ—Ź–Ķ—ā –≤–Ķ—Ā—ā–ł –į—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ—č–Ļ –ĺ–Ī–ľ–Ķ–Ĺ —Ā —É—á–Ķ—ā–ĺ–ľ –≥–ĺ—ā–ĺ–≤–Ĺ–ĺ—Ā—ā–ł –į–Ī–ĺ–Ĺ–Ķ–Ĺ—ā–į –ļ –Ņ–Ķ—Ä–Ķ–ī–į—á–Ķ, —ā.–Ķ.

–ł–ľ–Ķ—ā—Ć –Ņ–Ķ—Ä–Ķ–ľ–Ķ–Ĺ–Ĺ—č–Ļ —ā–Ķ–ľ–Ņ –ĺ–Ī–ľ–Ķ–Ĺ–į —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ –≤–ĺ–∑–ľ–ĺ–∂–Ĺ–ĺ—Ā—ā—Ź–ľ –≤–Ĺ–Ķ—ą–Ĺ–Ķ–≥–ĺ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į.

–†–ł—Ā. –§–ĺ—Ä–ľ–į—ā—č —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł—Ö —Ā–Ľ–ĺ–≤ –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ–ĺ–≥–ĺ –Ņ–Ķ—Ä–ł—Ą–Ķ—Ä–ł–Ļ–Ĺ–ĺ–≥–ĺ –į–ī–į–Ņ—ā–Ķ—Ä–į

–†–Ķ–∂–ł–ľ 0

–í —Ä–Ķ–∂–ł–ľ–Ķ 0 –ĺ—Ā—É—Č–Ķ—Ā—ā–≤–Ľ—Ź–Ķ—ā—Ā—Ź

–Ņ—Ä—Ź–ľ–ĺ–Ļ –ĺ–ī–Ĺ–ĺ–Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–Ĺ—č–Ļ –≤–≤–ĺ–ī-–≤—č–≤–ĺ–ī –ī–į–Ĺ–Ĺ—č—Ö –Ī–Ķ–∑ —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ –ł—Ö —Ā–ĺ–Ņ—Ä–ĺ–≤–ĺ–∂–ī–Ķ–Ĺ–ł—Ź. –ö–į–∂–ī—č–Ļ

–ł–∑ 4-—Ö –Ņ–ĺ—Ä—ā–ĺ–≤ –ľ–ĺ–∂–Ķ—ā –Ī—č—ā—Ć –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ –ī–Ľ—Ź –≤–≤–ĺ–ī–į –ł–Ľ–ł –≤—č–≤–ĺ–ī–į –Ĺ–Ķ–∑–į–≤–ł—Ā–ł–ľ–ĺ –ĺ—ā –ī—Ä—É–≥–ł—Ö,

—ā–į–ļ —á—ā–ĺ –≤–ĺ–∑–ľ–ĺ–∂–Ĺ—č 16 –≤–į—Ä–ł–į–Ĺ—ā–ĺ–≤ —Ä–Ķ–∂–ł–ľ–į 0. –ü—Ä–ł –≤–≤–ĺ–ī–Ķ

–Ņ–ĺ—Ā—ā—É–Ņ–į—é—Č–į—Ź –ł–∑ –í–£ –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł—Ź –į–ī–į–Ņ—ā–Ķ—Ä–ĺ–ľ –Ĺ–Ķ —Ą–ł–ļ—Ā–ł—Ä—É–Ķ—ā—Ā—Ź –ł –ī–ĺ–Ľ–∂–Ĺ–į –Ņ—Ä–ł—Ā—É—ā—Ā—ā–≤–ĺ–≤–į—ā—Ć

–Ĺ–į –Ķ–≥–ĺ –≤—Ö–ĺ–ī–Ķ –≤–ĺ –≤—Ä–Ķ–ľ—Ź –ī–Ķ–Ļ—Ā—ā–≤–ł—Ź —Ā–ł–≥–Ĺ–į–Ľ–į —á—ā–Ķ–Ĺ–ł—Ź. –ü—Ä–ł –≤—č–≤–ĺ–ī–Ķ –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł—Ź –ĺ—ā –ú–ü

—Ą–ł–ļ—Ā–ł—Ä—É–Ķ—ā—Ā—Ź –≤ –Ī—É—Ą–Ķ—Ä–Ĺ–ĺ–ľ —Ä–Ķ–≥–ł—Ā—ā—Ä–Ķ –Ņ–ĺ—Ä—ā–į –Ņ–ĺ –∑–į–ī–Ĺ–Ķ–ľ—É —Ą—Ä–ĺ–Ĺ—ā—É —Ā–ł–≥–Ĺ–į–Ľ–į –∑–į–Ņ–ł—Ā–ł –ł

—Ā–ĺ—Ö—Ä–į–Ĺ—Ź–Ķ—ā—Ā—Ź –ī–ĺ –Ĺ–ĺ–≤–ĺ–≥–ĺ —Ü–ł–ļ–Ľ–į –≤—č–≤–ĺ–ī–į –ł–Ľ–ł —Ā–ľ–Ķ–Ĺ—č —Ä–Ķ–∂–ł–ľ–į —Ä–į–Ī–ĺ—ā—č –Ņ–ĺ—Ä—ā–į. –ü—Ä–ł –≤–≤–ĺ–ī–Ķ

–ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł—Ź –≤—č–ī–į–Ķ—ā—Ā—Ź –Ĺ–į –®–Ē –Ņ—Ä–ł –≤—č–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł–ł –ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ –ļ–ĺ–ľ–į–Ĺ–ī—č IN port, –Ņ—Ä–ł –≤—č–≤–ĺ–ī–Ķ -

–Ņ—Ä–ł –≤—č–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł–ł –ļ–ĺ–ľ–į–Ĺ–ī—č OUT port.

–Ę–į–ļ–ĺ–Ļ –≤–į—Ä–ł–į–Ĺ—ā —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É–Ķ—ā

—Ä–į–Ī–ĺ—ā–Ķ "—Ā —Ä–į–∑–ī–Ķ–Ľ—Ć–Ĺ–ĺ–Ļ —ą–ł–Ĺ–ĺ–Ļ", –Ņ—Ä–ł –ļ–ĺ—ā–ĺ—Ä–ĺ–Ļ –≤–Ĺ–Ķ—ą–Ĺ–ł–ľ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į–ľ

–Ņ—Ä–ł–Ĺ–į–ī–Ľ–Ķ–∂–ł—ā –ĺ—ā–ī–Ķ–Ľ—Ć–Ĺ–ĺ–Ķ –į–ī—Ä–Ķ—Ā–Ĺ–ĺ–Ķ –Ņ—Ä–ĺ—Ā—ā—Ä–į–Ĺ—Ā—ā–≤–ĺ. –Ě–Ķ –ł—Ā–ļ–Ľ—é—á–į–Ķ—ā—Ā—Ź –ł –ĺ—Ä–≥–į–Ĺ–ł–∑–į—Ü–ł—Ź

–ĺ–Ī—Ä–į—Č–Ķ–Ĺ–ł—Ź –ļ –Ņ–ĺ—Ä—ā–į–ľ, –ļ–į–ļ –ļ —Ź—á–Ķ–Ļ–ļ–į–ľ –Ņ–į–ľ—Ź—ā–ł (–ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā "—Ā –ĺ–Ī—Č–Ķ–Ļ —ą–ł–Ĺ–ĺ–Ļ").

–†–Ķ–∂–ł–ľ 1

–í —Ä–Ķ–∂–ł–ľ–Ķ 1 –ļ–į–∂–ī–į—Ź –ł–∑ –ī–≤—É—Ö

12-—Ä–į–∑—Ä—Ź–ī–Ĺ—č—Ö –≥—Ä—É–Ņ–Ņ (–ź –ł –í) –ľ–ĺ–∂–Ķ—ā –Ī—č—ā—Ć –∑–į–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä–ĺ–≤–į–Ĺ–į –Ĺ–į –ĺ–ī–Ĺ–ĺ–Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–Ĺ—č–Ļ

–≤–≤–ĺ–ī –ł–Ľ–ł –≤—č–≤–ĺ–ī —Ā –ļ–≤–ł—ā–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ–ľ. –ü—Ä–ł —ć—ā–ĺ–ľ –≤—Ö–ĺ–ī–Ĺ—č–Ķ –ł –≤—č—Ö–ĺ–ī–Ĺ—č–Ķ –ī–į–Ĺ–Ĺ—č–Ķ —Ą–ł–ļ—Ā–ł—Ä—É—é—ā—Ā—Ź

–į–ī–į–Ņ—ā–Ķ—Ä–ĺ–ľ. –ü–ĺ –Ľ–ł–Ĺ–ł—Ź–ľ –Ņ–ĺ—Ä—ā–ĺ–≤ –°–Ĺ –ł CL –Ņ–Ķ—Ä–Ķ–ī–į—é—ā—Ā—Ź —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł–Ķ —Ā–ł–≥–Ĺ–į–Ľ—č. –†–į–∑–ī–Ķ–Ľ—Ć–Ĺ–į—Ź —É—Ā—ā–į–Ĺ–ĺ–≤–ļ–į

—Ä–į–∑—Ä—Ź–ī–ĺ–≤ –Ņ–ĺ—Ä—ā–į –° –Ņ–ĺ–∑–≤–ĺ–Ľ—Ź–Ķ—ā –Ķ–ľ—É –ł–≥—Ä–į—ā—Ć —Ä–ĺ–Ľ—Ć —Ā—Ö–Ķ–ľ—č

—É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –Ņ—Ä–ĺ—Ü–Ķ–ī—É—Ä–į–ľ–ł –≤–≤–ĺ–ī–į-–≤—č–≤–ĺ–ī–į, –Ņ—Ä–ł—á–Ķ–ľ –Ī–ł—ā–į–ľ –Ņ–ĺ—Ä—ā–į –Ņ—Ä–ł–ī–į–Ķ—ā—Ā—Ź –ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ–Ķ–Ĺ–Ĺ–ĺ–Ķ

—Ą—É–Ĺ–ļ—Ü–ł–ĺ–Ĺ–į–Ľ—Ć–Ĺ–ĺ–Ķ –Ĺ–į–∑–Ĺ–į—á–Ķ–Ĺ–ł–Ķ.

–†–Ķ–∂–ł–ľ 1 —Ä–į—Ā—Ā–ľ–ĺ—ā—Ä–ł–ľ –≤ –Ņ–ĺ–Ľ–Ĺ–ĺ–ľ

–ĺ–Ī—ä–Ķ–ľ–Ķ, —ā. –ļ. –ĺ–Ĺ —Ö–ĺ—Ä–ĺ—ą–ĺ –ł–Ľ–Ľ—é—Ā—ā—Ä–ł—Ä—É–Ķ—ā –Ņ—Ä–ł–Ĺ—Ü–ł–Ņ—č —Ä–į–Ī–ĺ—ā—č –į–ī–į–Ņ—ā–Ķ—Ä–į. –ü—Ä–ł –≤–≤–ĺ–ī–Ķ

–ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É—é—ā—Ā—Ź —Ā–Ľ–Ķ–ī—É—é—Č–ł–Ķ —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł–Ķ —Ā–ł–≥–Ĺ–į–Ľ—č:

-

![]() ¬†- —Ā—ā—Ä–ĺ–Ī –∑–į–≥—Ä—É–∑–ļ–ł –ī–į–Ĺ–Ĺ—č—Ö –≤ —Ä–Ķ–≥–ł—Ā—ā—Ä (–Ņ–ĺ –∑–į–ī–Ĺ–Ķ–ľ—É

—Ą—Ä–ĺ–Ĺ—ā—É);

¬†- —Ā—ā—Ä–ĺ–Ī –∑–į–≥—Ä—É–∑–ļ–ł –ī–į–Ĺ–Ĺ—č—Ö –≤ —Ä–Ķ–≥–ł—Ā—ā—Ä (–Ņ–ĺ –∑–į–ī–Ĺ–Ķ–ľ—É

—Ą—Ä–ĺ–Ĺ—ā—É);

-

IBF (Input Buffer Full) - –≤—Ö–ĺ–ī–Ĺ–ĺ–Ļ –Ī—É—Ą–Ķ—Ä –Ņ–ĺ–Ľ–ĺ–Ĺ, —Ā–ł–≥–Ĺ–į–Ľ –Ņ–ĺ–ī—ā–≤–Ķ—Ä–∂–ī–Ķ–Ĺ–ł—Ź –∑–į–≥—Ä—É–∑–ļ–ł

–ī–į–Ĺ–Ĺ—č—Ö;

-

INT - –∑–į–Ņ—Ä–ĺ—Ā –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź.

–ė–ľ–Ķ—Ź –ī–į–Ĺ–Ĺ—č–Ķ –ī–Ľ—Ź –≤–≤–ĺ–ī–į –≤ –Ņ–ĺ—Ä—ā,

–í–£ –Ņ—Ä–ł —É—Ā–Ľ–ĺ–≤–ł–ł IBF = 0 –≤—č—Ä–į–Ī–į—ā—č–≤–į–Ķ—ā —Ā–ł–≥–Ĺ–į–Ľ –≥–ĺ—ā–ĺ–≤–Ĺ–ĺ—Ā—ā–ł

–ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł ![]() . –ü–Ķ—Ä–Ķ–ī–Ĺ–ł–Ļ —Ą—Ä–ĺ–Ĺ—ā —ć—ā–ĺ–≥–ĺ

—Ā–ł–≥–Ĺ–į–Ľ–į —É—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā —Ā–ł–≥–Ĺ–į–Ľ IBF, –∑–į–Ņ—Ä–Ķ—Č–į—é—Č–ł–Ļ

–≤–Ĺ–Ķ—ą–Ĺ–Ķ–ľ—É —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤—É –≤–≤–ĺ–ī —Ā–Ľ–Ķ–ī—É—é—Č–Ķ–≥–ĺ —Ā–Ľ–ĺ–≤–į –ī–ĺ –ĺ—Ā–≤–ĺ–Ī–ĺ–∂–ī–Ķ–Ĺ–ł—Ź –į–ī–į–Ņ—ā–Ķ—Ä–į (—ā–ĺ–≥–ĺ –Ņ–ĺ—Ä—ā–į,

–ļ–ĺ—ā–ĺ—Ä—č–Ļ –ł–ľ–Ķ–Ķ—ā—Ā—Ź –≤ –≤–ł–ī—É). –ö –ľ–ĺ–ľ–Ķ–Ĺ—ā—É –ĺ–ļ–ĺ–Ĺ—á–į–Ĺ–ł—Ź

. –ü–Ķ—Ä–Ķ–ī–Ĺ–ł–Ļ —Ą—Ä–ĺ–Ĺ—ā —ć—ā–ĺ–≥–ĺ

—Ā–ł–≥–Ĺ–į–Ľ–į —É—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā —Ā–ł–≥–Ĺ–į–Ľ IBF, –∑–į–Ņ—Ä–Ķ—Č–į—é—Č–ł–Ļ

–≤–Ĺ–Ķ—ą–Ĺ–Ķ–ľ—É —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤—É –≤–≤–ĺ–ī —Ā–Ľ–Ķ–ī—É—é—Č–Ķ–≥–ĺ —Ā–Ľ–ĺ–≤–į –ī–ĺ –ĺ—Ā–≤–ĺ–Ī–ĺ–∂–ī–Ķ–Ĺ–ł—Ź –į–ī–į–Ņ—ā–Ķ—Ä–į (—ā–ĺ–≥–ĺ –Ņ–ĺ—Ä—ā–į,

–ļ–ĺ—ā–ĺ—Ä—č–Ļ –ł–ľ–Ķ–Ķ—ā—Ā—Ź –≤ –≤–ł–ī—É). –ö –ľ–ĺ–ľ–Ķ–Ĺ—ā—É –ĺ–ļ–ĺ–Ĺ—á–į–Ĺ–ł—Ź ![]() ¬†–ī–į–Ĺ–Ĺ—č–Ķ –≤–≤–Ķ–ī–Ķ–Ĺ—č –≤ –Ī—É—Ą–Ķ—Ä –Ņ–ĺ—Ä—ā–į, –ł, –Ķ—Ā–Ľ–ł

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ—č (–≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–ł–Ļ —ā—Ä–ł–≥–≥–Ķ—Ä —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ–ł—Ź –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ INTE —É—Ā—ā–į–Ĺ–ĺ–≤–Ľ–Ķ–Ĺ –ļ–ĺ–ľ–į–Ĺ–ī–ĺ–Ļ –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—č), —ā–ĺ –į–ī–į–Ņ—ā–Ķ—Ä —Ą–ĺ—Ä–ľ–ł—Ä—É–Ķ—ā

–∑–į–Ņ—Ä–ĺ—Ā –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź INT –ī–Ľ—Ź –ú–ü, –Ņ–Ķ—Ä–Ķ—Ö–ĺ–ī—Ź—Č–Ķ–≥–ĺ –ļ –Ņ–ĺ–ī–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–Ķ

–ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź, —Ā–ĺ–ī–Ķ—Ä–∂–į—Č–Ķ–Ļ –ļ–ĺ–ľ–į–Ĺ–ī—É IN port. –ü—Ä–ł —ć—ā–ĺ–ľ –Ĺ–į –į–ī–į–Ņ—ā–Ķ—Ä –Ņ–ĺ—Ā—ā—É–Ņ–į—é—ā —Ā–ł–≥–Ĺ–į–Ľ—č –į–ī—Ä–Ķ—Ā–į—Ü–ł–ł

–ł

¬†–ī–į–Ĺ–Ĺ—č–Ķ –≤–≤–Ķ–ī–Ķ–Ĺ—č –≤ –Ī—É—Ą–Ķ—Ä –Ņ–ĺ—Ä—ā–į, –ł, –Ķ—Ā–Ľ–ł

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ—č (–≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–ł–Ļ —ā—Ä–ł–≥–≥–Ķ—Ä —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ–ł—Ź –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ INTE —É—Ā—ā–į–Ĺ–ĺ–≤–Ľ–Ķ–Ĺ –ļ–ĺ–ľ–į–Ĺ–ī–ĺ–Ļ –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—č), —ā–ĺ –į–ī–į–Ņ—ā–Ķ—Ä —Ą–ĺ—Ä–ľ–ł—Ä—É–Ķ—ā

–∑–į–Ņ—Ä–ĺ—Ā –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź INT –ī–Ľ—Ź –ú–ü, –Ņ–Ķ—Ä–Ķ—Ö–ĺ–ī—Ź—Č–Ķ–≥–ĺ –ļ –Ņ–ĺ–ī–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–Ķ

–ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź, —Ā–ĺ–ī–Ķ—Ä–∂–į—Č–Ķ–Ļ –ļ–ĺ–ľ–į–Ĺ–ī—É IN port. –ü—Ä–ł —ć—ā–ĺ–ľ –Ĺ–į –į–ī–į–Ņ—ā–Ķ—Ä –Ņ–ĺ—Ā—ā—É–Ņ–į—é—ā —Ā–ł–≥–Ĺ–į–Ľ—č –į–ī—Ä–Ķ—Ā–į—Ü–ł–ł

–ł ![]() . –ü–Ķ—Ä–Ķ–ī–Ĺ–ł–Ļ —Ą—Ä–ĺ–Ĺ—ā

. –ü–Ķ—Ä–Ķ–ī–Ĺ–ł–Ļ —Ą—Ä–ĺ–Ĺ—ā ![]() ¬†–ĺ—ā–ľ–Ķ—á–į–Ķ—ā –Ĺ–į—á–į–Ľ–ĺ —Ā—á–ł—ā—č–≤–į–Ĺ–ł—Ź —Ā–Ľ–ĺ–≤–į

–ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ –ł —Ā–Ĺ–ł–ľ–į–Ķ—ā –∑–į–Ņ—Ä–ĺ—Ā –Ĺ–į –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ķ INT.

–ü–ĺ–ļ–į –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź –Ĺ–Ķ —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ—č, –ĺ—Ā—É—Č–Ķ—Ā—ā–≤–Ľ—Ź–Ķ—ā—Ā—Ź —Ö—Ä–į–Ĺ–Ķ–Ĺ–ł–Ķ –ī–į–Ĺ–Ĺ—č—Ö –≤ –į–ī–į–Ņ—ā–Ķ—Ä–Ķ. –ó–į–ī–Ĺ–ł–Ļ

—Ą—Ä–ĺ–Ĺ—ā

¬†–ĺ—ā–ľ–Ķ—á–į–Ķ—ā –Ĺ–į—á–į–Ľ–ĺ —Ā—á–ł—ā—č–≤–į–Ĺ–ł—Ź —Ā–Ľ–ĺ–≤–į

–ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ –ł —Ā–Ĺ–ł–ľ–į–Ķ—ā –∑–į–Ņ—Ä–ĺ—Ā –Ĺ–į –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ķ INT.

–ü–ĺ–ļ–į –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź –Ĺ–Ķ —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ—č, –ĺ—Ā—É—Č–Ķ—Ā—ā–≤–Ľ—Ź–Ķ—ā—Ā—Ź —Ö—Ä–į–Ĺ–Ķ–Ĺ–ł–Ķ –ī–į–Ĺ–Ĺ—č—Ö –≤ –į–ī–į–Ņ—ā–Ķ—Ä–Ķ. –ó–į–ī–Ĺ–ł–Ļ

—Ą—Ä–ĺ–Ĺ—ā ![]() ¬†–ĺ—ā–ľ–Ķ—á–į–Ķ—ā –∑–į–≤–Ķ—Ä—ą–Ķ–Ĺ–ł–Ķ —Ā—á–ł—ā—č–≤–į–Ĺ–ł—Ź —Ā–Ľ–ĺ–≤–į

–ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ –ł —Ā–Ĺ–ł–ľ–į–Ķ—ā —Ā–ł–≥–Ĺ–į–Ľ IBF, –ī–ĺ–Ņ—É—Ā–ļ–į—Ź –Ĺ–ĺ–≤—É—é

–∑–į–Ņ–ł—Ā—Ć —Ā–Ľ–ĺ–≤–į —Ā–ĺ —Ā—ā–ĺ—Ä–ĺ–Ĺ—č –í–£.

¬†–ĺ—ā–ľ–Ķ—á–į–Ķ—ā –∑–į–≤–Ķ—Ä—ą–Ķ–Ĺ–ł–Ķ —Ā—á–ł—ā—č–≤–į–Ĺ–ł—Ź —Ā–Ľ–ĺ–≤–į

–ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ –ł —Ā–Ĺ–ł–ľ–į–Ķ—ā —Ā–ł–≥–Ĺ–į–Ľ IBF, –ī–ĺ–Ņ—É—Ā–ļ–į—Ź –Ĺ–ĺ–≤—É—é

–∑–į–Ņ–ł—Ā—Ć —Ā–Ľ–ĺ–≤–į —Ā–ĺ —Ā—ā–ĺ—Ä–ĺ–Ĺ—č –í–£.

–ü—Ä–ł –≤—č–≤–ĺ–ī–Ķ –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É—é—ā—Ā—Ź

—Ā–Ľ–Ķ–ī—É—é—Č–ł–Ķ —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł–Ķ —Ā–ł–≥–Ĺ–į–Ľ—č:

- ![]() ¬†(Output Buffer Full) ‚ÄĒ –≤—č—Ö–ĺ–ī–Ĺ–ĺ–Ļ

–Ī—É—Ą–Ķ—Ä –Ņ–ĺ–Ľ–ĺ–Ĺ, —Ā—ā—Ä–ĺ–Ī –≤—č–≤–ĺ–ī–į –Ĺ–ĺ–≤—č—Ö –ī–į–Ĺ–Ĺ—č—Ö;

¬†(Output Buffer Full) ‚ÄĒ –≤—č—Ö–ĺ–ī–Ĺ–ĺ–Ļ

–Ī—É—Ą–Ķ—Ä –Ņ–ĺ–Ľ–ĺ–Ĺ, —Ā—ā—Ä–ĺ–Ī –≤—č–≤–ĺ–ī–į –Ĺ–ĺ–≤—č—Ö –ī–į–Ĺ–Ĺ—č—Ö;

- ![]() ¬†(Acknowledge) ‚ÄĒ

–Ņ–ĺ–ī—ā–≤–Ķ—Ä–∂–ī–Ķ–Ĺ–ł–Ķ –Ņ—Ä–ł—Ď–ľ–į –≤–Ĺ–Ķ—ą–Ĺ–ł–ľ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–ĺ–ľ;

¬†(Acknowledge) ‚ÄĒ

–Ņ–ĺ–ī—ā–≤–Ķ—Ä–∂–ī–Ķ–Ĺ–ł–Ķ –Ņ—Ä–ł—Ď–ľ–į –≤–Ĺ–Ķ—ą–Ĺ–ł–ľ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–ĺ–ľ;

- INT ‚ÄĒ –∑–į–Ņ—Ä–ĺ—Ā –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź.

–ü—Ä–ł –≤—č–≤–ĺ–ī–Ķ –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā—Ā—Ź –ļ–ĺ–ľ–į–Ĺ–ī–į

OUT port, –ł –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä

—É—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā –į–ī—Ä–Ķ—Ā –Ņ–ĺ—Ä—ā–į –ł –ī–į–Ĺ–Ĺ—č–Ķ –Ĺ–į –®–Ē. –ü—Ä–ł —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ–Ĺ—č—Ö –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź—Ö –ī–į–Ľ–Ķ–Ķ

–≤—č—Ä–į–Ī–į—ā—č–≤–į–Ķ—ā—Ā—Ź —Ā–ł–≥–Ĺ–į–Ľ ![]() , –∑–į–≥—Ä—É–∂–į—é—Č–ł–Ļ –ī–į–Ĺ–Ĺ—č–Ķ —Ā –®–Ē –≤

–Ī—É—Ą–Ķ—Ä –į–ī–į–Ņ—ā–Ķ—Ä–į –ł —Ā–Ī—Ä–į—Ā—č–≤–į—é—Č–ł–Ļ –∑–į–Ņ—Ä–ĺ—Ā –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź INT.

–ü–ĺ—Ā–Ľ–Ķ –ĺ–ļ–ĺ–Ĺ—á–į–Ĺ–ł—Ź –∑–į–Ņ–ł—Ā–ł –≤ –į–ī–į–Ņ—ā–Ķ—Ä —Ą–ĺ—Ä–ľ–ł—Ä—É–Ķ—ā—Ā—Ź —Ā–ł–≥–Ĺ–į–Ľ

, –∑–į–≥—Ä—É–∂–į—é—Č–ł–Ļ –ī–į–Ĺ–Ĺ—č–Ķ —Ā –®–Ē –≤

–Ī—É—Ą–Ķ—Ä –į–ī–į–Ņ—ā–Ķ—Ä–į –ł —Ā–Ī—Ä–į—Ā—č–≤–į—é—Č–ł–Ļ –∑–į–Ņ—Ä–ĺ—Ā –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź INT.

–ü–ĺ—Ā–Ľ–Ķ –ĺ–ļ–ĺ–Ĺ—á–į–Ĺ–ł—Ź –∑–į–Ņ–ł—Ā–ł –≤ –į–ī–į–Ņ—ā–Ķ—Ä —Ą–ĺ—Ä–ľ–ł—Ä—É–Ķ—ā—Ā—Ź —Ā–ł–≥–Ĺ–į–Ľ ![]() , —É–ļ–į–∑—č–≤–į—é—Č–ł–Ļ –Ĺ–į –≥–ĺ—ā–ĺ–≤–Ĺ–ĺ—Ā—ā—Ć

–ī–į–Ĺ–Ĺ—č—Ö –ī–Ľ—Ź –í–£. –ü—Ä–ł–Ĺ—Ź–≤ –ī–į–Ĺ–Ĺ—č–Ķ, –í–£ –≤—č–ī–į–Ķ—ā —Ā–ł–≥–Ĺ–į–Ľ –Ņ–ĺ–ī—ā–≤–Ķ—Ä–∂–ī–Ķ–Ĺ–ł—Ź –Ņ—Ä–ł–Ķ–ľ–į

, —É–ļ–į–∑—č–≤–į—é—Č–ł–Ļ –Ĺ–į –≥–ĺ—ā–ĺ–≤–Ĺ–ĺ—Ā—ā—Ć

–ī–į–Ĺ–Ĺ—č—Ö –ī–Ľ—Ź –í–£. –ü—Ä–ł–Ĺ—Ź–≤ –ī–į–Ĺ–Ĺ—č–Ķ, –í–£ –≤—č–ī–į–Ķ—ā —Ā–ł–≥–Ĺ–į–Ľ –Ņ–ĺ–ī—ā–≤–Ķ—Ä–∂–ī–Ķ–Ĺ–ł—Ź –Ņ—Ä–ł–Ķ–ľ–į ![]() , —Ā–Ĺ–ł–ľ–į—é—Č–ł–Ļ OBF, –į –Ņ–ĺ –ĺ–ļ–ĺ–Ĺ—á–į–Ĺ–ł–ł —Ā–ł–≥–Ĺ–į–Ľ–į

, —Ā–Ĺ–ł–ľ–į—é—Č–ł–Ļ OBF, –į –Ņ–ĺ –ĺ–ļ–ĺ–Ĺ—á–į–Ĺ–ł–ł —Ā–ł–≥–Ĺ–į–Ľ–į ![]() ¬†–≤–ĺ—Ā—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā—Ā—Ź –∑–į–Ņ—Ä–ĺ—Ā –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź (–Ķ—Ā–Ľ–ł

—ā—Ä–ł–≥–≥–Ķ—Ä INTE —É—Ā—ā–į–Ĺ–ĺ–≤–Ľ–Ķ–Ĺ), —á—ā–ĺ –≤—č–∑—č–≤–į–Ķ—ā –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł–Ķ —Ā–Ľ–Ķ–ī—É—é—Č–Ķ–≥–ĺ —Ü–ł–ļ–Ľ–į

–≤—č–≤–ĺ–ī–į.

¬†–≤–ĺ—Ā—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā—Ā—Ź –∑–į–Ņ—Ä–ĺ—Ā –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź (–Ķ—Ā–Ľ–ł

—ā—Ä–ł–≥–≥–Ķ—Ä INTE —É—Ā—ā–į–Ĺ–ĺ–≤–Ľ–Ķ–Ĺ), —á—ā–ĺ –≤—č–∑—č–≤–į–Ķ—ā –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł–Ķ —Ā–Ľ–Ķ–ī—É—é—Č–Ķ–≥–ĺ —Ü–ł–ļ–Ľ–į

–≤—č–≤–ĺ–ī–į.

–†–Ķ–∂–ł–ľ 2 –ě—Ā–ĺ–Ī–Ķ–Ĺ–Ĺ–ĺ—Ā—ā–ł —Ą—É–Ĺ–ļ—Ü–ł–ĺ–Ĺ–į–Ľ—Ć–Ĺ–ĺ–Ļ

—Ā—Ö–Ķ–ľ—č –Ņ–ĺ—Ä—ā–į –ź –ī–ĺ–Ņ—É—Ā–ļ–į—é—ā –Ķ–≥–ĺ –Ņ—Ä–ł–ľ–Ķ–Ĺ–Ķ–Ĺ–ł–Ķ –ī–Ľ—Ź

–ī–≤—É–Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–Ĺ–ĺ–Ļ –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –ľ–Ķ–∂–ī—É –®–Ē –ł –í–£. –ü—Ä–ł —ć—ā–ĺ–ľ 5 –Ľ–ł–Ĺ–ł–Ļ –Ņ–ĺ—Ä—ā–į –° –Ņ–Ķ—Ä–Ķ–ī–į—é—ā —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł–Ķ —Ā–ł–≥–Ĺ–į–Ľ—č. –Ē–≤—É–Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–Ĺ—č–Ļ –į—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ—č–Ļ

–ĺ–Ī–ľ–Ķ–Ĺ —á–Ķ—Ä–Ķ–∑ –Ņ–ĺ—Ä—ā –ź –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā—Ā—Ź –ļ–į–ļ –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–ĺ—Ā—ā—Ć

–Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ł—Ö –Ĺ–Ķ–∑–į–≤–ł—Ā–ł–ľ—č—Ö —ć—ā–į–Ņ–ĺ–≤: –∑–į–Ņ–ł—Ā–ł —Ā –®–Ē –≤ –į–ī–į–Ņ—ā–Ķ—Ä, –≤–≤–ĺ–ī–į –≤ –į–ī–į–Ņ—ā–Ķ—Ä –ł–∑ –í–£,

—á—ā–Ķ–Ĺ–ł—Ź –Ĺ–į –®–Ē, –≤—č–≤–ĺ–ī–į –≤ –í–£, –Ĺ–Ķ–ļ–ĺ—ā–ĺ—Ä—č–Ķ –ł–∑ –ļ–ĺ—ā–ĺ—Ä—č—Ö –ľ–ĺ–≥—É—ā —Ā–ĺ–≤–ľ–Ķ—Č–į—ā—Ć—Ā—Ź –≤–ĺ –≤—Ä–Ķ–ľ–Ķ–Ĺ–ł.

–ė—Ā–Ņ–ĺ–Ľ—Ć–∑—É—é—ā—Ā—Ź —Ā–ł–≥–Ĺ–į–Ľ—č —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź: ![]() , IBF,

, IBF, ![]() ,

, ![]() , INT,

—ā. –Ķ. —ā–Ķ –∂–Ķ, —á—ā–ĺ –ł –ī–Ľ—Ź —Ä–Ķ–∂–ł–ľ–į 1.

, INT,

—ā. –Ķ. —ā–Ķ –∂–Ķ, —á—ā–ĺ –ł –ī–Ľ—Ź —Ä–Ķ–∂–ł–ľ–į 1.

–í–≤–ĺ–ī –≤ –į–ī–į–Ņ—ā–Ķ—Ä —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł—Ö

—Ā–Ľ–ĺ–≤ –£–°1 –ł –£–°2 –Ņ—Ä–ĺ–ł–∑–≤–ĺ–ī–ł—ā—Ā—Ź –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–Ĺ—č–ľ —Ā–Ņ–ĺ—Ā–ĺ–Ī–ĺ–ľ —Ā

–Ņ–ĺ–ľ–ĺ—Č—Ć—é –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ–ĺ—Ā—ā–ł –ļ–ĺ–ľ–į–Ĺ–ī –Ĺ–Ķ–Ņ–ĺ—Ā—Ä–Ķ–ī—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ–Ļ –∑–į–≥—Ä—É–∑–ļ–ł –į–ļ–ļ—É–ľ—É–Ľ—Ź—ā–ĺ—Ä–į –ł

–≤—č–≤–ĺ–ī–į –ī–į–Ĺ–Ĺ—č—Ö –≤ –į–ī—Ä–Ķ—Ā–ĺ–≤–į–Ĺ–Ĺ—č–Ļ –Ņ–ĺ—Ä—ā. –Ě–į —Ź–∑—č–ļ–Ķ –į—Ā—Ā–Ķ–ľ–Ī–Ľ–Ķ—Ä–į —Ą—Ä–į–≥–ľ–Ķ–Ĺ—ā –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—č –ł–ľ–Ķ–Ķ—ā

–≤–ł–ī:

MVI A,

b2

OUT port,

–≥–ī–Ķ –∑–į–≥—Ä—É–∂–į–Ķ–ľ—č–Ļ –≤ –į–ļ–ļ—É–ľ—É–Ľ—Ź—ā–ĺ—Ä

–Ī–į–Ļ—ā b2 –Ņ—Ä–Ķ–ī—Ā—ā–į–≤–Ľ—Ź–Ķ—ā —Ā–ĺ–Ī–ĺ—é

–≤–≤–ĺ–ī–ł–ľ–ĺ–Ķ –≤ –į–ī–į–Ņ—ā–Ķ—Ä —Ā–Ľ–ĺ–≤–ĺ –£–°1 –ł–Ľ–ł –£–°2, a port - –į–ī—Ä–Ķ—Ā

—Ä–Ķ–≥–ł—Ā—ā—Ä–ĺ–≤ —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź, —ą–Ķ—Ā—ā—Ć —Ā—ā–į—Ä—ą–ł—Ö —Ä–į–∑—Ä—Ź–ī–ĺ–≤ –ļ–ĺ—ā–ĺ—Ä–ĺ–≥–ĺ –ī–į—é—ā –Ĺ–ĺ–ľ–Ķ—Ä (–į–ī—Ä–Ķ—Ā)

–į–ī–į–Ņ—ā–Ķ—Ä–į, –į –ī–≤–į –ľ–Ľ–į–ī—ą–ł—Ö —Ā–ĺ–ī–Ķ—Ä–∂–į—ā –Ķ–ī–ł–Ĺ–ł—Ü—č. –£–ļ–į–∑–į–Ĺ–Ĺ—č–Ļ —Ą—Ä–į–≥–ľ–Ķ–Ĺ—ā –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—č

–Ņ–ĺ–≤—ā–ĺ—Ä—Ź–Ķ—ā—Ā—Ź —Ā—ā–ĺ–Ľ—Ć–ļ–ĺ —Ä–į–∑, —Ā–ļ–ĺ–Ľ—Ć–ļ–ĺ –Ĺ–Ķ–ĺ–Ī—Ö–ĺ–ī–ł–ľ–ĺ –ī–Ľ—Ź –∑–į–ī–į–Ĺ–ł—Ź –į–ī–į–Ņ—ā–Ķ—Ä—É —Ä–Ķ–∂–ł–ľ–į –ł

—Ą—É–Ĺ–ļ—Ü–ł–Ļ, –į –≤—č—Ö–ĺ–ī–į–ľ –Ņ–ĺ—Ä—ā–į –° –Ĺ—É–∂–Ĺ—č—Ö –∑–Ĺ–į—á–Ķ–Ĺ–ł–Ļ.

–£–Ľ—É—á—ą–Ķ–Ĺ–Ĺ—č–Ļ –≤–į—Ä–ł–į–Ĺ—ā –į–ī–į–Ņ—ā–Ķ—Ä–į

–í–í55–ź –ĺ—ā–Ľ–ł—á–į–Ķ—ā—Ā—Ź –ĺ—ā –Ņ—Ä–Ķ–ī—ą–Ķ—Ā—ā–≤–Ķ–Ĺ–Ĺ–ł–ļ–į –í–í55 —Ä–į–Ī–ĺ—ā–ĺ–Ļ —Ā —Ä–į—Ā—ą–ł—Ä–Ķ–Ĺ–Ĺ—č–ľ —Ā—ā—Ä–ĺ–Ī–ĺ–ľ –∑–į–Ņ–ł—Ā–ł,

—Ā–≤–ĺ–Ļ—Ā—ā–≤–Ķ–Ĺ–Ĺ—č–ľ, –≤ —á–į—Ā—ā–Ĺ–ĺ—Ā—ā–ł, –ł –ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É –ö1821–í–ú85–ź.

–Ē–Ľ—Ź —Ā–≤—Ź–∑–ł —Ā –Ņ–Ķ—Ä–ł—Ą–Ķ—Ä–ł–Ļ–Ĺ—č–ľ–ł

—É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į–ľ–ł, —É–ī–į–Ľ–Ķ–Ĺ–Ĺ—č–ľ–ł –ĺ—ā –ú–ü–° (–Ĺ–į —Ä–į—Ā—Ā—ā–ĺ—Ź–Ĺ–ł–Ķ –Ĺ–Ķ –Ī–ĺ–Ľ–Ķ–Ķ 15–ľ), –Ņ—Ä–ł–ľ–Ķ–Ĺ—Ź–Ķ—ā—Ā—Ź

–ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā –ė–†–ü–† (–ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā —Ä–į–ī–ł–į–Ľ—Ć–Ĺ—č–Ļ –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ—č–Ļ), –ĺ—Ā—É—Č–Ķ—Ā—ā–≤–Ľ—Ź—é—Č–ł–Ļ

–ĺ–ī–Ĺ–ĺ–Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–Ĺ—č–Ķ –į—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ—č–Ķ –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –Ņ–ĺ 8-–ł–Ľ–ł 16-—Ä–į–∑—Ä—Ź–ī–Ĺ–ĺ–Ļ —ą–ł–Ĺ–Ķ (–≤ –Ī–į–∑–ĺ–≤–ĺ–ľ

–≤–į—Ä–ł–į–Ĺ—ā–Ķ). –õ–ĺ–≥–ł—á–Ķ—Ā–ļ–ł–Ķ —ā—Ä–Ķ–Ī–ĺ–≤–į–Ĺ–ł—Ź –ł–Ĺ—ā–Ķ—Ä—Ą–Ķ–Ļ—Ā–į –ė–†–ü–† –ľ–ĺ–≥—É—ā

–Ī—č—ā—Ć –≤—č–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ—č –Ņ—Ä–ł –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–ł–ł –į–ī–į–Ņ—ā–Ķ—Ä–į –í–í55/55–ź.

5. –ü—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä—É–Ķ–ľ—č–Ķ —Ā–≤—Ź–∑–Ĺ—č–Ķ –į–ī–į–Ņ—ā–Ķ—Ä—č

–ü—Ä–ł —É–≤–Ķ–Ľ–ł—á–Ķ–Ĺ–ł–ł —Ä–į—Ā—Ā—ā–ĺ—Ź–Ĺ–ł–Ļ, –Ĺ–į –ļ–ĺ—ā–ĺ—Ä—č–Ķ –Ņ–Ķ—Ä–Ķ–ī–į—é—ā—Ā—Ź

–ī–į–Ĺ–Ĺ—č–Ķ, –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ—č–Ķ —Ā–≤—Ź–∑–ł —Ā—ā–į–Ĺ–ĺ–≤—Ź—ā—Ā—Ź –Ĺ–Ķ–Ņ—Ä–ł–Ķ–ľ–Ľ–Ķ–ľ–ĺ —Ā–Ľ–ĺ–∂–Ĺ—č–ľ–ł –ł –ī–ĺ—Ä–ĺ–≥–ł–ľ–ł. –í —ć—ā–ĺ–ľ

—Ā–Ľ—É—á–į–Ķ –Ņ—Ä–ł–ľ–Ķ–Ĺ—Ź—é—ā –Ņ—Ä–Ķ–ĺ–Ī—Ä–į–∑–ĺ–≤–į–Ĺ–ł–Ķ –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ—č—Ö –ī–į–Ĺ–Ĺ—č—Ö –≤ –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č–Ķ –ī–Ľ—Ź –ł—Ö –Ņ–Ķ—Ä–Ķ–ī–į—á–ł

–Ņ–ĺ –ĺ–ī–Ĺ–ĺ–Ļ —Ā–ł–≥–Ĺ–į–Ľ—Ć–Ĺ–ĺ–Ļ –Ľ–ł–Ĺ–ł–ł. –Ę—Ä–į–ļ—ā –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č—Ö –ī–į–Ĺ–Ĺ—č—Ö –≤ –ĺ–Ī—Č–Ķ–ľ

—Ā–Ľ—É—á–į–Ķ –≤–ļ–Ľ—é—á–į–Ķ—ā –≤ —Ā–Ķ–Ī—Ź –ł—Ā—ā–ĺ—á–Ĺ–ł–ļ –ł –Ņ—Ä–ł–Ķ–ľ–Ĺ–ł–ļ –ī–į–Ĺ–Ĺ—č—Ö, –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä—É–Ķ–ľ—č–Ķ —Ā–≤—Ź–∑–Ĺ—č–Ķ

–į–ī–į–Ņ—ā–Ķ—Ä—č (–ü–°–ź).

–Ě–į —Ä–ł—Ā—É–Ĺ–ļ–Ķ 44 –Ņ–ĺ–ļ–į–∑–į–Ĺ–į

—Ā—ā—Ä—É–ļ—ā—É—Ä–į –ü–°–ź (PCI, Programmable Communication Interface) —ā–ł–Ņ–į 8251–ź —Ą–ł—Ä–ľ—č Intel, –į–Ĺ–į–Ľ–ĺ–≥–ĺ–ľ –ļ–ĺ—ā–ĺ—Ä–ĺ–≥–ĺ —Ź–≤–Ľ—Ź–Ķ—ā—Ā—Ź –ĺ—ā–Ķ—á–Ķ—Ā—ā–≤–Ķ–Ĺ–Ĺ—č–Ļ –ü–°–ź

–ö580–í–í51–ź. –°–ĺ–≥–Ľ–į—Ā–Ĺ–ĺ —ā–ł–Ņ—É —Ä–Ķ–į–Ľ–ł–∑—É–Ķ–ľ—č—Ö –Ņ—Ä–ĺ—ā–ĺ–ļ–ĺ–Ľ–ĺ–≤ —ć—ā–ĺ—ā –ü–°–ź –Ĺ–į–∑—č–≤–į—é—ā —É–Ĺ–ł–≤–Ķ—Ä—Ā–į–Ľ—Ć–Ĺ—č–ľ

—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ–ĺ-–į—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ—č–ľ –Ņ—Ä–ł–Ķ–ľ–ĺ–Ņ–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ–ĺ–ľ (–£–°–ź–ü–ü), —á–Ķ–ľ—É –≤ –į–Ĺ–≥–Ľ–ł–Ļ—Ā–ļ–ĺ–Ļ

—ā–Ķ—Ä–ľ–ł–Ĺ–ĺ–Ľ–ĺ–≥–ł–ł —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É–Ķ—ā USART - Universal Synchronous/Asynchronous Receiver/Transmitter.

–ź–ī–į–Ņ—ā–Ķ—Ä—č, –≤ –ļ–ĺ—ā–ĺ—Ä—č—Ö

—Ä–Ķ–į–Ľ–ł–∑—É—é—ā—Ā—Ź —ā–ĺ–Ľ—Ć–ļ–ĺ –į—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ—č–Ķ –Ņ—Ä–ĺ—ā–ĺ–ļ–ĺ–Ľ—č, –Ĺ–į–∑—č–≤–į—é—ā—Ā—Ź –£–ź–ü–ü (UART - Universal Asynchronous Receiver/Transmitter).

–í –ú–ü–° –į–ī–į–Ņ—ā–Ķ—Ä –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ—ā—Ā—Ź –ļ–į–ļ

–í–£, –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä—É–Ķ—ā—Ā—Ź –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ –ī–Ľ—Ź —Ä–į–Ī–ĺ—ā—č —Ā —Ä–į–∑–Ľ–ł—á–Ĺ–ĺ–Ļ –į–Ņ–Ņ–į—Ä–į—ā—É—Ä–ĺ–Ļ, –Ņ—Ä–ł–Ĺ–ł–ľ–į–Ķ—ā

–ĺ—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į —Ā–ł–ľ–≤–ĺ–Ľ—č –≤ –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ–ĺ–Ļ —Ą–ĺ—Ä–ľ–Ķ –ł –Ņ—Ä–Ķ–ĺ–Ī—Ä–į–∑—É–Ķ—ā –ł—Ö –≤ –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—É—é –ī–Ľ—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –ł–Ľ–ł –Ņ–ĺ–Ľ—É—á–į–Ķ—ā –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č–Ķ

–ī–į–Ĺ–Ĺ—č–Ķ –ł –Ņ—Ä–Ķ–ĺ–Ī—Ä–į–∑—É–Ķ—ā –ł—Ö –≤ –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ—č–Ķ —Ā–ł–ľ–≤–ĺ–Ľ—č –ī–Ľ—Ź –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į. –ö—Ä–ĺ–ľ–Ķ —ā–ĺ–≥–ĺ,

–į–ī–į–Ņ—ā–Ķ—Ä —Ā–ł–≥–Ĺ–į–Ľ–ł–∑–ł—Ä—É–Ķ—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É –ĺ –≥–ĺ—ā–ĺ–≤–Ĺ–ĺ—Ā—ā–ł –Ņ—Ä–ł–Ĺ—Ź—ā—Ć –Ĺ–ĺ–≤—č–Ļ —Ā–ł–ľ–≤–ĺ–Ľ –ī–Ľ—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á–ł

–ł–Ľ–ł –ĺ —ā–ĺ–ľ, —á—ā–ĺ –Ņ–ĺ–Ľ—É—á–ł–Ľ —Ā–ł–ľ–≤–ĺ–Ľ –ī–Ľ—Ź –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į. –í –Ľ—é–Ī–ĺ–Ķ –≤—Ä–Ķ–ľ—Ź –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –ľ–ĺ–∂–Ķ—ā

—á–ł—ā–į—ā—Ć —Ā–Ľ–ĺ–≤–ĺ —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź –į–ī–į–Ņ—ā–Ķ—Ä–į.

–†–ł—Ā. –°—ā—Ä—É–ļ—ā—É—Ä–į –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä—É–Ķ–ľ–ĺ–≥–ĺ

—Ā–≤—Ź–∑–Ĺ–ĺ–≥–ĺ –į–ī–į–Ņ—ā–Ķ—Ä–į

–Ď—É—Ą–Ķ—Ä –®–Ē - –ī–≤—É–Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–Ĺ—č–Ļ,

–≤–ĺ—Ā—Ć–ľ–ł—Ä–į–∑—Ä—Ź–ī–Ĺ—č–Ļ, —Ā —ā—Ä–Ķ–ľ—Ź —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź–ľ–ł. –ě–Ĺ —Ā–≤—Ź–∑—č–≤–į–Ķ—ā –į–ī–į–Ņ—ā–Ķ—Ä —Ā —Ā–ł—Ā—ā–Ķ–ľ–Ĺ–ĺ–Ļ —ą–ł–Ĺ–ĺ–Ļ

–ī–į–Ĺ–Ĺ—č—Ö –ł –Ņ—Ä–ł–Ĺ–ł–ľ–į–Ķ—ā –ī–į–Ĺ–Ĺ—č–Ķ –Ņ–ĺ –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ OUT port, –≤—č–ī–į–Ķ—ā - –Ņ–ĺ –ļ–ĺ–ľ–į–Ĺ–ī–į–ľ IN port. –ß–Ķ—Ä–Ķ–∑ –Ī—É—Ą–Ķ—Ä –Ņ–Ķ—Ä–Ķ–ī–į—é—ā—Ā—Ź —ā–į–ļ–∂–Ķ

—É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł–Ķ –ł –ļ–ĺ–ľ–į–Ĺ–ī–Ĺ—č–Ķ —Ā–Ľ–ĺ–≤–į –ł —Ā–Ľ–ĺ–≤–ĺ —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź

–į–ī–į–Ņ—ā–Ķ—Ä–į. –í –Ī—É—Ą–Ķ—Ä–Ķ –ł–ľ–Ķ—é—ā—Ā—Ź —Ä–Ķ–≥–ł—Ā—ā—Ä—č –ī–į–Ĺ–Ĺ—č—Ö (–≤—Ö–ĺ–ī–Ĺ–ĺ–Ļ –ł –≤—č—Ö–ĺ–ī–Ĺ–ĺ–Ļ), –ļ–ĺ–ľ–į–Ĺ–ī –ł

—Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź.

–Ď–Ľ–ĺ–ļ —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź

—á—ā–Ķ–Ĺ–ł–Ķ–ľ/–∑–į–Ņ–ł—Ā—Ć—é –Ņ—Ä–ł–Ĺ–ł–ľ–į–Ķ—ā —Ā–ł–≥–Ĺ–į–Ľ—č –ĺ—ā —Ā–ł—Ā—ā–Ķ–ľ–Ĺ–ĺ–Ļ —ą–ł–Ĺ—č –ī–į–Ĺ–Ĺ—č—Ö –ł –≥–Ķ–Ĺ–Ķ—Ä–ł—Ä—É–Ķ—ā —Ā–ł–≥–Ĺ–į–Ľ—č

—É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź —Ä–į–Ī–ĺ—ā–ĺ–Ļ –≤—Ā–Ķ—Ö –Ī–Ľ–ĺ–ļ–ĺ–≤ –į–ī–į–Ņ—ā–Ķ—Ä–į.

–í—č–≤–ĺ–ī—č –ł —Ā–ł–≥–Ĺ–į–Ľ—č –ü–°–ź. –í—č–≤–ĺ–ī—č

–ł —Ā–ł–≥–Ĺ–į–Ľ—č –ü–°–ź –ł–ľ–Ķ—é—ā —Ā–Ľ–Ķ–ī—É—é—Č–Ķ–Ķ –Ĺ–į–∑–Ĺ–į—á–Ķ–Ĺ–ł–Ķ:

- RESET - —É—Ā—ā–į–Ĺ–ĺ–≤–ļ–į –į–ī–į–Ņ—ā–Ķ—Ä–į –≤ –ł—Ā—Ö–ĺ–ī–Ĺ–ĺ–Ķ —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł–Ķ, –Ņ–ĺ—Ā–Ľ–Ķ –Ĺ–Ķ–≥–ĺ

–į–ī–į–Ņ—ā–Ķ—Ä –Ĺ–į—Ö–ĺ–ī–ł—ā—Ā—Ź –≤ –Ī–Ķ–∑–ī–Ķ–Ļ—Ā—ā–≤–ł–ł –ī–ĺ –∑–į–Ņ–ł—Ā–ł –Ĺ–ĺ–≤–ĺ–≥–ĺ –Ĺ–į–Ī–ĺ—Ä–į —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł—Ö —Ā–Ľ–ĺ–≤ –ī–Ľ—Ź

–ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ–Ķ–Ĺ–ł—Ź –∑–į–ī–į–≤–į–Ķ–ľ—č—Ö –Ķ–ľ—É —Ą—É–Ĺ–ļ—Ü–ł–Ļ. –í —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł–Ķ –Ī–Ķ–∑–ī–Ķ–Ļ—Ā—ā–≤–ł—Ź –į–ī–į–Ņ—ā–Ķ—Ä –≤–≤–ĺ–ī–ł—ā—Ā—Ź

—ā–į–ļ–∂–Ķ –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ĺ–Ļ –Ņ–ĺ –ļ–ĺ–ľ–į–Ĺ–ī–Ķ —Ā–Ī—Ä–ĺ—Ā–į;

- CLK - –≤—Ö–ĺ–ī —ā–į–ļ—ā–ĺ–≤–ĺ–Ļ —á–į—Ā—ā–ĺ—ā—č –ī–Ľ—Ź –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–Ķ–≥–ĺ —ā–į–ļ—ā–ł—Ä–ĺ–≤–į–Ĺ–ł—Ź

–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į.

–í–Ĺ–Ķ—ą–Ĺ–ł–Ķ –≤—Ö–ĺ–ī—č –ł –≤—č—Ö–ĺ–ī—č

–į–ī–į–Ņ—ā–Ķ—Ä–į –Ĺ–Ķ –Ņ—Ä–ł–≤—Ź–∑–į–Ĺ—č –ļ —ā–į–ļ—ā–į–ľ —Ā–ł–≥–Ĺ–į–Ľ–į CLK,

–Ĺ–ĺ —á–į—Ā—ā–ĺ—ā–į —ć—ā–ĺ–≥–ĺ —Ā–ł–≥–Ĺ–į–Ľ–į –ī–ĺ–Ľ–∂–Ĺ–į –Ī—č—ā—Ć –≤—č—ą–Ķ –Ī–ł—ā–ĺ–≤–ĺ–Ļ —á–į—Ā—ā–ĺ—ā—č –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –ī–į–Ĺ–Ĺ—č—Ö –Ĺ–Ķ

–ľ–Ķ–Ĺ–Ķ–Ķ —á–Ķ–ľ –≤ 30 —Ä–į–∑;

- ![]() ,

, ![]() ¬†–ł

¬†–ł ![]() ¬†- —Ā–ł–≥–Ĺ–į–Ľ—č, —Ā–ľ—č—Ā–Ľ –ļ–ĺ—ā–ĺ—Ä—č—Ö —É–∂–Ķ –ł–∑–≤–Ķ—Ā—ā–Ķ–Ĺ (—Ā—ā—Ä–ĺ–Ī—č

—á—ā–Ķ–Ĺ–ł—Ź –ł –∑–į–Ņ–ł—Ā–ł –ł —Ā–ł–≥–Ĺ–į–Ľ –≤—č–Ī–ĺ—Ä–į –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č);

¬†- —Ā–ł–≥–Ĺ–į–Ľ—č, —Ā–ľ—č—Ā–Ľ –ļ–ĺ—ā–ĺ—Ä—č—Ö —É–∂–Ķ –ł–∑–≤–Ķ—Ā—ā–Ķ–Ĺ (—Ā—ā—Ä–ĺ–Ī—č

—á—ā–Ķ–Ĺ–ł—Ź –ł –∑–į–Ņ–ł—Ā–ł –ł —Ā–ł–≥–Ĺ–į–Ľ –≤—č–Ī–ĺ—Ä–į –ľ–ł–ļ—Ä–ĺ—Ā—Ö–Ķ–ľ—č);

- C/D (Control/Data) - —É–ļ–į–∑—č–≤–į–Ķ—ā –Ĺ–į —ā–ł–Ņ –Ņ–Ķ—Ä–Ķ–ī–į–≤–į–Ķ–ľ–ĺ–Ļ

–ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł, –Ņ—Ä–ł –Ķ–ī–ł–Ĺ–ł—á–Ĺ–ĺ–ľ –∑–Ĺ–į—á–Ķ–Ĺ–ł–ł —ć—ā–ĺ–≥–ĺ —Ā–ł–≥–Ĺ–į–Ľ–į –≤–≤–ĺ–ī—Ź—ā—Ā—Ź —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł–Ķ —Ā–Ľ–ĺ–≤–į –ł–Ľ–ł

–≤—č–≤–ĺ–ī–ł—ā—Ā—Ź —Ā–Ľ–ĺ–≤–ĺ —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź –į–ī–į–Ņ—ā–Ķ—Ä–į, –Ņ—Ä–ł –Ĺ—É–Ľ–Ķ–≤–ĺ–ľ - –Ņ–Ķ—Ä–Ķ–ī–į—é—ā—Ā—Ź –ī–į–Ĺ–Ĺ—č–Ķ. –í–ľ–Ķ—Ā—ā–Ķ —Ā

—Ā–ł–≥–Ĺ–į–Ľ–į–ľ–ł ![]() ¬†–ł

¬†–ł ![]() ¬†–ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ—Ź–Ķ—ā —Ö–į—Ä–į–ļ—ā–Ķ—Ä –Ņ–Ķ—Ä–Ķ–ī–į—á–ł. –ě–Ī—č—á–Ĺ–ĺ –Ĺ–į —ć—ā–ĺ—ā

–≤—Ö–ĺ–ī –Ņ–ĺ–ī–ļ–Ľ—é—á–į–Ķ—ā—Ā—Ź –ľ–Ľ–į–ī—ą–ł–Ļ —Ä–į–∑—Ä—Ź–ī –į–ī—Ä–Ķ—Ā–į A0.

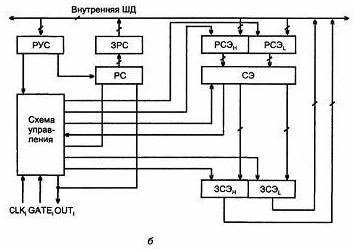

–Ě–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –ł —Ö–į—Ä–į–ļ—ā–Ķ—Ä –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł –∑–į–ī–į—é—ā—Ā—Ź –ī–Ľ—Ź –į–ī–į–Ņ—ā–Ķ—Ä–į —ā–į–Ī–Ľ–ł—Ü–Ķ–Ļ 2.

¬†–ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ—Ź–Ķ—ā —Ö–į—Ä–į–ļ—ā–Ķ—Ä –Ņ–Ķ—Ä–Ķ–ī–į—á–ł. –ě–Ī—č—á–Ĺ–ĺ –Ĺ–į —ć—ā–ĺ—ā

–≤—Ö–ĺ–ī –Ņ–ĺ–ī–ļ–Ľ—é—á–į–Ķ—ā—Ā—Ź –ľ–Ľ–į–ī—ą–ł–Ļ —Ä–į–∑—Ä—Ź–ī –į–ī—Ä–Ķ—Ā–į A0.

–Ě–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –ł —Ö–į—Ä–į–ļ—ā–Ķ—Ä –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł –∑–į–ī–į—é—ā—Ā—Ź –ī–Ľ—Ź –į–ī–į–Ņ—ā–Ķ—Ä–į —ā–į–Ī–Ľ–ł—Ü–Ķ–Ļ 2.

–Ę–į–Ī–Ľ–ł—Ü–į 2

|

C/D |

|

|

|

–ě–Ņ–Ķ—Ä–į—Ü–ł—Ź |

|

0 |

0 |

1 |

0 |

–®–Ē <- –ī–į–Ĺ–Ĺ—č–Ķ –į–ī–į–Ņ—ā–Ķ—Ä–į |

|

0 |

1 |

0 |

0 |

–Ē–į–Ĺ–Ĺ—č–Ķ –į–ī–į–Ņ—ā–Ķ—Ä–į <- –®–Ē |

|

1 |

0 |

1 |

0 |

–®–Ē <- —Ā–Ľ–ĺ–≤–ĺ —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź |

|

1 |

1 |

0 |

0 |

–£–Ņ—Ä–į–≤–Ľ—Ź—é—Č–Ķ–Ķ —Ā–Ľ–ĺ–≤–ĺ <- –®–Ē |

|

X |

1 |

1 |

0 |

–ě—ā–ļ–Ľ—é—á–Ķ–Ĺ–ĺ |

|

X |

X |

X |

1 |

–ě—ā–ļ–Ľ—é—á–Ķ–Ĺ–ĺ |

–ź–ī–į–Ņ—ā–Ķ—Ä –ł–ľ–Ķ–Ķ—ā –Ĺ–į–Ī–ĺ—Ä

—É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł—Ö –≤—Ö–ĺ–ī–Ĺ—č—Ö –ł –≤—č—Ö–ĺ–ī–Ĺ—č—Ö —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ –ī–Ľ—Ź —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –ľ–ĺ–ī–Ķ–ľ–ĺ–ľ. –ú–ĺ–ī–Ķ–ľ —É–ļ–į–∑–į–Ĺ

–∑–ī–Ķ—Ā—Ć –ļ–į–ļ –Ĺ–į–ł–Ī–ĺ–Ľ–Ķ–Ķ —ā–ł–Ņ–ł—á–Ĺ–ĺ–Ķ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–ĺ, —Ä–į–Ī–ĺ—ā–į—é—Č–Ķ–Ķ –≤–ĺ –≤–∑–į–ł–ľ–ĺ–ī–Ķ–Ļ—Ā—ā–≤–ł–ł —Ā –ü–°–ź,

—Ö–ĺ—ā—Ź, –≤ —Ā—É—Č–Ĺ–ĺ—Ā—ā–ł, —ć—ā–ĺ —Ā–ł–≥–Ĺ–į–Ľ—č –ĺ–Ī—Č–Ķ–≥–ĺ –Ĺ–į–∑–Ĺ–į—á–Ķ–Ĺ–ł—Ź, –ļ–ĺ—ā–ĺ—Ä—č–Ķ –ľ–ĺ–≥—É—ā –Ī—č—ā—Ć

–ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ—č –ł –ī–Ľ—Ź —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –ī—Ä—É–≥–ł–ľ–ł —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į–ľ–ł. –Ē–Ľ—Ź —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –ľ–ĺ–ī–Ķ–ľ–ĺ–ľ

(—ā–Ķ—Ä–ľ–ł–Ĺ–į–Ľ–ĺ–ľ) –ł–ľ–Ķ—é—ā—Ā—Ź –ī–≤–Ķ –Ņ–į—Ä—č —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ –ļ–≤–ł—ā–ł—Ä–ĺ–≤–į–Ĺ–ł—Ź:

- ![]() ¬†(Data Set Ready) - –∑–į–Ņ—Ä–ĺ—Ā

–≥–ĺ—ā–ĺ–≤–Ĺ–ĺ—Ā—ā–ł –Ņ–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ–į —ā–Ķ—Ä–ľ–ł–Ĺ–į–Ľ–į, —Ā–ł–≥–Ĺ–į–Ľ —Ā–≤—Ź–∑–į–Ĺ —Ā –ĺ–ī–Ĺ–ĺ—Ä–į–∑—Ä—Ź–ī–Ĺ—č–ľ –Ņ–ĺ—Ä—ā–ĺ–ľ –ł –ľ–ĺ–∂–Ķ—ā

–Ī—č—ā—Ć –Ņ—Ä–ĺ–≤–Ķ—Ä–Ķ–Ĺ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ —á—ā–Ķ–Ĺ–ł–Ķ–ľ —Ā–Ľ–ĺ–≤–į —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź. –Ě–ł–∑–ļ–ł–Ļ —É—Ä–ĺ–≤–Ķ–Ĺ—Ć —ć—ā–ĺ–≥–ĺ —Ā–ł–≥–Ĺ–į–Ľ–į

–≥–ĺ–≤–ĺ—Ä–ł—ā –ĺ —ā–ĺ–ľ, —á—ā–ĺ –ľ–ĺ–ī–Ķ–ľ (—ā–Ķ—Ä–ľ–ł–Ĺ–į–Ľ) –ł–ľ–Ķ–Ķ—ā –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł—é –ī–Ľ—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É;

¬†(Data Set Ready) - –∑–į–Ņ—Ä–ĺ—Ā

–≥–ĺ—ā–ĺ–≤–Ĺ–ĺ—Ā—ā–ł –Ņ–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ–į —ā–Ķ—Ä–ľ–ł–Ĺ–į–Ľ–į, —Ā–ł–≥–Ĺ–į–Ľ —Ā–≤—Ź–∑–į–Ĺ —Ā –ĺ–ī–Ĺ–ĺ—Ä–į–∑—Ä—Ź–ī–Ĺ—č–ľ –Ņ–ĺ—Ä—ā–ĺ–ľ –ł –ľ–ĺ–∂–Ķ—ā

–Ī—č—ā—Ć –Ņ—Ä–ĺ–≤–Ķ—Ä–Ķ–Ĺ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ —á—ā–Ķ–Ĺ–ł–Ķ–ľ —Ā–Ľ–ĺ–≤–į —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź. –Ě–ł–∑–ļ–ł–Ļ —É—Ä–ĺ–≤–Ķ–Ĺ—Ć —ć—ā–ĺ–≥–ĺ —Ā–ł–≥–Ĺ–į–Ľ–į

–≥–ĺ–≤–ĺ—Ä–ł—ā –ĺ —ā–ĺ–ľ, —á—ā–ĺ –ľ–ĺ–ī–Ķ–ľ (—ā–Ķ—Ä–ľ–ł–Ĺ–į–Ľ) –ł–ľ–Ķ–Ķ—ā –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł—é –ī–Ľ—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É;

- ¬†![]() ¬†(Data Terminal Ready) - —ć—ā–ĺ—ā —Ā–ł–≥–Ĺ–į–Ľ

—Ź–≤–Ľ—Ź–Ķ—ā—Ā—Ź —Ä–Ķ–į–ļ—Ü–ł–Ķ–Ļ –Ĺ–į –∑–į–Ņ—Ä–ĺ—Ā

¬†(Data Terminal Ready) - —ć—ā–ĺ—ā —Ā–ł–≥–Ĺ–į–Ľ

—Ź–≤–Ľ—Ź–Ķ—ā—Ā—Ź —Ä–Ķ–į–ļ—Ü–ł–Ķ–Ļ –Ĺ–į –∑–į–Ņ—Ä–ĺ—Ā ![]() . –ź–ļ—ā–ł–≤–ł–∑–ł—Ä—É–Ķ—ā—Ā—Ź

—Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–ł–ľ –Ī–ł—ā–ĺ–ľ –ļ–ĺ–ľ–į–Ĺ–ī–Ĺ–ĺ–≥–ĺ —Ā–Ľ–ĺ–≤–į, –Ķ—Ā–Ľ–ł –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ –ĺ–Ī–ľ–Ķ–Ĺ —Ā

–ľ–ĺ–ī–Ķ–ľ–ĺ–ľ. –°–≤—Ź–∑–į–Ĺ —Ā —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ–ł–Ķ–ľ –ľ–ĺ–ī–Ķ–ľ—É –Ņ–ĺ—Ā—č–Ľ–ļ–ł –ī–į–Ĺ–Ĺ—č—Ö –Ĺ–į –≤—Ö–ĺ–ī

–Ņ—Ä–ł–Ķ–ľ–Ĺ–ł–ļ–į –į–ī–į–Ņ—ā–Ķ—Ä–į;

. –ź–ļ—ā–ł–≤–ł–∑–ł—Ä—É–Ķ—ā—Ā—Ź

—Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–ł–ľ –Ī–ł—ā–ĺ–ľ –ļ–ĺ–ľ–į–Ĺ–ī–Ĺ–ĺ–≥–ĺ —Ā–Ľ–ĺ–≤–į, –Ķ—Ā–Ľ–ł –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ –ĺ–Ī–ľ–Ķ–Ĺ —Ā

–ľ–ĺ–ī–Ķ–ľ–ĺ–ľ. –°–≤—Ź–∑–į–Ĺ —Ā —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ–ł–Ķ–ľ –ľ–ĺ–ī–Ķ–ľ—É –Ņ–ĺ—Ā—č–Ľ–ļ–ł –ī–į–Ĺ–Ĺ—č—Ö –Ĺ–į –≤—Ö–ĺ–ī

–Ņ—Ä–ł–Ķ–ľ–Ĺ–ł–ļ–į –į–ī–į–Ņ—ā–Ķ—Ä–į;

- ![]() ¬†(Request to Send) - —Ā–ł–≥–Ĺ–į–Ľ —Ā–≤—Ź–∑–į–Ĺ

—Ā –ĺ–ī–Ĺ–ĺ—Ä–į–∑—Ä—Ź–ī–Ĺ—č–ľ –≤—č—Ö–ĺ–ī–Ĺ—č–ľ –Ņ–ĺ—Ä—ā–ĺ–ľ. –Į–≤–Ľ—Ź–Ķ—ā—Ā—Ź –∑–į–Ņ—Ä–ĺ—Ā–ĺ–ľ –ĺ—ā –į–ī–į–Ņ—ā–Ķ—Ä–į –≥–ĺ—ā–ĺ–≤–Ĺ–ĺ—Ā—ā–ł

–Ņ—Ä–ł–Ķ–ľ–Ĺ–ł–ļ–į —ā–Ķ—Ä–ľ–ł–Ĺ–į–Ľ–į –Ņ—Ä–ł–Ĺ—Ź—ā—Ć –ī–į–Ĺ–Ĺ—č–Ķ. –ó–į–ī–į–Ķ—ā—Ā—Ź –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ–ľ —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–Ķ–≥–ĺ

–Ī–ł—ā–į –≤ –ļ–ĺ–ľ–į–Ĺ–ī–Ĺ–ĺ–ľ —Ā–Ľ–ĺ–≤–Ķ, –ļ–ĺ–≥–ī–į –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ –ĺ–Ī–ľ–Ķ–Ĺ —Ā –ľ–ĺ–ī–Ķ–ľ–ĺ–ľ;

¬†(Request to Send) - —Ā–ł–≥–Ĺ–į–Ľ —Ā–≤—Ź–∑–į–Ĺ

—Ā –ĺ–ī–Ĺ–ĺ—Ä–į–∑—Ä—Ź–ī–Ĺ—č–ľ –≤—č—Ö–ĺ–ī–Ĺ—č–ľ –Ņ–ĺ—Ä—ā–ĺ–ľ. –Į–≤–Ľ—Ź–Ķ—ā—Ā—Ź –∑–į–Ņ—Ä–ĺ—Ā–ĺ–ľ –ĺ—ā –į–ī–į–Ņ—ā–Ķ—Ä–į –≥–ĺ—ā–ĺ–≤–Ĺ–ĺ—Ā—ā–ł

–Ņ—Ä–ł–Ķ–ľ–Ĺ–ł–ļ–į —ā–Ķ—Ä–ľ–ł–Ĺ–į–Ľ–į –Ņ—Ä–ł–Ĺ—Ź—ā—Ć –ī–į–Ĺ–Ĺ—č–Ķ. –ó–į–ī–į–Ķ—ā—Ā—Ź –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ–ľ —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–Ķ–≥–ĺ

–Ī–ł—ā–į –≤ –ļ–ĺ–ľ–į–Ĺ–ī–Ĺ–ĺ–ľ —Ā–Ľ–ĺ–≤–Ķ, –ļ–ĺ–≥–ī–į –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ –ĺ–Ī–ľ–Ķ–Ĺ —Ā –ľ–ĺ–ī–Ķ–ľ–ĺ–ľ;

- ![]() ¬†(Clear to Send) - —Ā–ł–≥–Ĺ–į–Ľ

–≥–ĺ—ā–ĺ–≤–Ĺ–ĺ—Ā—ā–ł –Ņ—Ä–ł–Ķ–ľ–Ĺ–ł–ļ–į —ā–Ķ—Ä–ľ–ł–Ĺ–į–Ľ–į –Ņ—Ä–ł–Ĺ—Ź—ā—Ć –ī–į–Ĺ–Ĺ—č–Ķ. –Ě–ł–∑–ļ–ł–Ļ —É—Ä–ĺ–≤–Ķ–Ĺ—Ć —ć—ā–ĺ–≥–ĺ —Ā–ł–≥–Ĺ–į–Ľ–į

—Ä–į–∑—Ä–Ķ—ą–į–Ķ—ā –į–ī–į–Ņ—ā–Ķ—Ä—É –Ņ–Ķ—Ä–Ķ–ī–į—á—É –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č—Ö –ī–į–Ĺ–Ĺ—č—Ö, –Ķ—Ā–Ľ–ł —É—Ā—ā–į–Ĺ–ĺ–≤–Ľ–Ķ–Ĺ

–Ī–ł—ā TxEN –≤ –ļ–ĺ–ľ–į–Ĺ–ī–Ĺ–ĺ–ľ —Ā–Ľ–ĺ–≤–Ķ. –ü—Ä–ł

—Ā–Ĺ—Ź—ā–ł–ł TxEN –ł–Ľ–ł

¬†(Clear to Send) - —Ā–ł–≥–Ĺ–į–Ľ

–≥–ĺ—ā–ĺ–≤–Ĺ–ĺ—Ā—ā–ł –Ņ—Ä–ł–Ķ–ľ–Ĺ–ł–ļ–į —ā–Ķ—Ä–ľ–ł–Ĺ–į–Ľ–į –Ņ—Ä–ł–Ĺ—Ź—ā—Ć –ī–į–Ĺ–Ĺ—č–Ķ. –Ě–ł–∑–ļ–ł–Ļ —É—Ä–ĺ–≤–Ķ–Ĺ—Ć —ć—ā–ĺ–≥–ĺ —Ā–ł–≥–Ĺ–į–Ľ–į

—Ä–į–∑—Ä–Ķ—ą–į–Ķ—ā –į–ī–į–Ņ—ā–Ķ—Ä—É –Ņ–Ķ—Ä–Ķ–ī–į—á—É –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č—Ö –ī–į–Ĺ–Ĺ—č—Ö, –Ķ—Ā–Ľ–ł —É—Ā—ā–į–Ĺ–ĺ–≤–Ľ–Ķ–Ĺ

–Ī–ł—ā TxEN –≤ –ļ–ĺ–ľ–į–Ĺ–ī–Ĺ–ĺ–ľ —Ā–Ľ–ĺ–≤–Ķ. –ü—Ä–ł

—Ā–Ĺ—Ź—ā–ł–ł TxEN –ł–Ľ–ł ![]() ¬†–≤–ĺ –≤—Ä–Ķ–ľ—Ź —Ä–į–Ī–ĺ—ā—č –Ņ–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ–į –ĺ–Ĺ –Ī—É–ī–Ķ—ā

–Ņ–Ķ—Ä–Ķ–ī–į–≤–į—ā—Ć –≤—Ā–Ķ –ī–į–Ĺ–Ĺ—č–Ķ, –∑–į–Ņ–ł—Ā–į–Ĺ–Ĺ—č–Ķ –ī–ĺ –∑–į–Ņ—Ä–Ķ—Č–Ķ–Ĺ–ł—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á–ł, –Ņ—Ä–Ķ–∂–ī–Ķ —á–Ķ–ľ

–ĺ—Ā—ā–į–Ĺ–ĺ–≤–ł—ā—Ā—Ź.

¬†–≤–ĺ –≤—Ä–Ķ–ľ—Ź —Ä–į–Ī–ĺ—ā—č –Ņ–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ–į –ĺ–Ĺ –Ī—É–ī–Ķ—ā

–Ņ–Ķ—Ä–Ķ–ī–į–≤–į—ā—Ć –≤—Ā–Ķ –ī–į–Ĺ–Ĺ—č–Ķ, –∑–į–Ņ–ł—Ā–į–Ĺ–Ĺ—č–Ķ –ī–ĺ –∑–į–Ņ—Ä–Ķ—Č–Ķ–Ĺ–ł—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á–ł, –Ņ—Ä–Ķ–∂–ī–Ķ —á–Ķ–ľ

–ĺ—Ā—ā–į–Ĺ–ĺ–≤–ł—ā—Ā—Ź.

–ü–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ –ü–°–ź. –Ď—É—Ą–Ķ—Ä

–Ņ–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ–į –į–ī–į–Ņ—ā–Ķ—Ä–į (–Ī—É—Ą–Ķ—Ä –Ę—Ö) –Ņ—Ä–ł–Ĺ–ł–ľ–į–Ķ—ā –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ—č–Ķ

–ī–į–Ĺ–Ĺ—č–Ķ –ĺ—ā –Ī—É—Ą–Ķ—Ä–į –®–Ē, –Ņ—Ä–Ķ–ĺ–Ī—Ä–į–∑—É–Ķ—ā –ł—Ö –≤ –Ņ–ĺ—ā–ĺ–ļ –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č—Ö –Ī–ł—ā–ĺ–≤, –≤–≤–ĺ–ī–ł—ā –≤

—ć—ā–ĺ—ā –Ņ–ĺ—ā–ĺ–ļ —Ā–Ľ—É–∂–Ķ–Ī–Ĺ—č–Ķ —Ā–ł–ľ–≤–ĺ–Ľ—č –ł–Ľ–ł –Ī–ł—ā—č –ł –≤—č–ī–į–Ķ—ā —Ā–ĺ—Ā—ā–į–≤–Ľ–Ķ–Ĺ–Ĺ—č–Ļ –Ĺ–Ķ–ĺ–Ī—Ö–ĺ–ī–ł–ľ—č–ľ –ĺ–Ī—Ä–į–∑–ĺ–ľ

–Ņ–ĺ—ā–ĺ–ļ –Ī–ł—ā–ĺ–≤ –Ĺ–į –≤—č–≤–ĺ–ī TxD –Ņ–ĺ –ĺ—ā—Ä–ł—Ü–į—ā–Ķ–Ľ—Ć–Ĺ—č–ľ —Ą—Ä–ĺ–Ĺ—ā–į–ľ –ł–ľ–Ņ—É–Ľ—Ć—Ā–ĺ–≤ —á–į—Ā—ā–ĺ—ā—č –Ę—Ö–°. –ü–Ķ—Ä–Ķ–ī–į—á–į –Ĺ–į—á–ł–Ĺ–į–Ķ—ā—Ā—Ź –Ņ–ĺ—Ā–Ľ–Ķ –Ķ–Ķ —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ–ł—Ź –ł –Ņ—Ä–ł —É—Ā–Ľ–ĺ–≤–ł–ł ![]() ¬†= 0. –í—č–≤–ĺ–ī TxD –Ņ—Ä–ł–Ĺ–ł–ľ–į–Ķ—ā –≤—č—Ā–ĺ–ļ–ł–Ļ —É—Ä–ĺ–≤–Ķ–Ĺ—Ć –Ĺ–į–Ņ—Ä—Ź–∂–Ķ–Ĺ–ł—Ź –Ņ–ĺ—Ā–Ľ–Ķ —Ā–Ī—Ä–ĺ—Ā–į, –∑–į–Ņ—Ä–Ķ—ā–ĺ–≤

–Ņ–ĺ —É—Ā–Ľ–ĺ–≤–ł—Ź–ľ TxEN –ł–Ľ–ł

¬†= 0. –í—č–≤–ĺ–ī TxD –Ņ—Ä–ł–Ĺ–ł–ľ–į–Ķ—ā –≤—č—Ā–ĺ–ļ–ł–Ļ —É—Ä–ĺ–≤–Ķ–Ĺ—Ć –Ĺ–į–Ņ—Ä—Ź–∂–Ķ–Ĺ–ł—Ź –Ņ–ĺ—Ā–Ľ–Ķ —Ā–Ī—Ä–ĺ—Ā–į, –∑–į–Ņ—Ä–Ķ—ā–ĺ–≤

–Ņ–ĺ —É—Ā–Ľ–ĺ–≤–ł—Ź–ľ TxEN –ł–Ľ–ł ![]() ¬†–Ľ–ł–Ī–ĺ –Ņ—Ä–ł —É—Ā–Ľ–ĺ–≤–ł–ł "–Ņ–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ –Ņ—É—Ā—ā",

—Ā–≤—Ź–∑–į–Ĺ–Ĺ–ĺ–ľ —Ā —Ā–ł–≥–Ĺ–į–Ľ–ĺ–ľ –Ę—Ö–ē (TxEmpty). –°—Ö–Ķ–ľ–į —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –Ņ–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ–ĺ–ľ (—É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł–Ķ –Ę—Ö) –≤—č—Ä–į–Ī–į—ā—č–≤–į–Ķ—ā —Ā–Ľ–Ķ–ī—É—é—Č–ł–Ķ –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–ł–Ķ –ł –≤–Ĺ–Ķ—ą–Ĺ–ł–Ķ —Ā–ł–≥–Ĺ–į–Ľ—č –ī–Ľ—Ź

–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ–≤ –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č—Ö –ī–į–Ĺ–Ĺ—č—Ö:

¬†–Ľ–ł–Ī–ĺ –Ņ—Ä–ł —É—Ā–Ľ–ĺ–≤–ł–ł "–Ņ–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ –Ņ—É—Ā—ā",

—Ā–≤—Ź–∑–į–Ĺ–Ĺ–ĺ–ľ —Ā —Ā–ł–≥–Ĺ–į–Ľ–ĺ–ľ –Ę—Ö–ē (TxEmpty). –°—Ö–Ķ–ľ–į —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –Ņ–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ–ĺ–ľ (—É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł–Ķ –Ę—Ö) –≤—č—Ä–į–Ī–į—ā—č–≤–į–Ķ—ā —Ā–Ľ–Ķ–ī—É—é—Č–ł–Ķ –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–ł–Ķ –ł –≤–Ĺ–Ķ—ą–Ĺ–ł–Ķ —Ā–ł–≥–Ĺ–į–Ľ—č –ī–Ľ—Ź

–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ–≤ –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č—Ö –ī–į–Ĺ–Ĺ—č—Ö:

- TxRDY - —ć—ā–ĺ—ā –≤—č—Ö–ĺ–ī–Ĺ–ĺ–Ļ —Ā–ł–≥–Ĺ–į–Ľ —É–ļ–į–∑—č–≤–į–Ķ—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä—É –Ĺ–į –≥–ĺ—ā–ĺ–≤–Ĺ–ĺ—Ā—ā—Ć

–Ņ–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ–į –į–ī–į–Ņ—ā–Ķ—Ä–į –Ņ—Ä–ł–Ĺ—Ź—ā—Ć —Ā–ł–ľ–≤–ĺ–Ľ –ī–į–Ĺ–Ĺ—č—Ö. –°–ł–≥–Ĺ–į–Ľ –ľ–ĺ–∂–Ķ—ā –Ņ—Ä–ĺ–≤–Ķ—Ä—Ź—ā—Ć—Ā—Ź —á—ā–Ķ–Ĺ–ł–Ķ–ľ

—Ā–Ľ–ĺ–≤–į —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź –ł–Ľ–ł –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į—ā—Ć—Ā—Ź –ļ–į–ļ –∑–į–Ņ—Ä–ĺ—Ā –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź (–ĺ–Ĺ

–ľ–ĺ–∂–Ķ—ā –ľ–į—Ā–ļ–ł—Ä–ĺ–≤–į—ā—Ć—Ā—Ź –Ī–ł—ā–ĺ–ľ TxEN¬† –ļ–ĺ–ľ–į–Ĺ–ī–Ĺ–ĺ–≥–ĺ —Ā–Ľ–ĺ–≤–į).

–ź–≤—ā–ĺ–ľ–į—ā–ł—á–Ķ—Ā–ļ–ł —Ā–Ī—Ä–į—Ā—č–≤–į–Ķ—ā—Ā—Ź –Ņ–Ķ—Ä–Ķ–ī–Ĺ–ł–ľ —Ą—Ä–ĺ–Ĺ—ā–ĺ–ľ —Ā—ā—Ä–ĺ–Ī–į –∑–į–Ņ–ł—Ā–ł WR, –ļ–ĺ–≥–ī–į —Ā–ł–ľ–≤–ĺ–Ľ –ī–į–Ĺ–Ĺ—č—Ö –∑–į–≥—Ä—É–∂–į–Ķ—ā—Ā—Ź –ł–∑ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į;

- –Ę—Ö–ē

- —Ā–ł–≥–Ĺ–į–Ľ —É—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā—Ā—Ź, –ļ–ĺ–≥–ī–į –į–ī–į–Ņ—ā–Ķ—Ä –Ĺ–Ķ –ł–ľ–Ķ–Ķ—ā —Ā–ł–ľ–≤–ĺ–Ľ–į –ī–Ľ—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á–ł (–≤—Ö–ĺ–ī–Ĺ–ĺ–Ļ

–Ī—É—Ą–Ķ—Ä –≤ –Ī–Ľ–ĺ–ļ–Ķ "–Ī—É—Ą–Ķ—Ä –®–Ē" –Ņ—É—Ā—ā, –ł –Ņ–ĺ—Ā–Ľ–Ķ –≤—č—Ö–ĺ–ī–į —Ā–ł–ľ–≤–ĺ–Ľ–į –ł–∑ —Ā–ī–≤–ł–≥–į—é—Č–Ķ–≥–ĺ

—Ä–Ķ–≥–ł—Ā—ā—Ä–į –Ņ–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ–į —ć—ā–ĺ—ā —Ä–Ķ–≥–ł—Ā—ā—Ä –Ī—É–ī–Ķ—ā –Ĺ–Ķ—á–Ķ–ľ –∑–į–≥—Ä—É–∑–ł—ā—Ć).

–°–Ī—Ä–į—Ā—č–≤–į–Ķ—ā—Ā—Ź –Ņ–ĺ—Ā–Ľ–Ķ –Ņ–ĺ–Ľ—É—á–Ķ–Ĺ–ł—Ź

—Ā–ł–ľ–≤–ĺ–Ľ–į –ĺ—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į, –Ķ—Ā–Ľ–ł –Ņ–Ķ—Ä–Ķ–ī–į—á–į —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ–į, –ł –ĺ—Ā—ā–į–Ķ—ā—Ā—Ź –≤—č—Ā–ĺ–ļ–ł–ľ, –Ķ—Ā–Ľ–ł

–Ņ–Ķ—Ä–Ķ–ī–į—á–į –∑–į–Ņ—Ä–Ķ—Č–Ķ–Ĺ–į —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–ł–ľ –Ī–ł—ā–ĺ–ľ –ļ–ĺ–ľ–į–Ĺ–ī–Ĺ–ĺ–≥–ĺ —Ā–Ľ–ĺ–≤–į. –°–ł–≥–Ĺ–į–Ľ –ľ–ĺ–∂–Ķ—ā –Ī—č—ā—Ć –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ

–ī–Ľ—Ź –ł–Ĺ–ī–ł–ļ–į—Ü–ł–ł –ļ–ĺ–Ĺ—Ü–į —Ä–Ķ–∂–ł–ľ–į –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –ł –ĺ–Ņ–ĺ–≤–Ķ—Č–Ķ–Ĺ–ł—Ź –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į –ĺ –ľ–ĺ–ľ–Ķ–Ĺ—ā–Ķ

–Ņ–Ķ—Ä–Ķ–ļ–Ľ—é—á–Ķ–Ĺ–ł—Ź –Ľ–ł–Ĺ–ł–ł –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –Ĺ–į –ī—Ä—É–≥–ĺ–Ķ –Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł–Ķ –≤ –Ņ–ĺ–Ľ—É–ī—É–Ņ–Ľ–Ķ–ļ—Ā–Ĺ–ĺ–ľ —Ä–Ķ–∂–ł–ľ–Ķ

—Ä–į–Ī–ĺ—ā—č. –í —Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ–ĺ–ľ —Ä–Ķ–∂–ł–ľ–Ķ –≤—č—Ā–ĺ–ļ–ł–Ļ —É—Ä–ĺ–≤–Ķ–Ĺ—Ć —Ā–ł–≥–Ĺ–į–Ľ–į –Ņ–ĺ–ļ–į–∑—č–≤–į–Ķ—ā, —á—ā–ĺ —Ā–ł–ľ–≤–ĺ–Ľ –Ĺ–Ķ

–Ī—č–Ľ –∑–į–≥—Ä—É–∂–Ķ–Ĺ –ł –≤ –Ņ–ĺ—ā–ĺ–ļ –ī–į–Ĺ–Ĺ—č—Ö —Ā–Ľ–Ķ–ī—É–Ķ—ā –≤–≤–ĺ–ī–ł—ā—Ć —Ā–ł–Ĺ—Ö—Ä–ĺ—Ā–ł–ľ–≤–ĺ–Ľ—č.

–ü–ĺ–ļ–į –Ņ–Ķ—Ä–Ķ–ī–į—é—ā—Ā—Ź —Ā–ł–Ĺ—Ö—Ä–ĺ—Ā–ł–ľ–≤–ĺ–Ľ—č, –≤—č—Ā–ĺ–ļ–ł–Ļ —É—Ä–ĺ–≤–Ķ–Ĺ—Ć

—Ā–ł–≥–Ĺ–į–Ľ–į —Ā–ĺ—Ö—Ä–į–Ĺ—Ź–Ķ—ā—Ā—Ź;

- –Ę—Ö–° –ł RxC - —Ā–ł–≥–Ĺ–į–Ľ—č

—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–ł–∑–į—Ü–ł–ł –Ņ–Ķ—Ä–Ķ–ī–į—ā—á–ł–ļ–į –ł –Ņ—Ä–ł–Ķ–ľ–Ĺ–ł–ļ–į, –∑–į–ī–į—é—Č–ł–Ķ —Ā–ļ–ĺ—Ä–ĺ—Ā—ā—Ć —Ā–Ľ–Ķ–ī–ĺ–≤–į–Ĺ–ł—Ź

–Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č—Ö –Ī–ł—ā–ĺ–≤. –ü—Ä–ł —Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ—č—Ö –Ņ–Ķ—Ä–Ķ–ī–į—á–į—Ö –Ī–ĺ–ī–ĺ–≤–į—Ź —Ā–ļ–ĺ—Ä–ĺ—Ā—ā—Ć —Ä–į–≤–Ĺ–į —á–į—Ā—ā–ĺ—ā–Ķ –Ę—Ö–°

(RxC),

–Ņ—Ä–ł –į—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ—č—Ö –ĺ–Ĺ–į —Ź–≤–Ľ—Ź–Ķ—ā—Ā—Ź —á–į—Ā—ā—Ć—é —á–į—Ā—ā–ĺ—ā—č –Ę—Ö–° (RxC)

(—ć—ā–ĺ 1, –ł–Ľ–ł 1/16 –ł–Ľ–ł 1/64 –ĺ—ā –Ę—Ö–° –ł–Ľ–ł RxC).

–ě—á–Ķ–Ĺ—Ć —á–į—Ā—ā–ĺ —á–į—Ā—ā–ĺ—ā—č –Ę—Ö–° –ł RxC –ł–ī–Ķ–Ĺ—ā–ł—á–Ĺ—č. –ė—Ö —Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ–ĺ—Ā—ā–ł —Ā —Ā–ł–≥–Ĺ–į–Ľ–ĺ–ľ CLK –Ĺ–Ķ —ā—Ä–Ķ–Ī—É–Ķ—ā—Ā—Ź.

–ü—Ä–ł–Ķ–ľ–Ĺ–ł–ļ –ü–°–ź. –Ď—É—Ą–Ķ—Ä

–Ņ—Ä–ł–Ķ–ľ–Ĺ–ł–ļ–į –Ņ—Ä–ł–Ĺ–ł–ľ–į–Ķ—ā –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č–Ķ –ī–į–Ĺ–Ĺ—č–Ķ, –Ņ—Ä–Ķ–ĺ–Ī—Ä–į–∑—É–Ķ—ā –ł—Ö –≤ –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ—Ć–Ĺ—č–Ķ,

–Ņ—Ä–ĺ–≤–Ķ—Ä—Ź–Ķ—ā –Ī–ł—ā—č –ł–Ľ–ł —Ā–ł–ľ–≤–ĺ–Ľ—č, —Ā–Ņ–Ķ—Ü–ł—Ą–ł—á–Ĺ—č–Ķ –ī–Ľ—Ź –Ņ–ĺ—Ā—č–Ľ–ĺ–ļ –ī–į–Ĺ–Ĺ–ĺ–≥–ĺ —ā–ł–Ņ–į –ł –Ņ–ĺ—Ā—č–Ľ–į–Ķ—ā

–Ņ—Ä–ł–Ĺ—Ź—ā—č–Ļ —Ā–ł–ľ–≤–ĺ–Ľ –≤ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä. –í—č–≤–ĺ–ī RxD —Ā–Ľ—É–∂–ł—ā –≤—Ö–ĺ–ī–ĺ–ľ –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č—Ö –ī–į–Ĺ–Ĺ—č—Ö.

–Ď–Ľ–ĺ–ļ —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –Ņ—Ä–ł–Ķ–ľ–Ĺ–ł–ļ–ĺ–ľ Rx –ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–ł–≤–į–Ķ—ā —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł–Ķ –≤—Ā–Ķ–ľ–ł –ī–Ķ–Ļ—Ā—ā–≤–ł—Ź–ľ–ł, —Ā–≤—Ź–∑–į–Ĺ–Ĺ—č–ľ–ł —Ā

–Ņ—Ä–ł–Ķ–ľ–ĺ–ľ –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł–ł. –°—Ö–Ķ–ľ—č —ć—ā–ĺ–≥–ĺ –Ī–Ľ–ĺ–ļ–į –Ņ—Ä–Ķ–ī–ĺ—ā–≤—Ä–į—Č–į—é—ā –≤–ĺ—Ā–Ņ—Ä–ł—Ź—ā–ł–Ķ –Ĺ–Ķ–ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ–ľ–ĺ–Ļ

–Ľ–ł–Ĺ–ł–ł –ī–į–Ĺ–Ĺ—č—Ö –ļ–į–ļ L-–į–ļ—ā–ł–≤–Ĺ–ĺ–Ļ –≤ —Ä–Ķ–∂–ł–ľ–Ķ –Ņ–į—É–∑—č. –Ē–Ľ—Ź –Ĺ–į—á–į–Ľ–į

–Ņ—Ä–ł–Ķ–ľ–į —ā—Ä–Ķ–Ī—É–Ķ—ā—Ā—Ź –Ņ–ĺ—Ź–≤–Ľ–Ķ–Ĺ–ł–Ķ –≤—č—Ā–ĺ–ļ–ĺ–≥–ĺ —É—Ä–ĺ–≤–Ĺ—Ź (–ľ–į—Ä–ļ–ł) –Ĺ–į –≤—Ö–ĺ–ī–Ķ RxD –Ņ–ĺ—Ā–Ľ–Ķ —Ā–Ī—Ä–ĺ—Ā–į —Ā–ł—Ā—ā–Ķ–ľ—č. –ē—Ā–Ľ–ł —ć—ā–ĺ –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā—Ā—Ź, —ā–ĺ —Ä–į–∑—Ä–Ķ—ą–į–Ķ—ā—Ā—Ź

–Ņ–ĺ–ł—Ā–ļ –ĺ—ā—Ä–ł—Ü–į—ā–Ķ–Ľ—Ć–Ĺ–ĺ–≥–ĺ —Ą—Ä–ĺ–Ĺ—ā–į –≤—Ö–ĺ–ī–Ĺ–ĺ–≥–ĺ —Ā–ł–≥–Ĺ–į–Ľ–į (—Ā—ā–į—Ä—ā-–Ī–ł—ā–į). –ė—Ā—ā–ł–Ĺ–Ĺ–ĺ—Ā—ā—Ć

—Ā—ā–į—Ä—ā-–Ī–ł—ā–į —É—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā—Ā—Ź –Ņ—Ä–ĺ–≤–Ķ—Ä–ļ–ĺ–Ļ —É—Ä–ĺ–≤–Ĺ—Ź —Ā–ł–≥–Ĺ–į–Ľ–į –≤ –Ķ–≥–ĺ —Ā–Ķ—Ä–Ķ–ī–ł–Ĺ–Ķ. –ě—ą–ł–Ī–ļ–ł

—Ä–į–Ī–ĺ—ā—č –į–ī–į–Ņ—ā–Ķ—Ä–į —É—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į—é—ā —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–ł–Ķ –Ī–ł—ā—č –≤ —Ā–Ľ–ĺ–≤–Ķ —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź (—á–Ķ—ā–Ĺ–ĺ—Ā—ā–ł,

—Ą–ĺ—Ä–ľ–į—ā–į –ł–Ľ–ł –Ņ–Ķ—Ä–Ķ–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł—Ź, –Ķ—Ā–Ľ–ł –Ĺ–ĺ–≤–į—Ź –ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł—Ź –∑–į–ľ–Ķ—Č–į–Ķ—ā —Ā—ā–į—Ä—É—é

—Ä–į–Ĺ—Ć—ą–Ķ, —á–Ķ–ľ –ĺ–Ĺ–į –Ī—č–Ľ–į –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į–Ĺ–į).

RxRDY - –≤—č—Ö–ĺ–ī–Ĺ–ĺ–Ļ —Ā–ł–≥–Ĺ–į–Ľ, –Ņ–ĺ–ļ–į–∑—č–≤–į—é—Č–ł–Ļ, —á—ā–ĺ

–į–ī–į–Ņ—ā–Ķ—Ä –ł–ľ–Ķ–Ķ—ā —Ā–ł–ľ–≤–ĺ–Ľ, –≥–ĺ—ā–ĺ–≤—č–Ļ –ļ –≤—č–≤–ĺ–ī—É –≤ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä. –ú–ĺ–∂–Ķ—ā –Ņ—Ä–ĺ–≤–Ķ—Ä—Ź—ā—Ć—Ā—Ź —á—ā–Ķ–Ĺ–ł–Ķ–ľ —Ā–Ľ–ĺ–≤–į —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź –ł–Ľ–ł –ł—Ā–Ņ–ĺ–Ľ—Ć–∑–ĺ–≤–į—ā—Ć—Ā—Ź

–ļ–į–ļ –∑–į–Ņ—Ä–ĺ—Ā –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź –ī–Ľ—Ź –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į. –ē—Ā–Ľ–ł –ļ–ĺ–ľ–į–Ĺ–ī–į —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ–ł—Ź –Ņ—Ä–ł–Ķ–ľ–į RxEN –ĺ—ā—Ā—É—ā—Ā—ā–≤—É–Ķ—ā, —ā–ĺ —Ā–ł–≥–Ĺ–į–Ľ RxRDY –Ĺ–į—Ö–ĺ–ī–ł—ā—Ā—Ź –≤ —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł–ł —Ā–Ī—Ä–ĺ—Ā–į. –ě—ā—Ā—É—ā—Ā—ā–≤–ł–Ķ —á—ā–Ķ–Ĺ–ł—Ź –Ņ—Ä–ł–Ĺ—Ź—ā–ĺ–≥–ĺ

—Ā–ł–ľ–≤–ĺ–Ľ–į –ł–∑ –≤—č—Ö–ĺ–ī–Ĺ–ĺ–≥–ĺ —Ä–Ķ–≥–ł—Ā—ā—Ä–į –į–ī–į–Ņ—ā–Ķ—Ä–į –ī–ĺ –Ņ–ĺ—Ź–≤–Ľ–Ķ–Ĺ–ł—Ź —Ā–Ľ–Ķ–ī—É—é—Č–Ķ–≥–ĺ –≤–Ķ–ī–Ķ—ā –ļ –∑–į–≥—Ä—É–∑–ļ–Ķ

–Ĺ–ĺ–≤–ĺ–≥–ĺ —Ā–ł–ľ–≤–ĺ–Ľ–į –ł –Ņ–ĺ—ā–Ķ—Ä–Ķ —Ā—ā–į—Ä–ĺ–≥–ĺ. –£—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā—Ā—Ź –ĺ—ą–ł–Ī–ļ–į –Ņ–Ķ—Ä–Ķ–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł—Ź.

SYNDET (SYNC Detect/Break Detect) —ć—ā–ĺ—ā –≤—č–≤–ĺ–ī –≤

—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ–ĺ–ľ —Ä–Ķ–∂–ł–ľ–Ķ –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ—ā—Ā—Ź –ļ–į–ļ SYNDET –ł –ľ–ĺ–∂–Ķ—ā –Ī—č—ā—Ć

–≤—Ö–ĺ–ī–ĺ–ľ –ł–Ľ–ł –≤—č—Ö–ĺ–ī–ĺ–ľ –≤ –∑–į–≤–ł—Ā–ł–ľ–ĺ—Ā—ā–ł –ĺ—ā –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä–ĺ–≤–į–Ĺ–ł—Ź –į–ī–į–Ņ—ā–Ķ—Ä–į. –ü—Ä–ł –≤–Ĺ—É—ā—Ä–Ķ–Ĺ–Ĺ–Ķ–Ļ —Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–ł–∑–į—Ü–ł–ł —Ź–≤–Ľ—Ź–Ķ—ā—Ā—Ź –≤—č—Ö–ĺ–ī–ĺ–ľ –ł

—É—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā—Ā—Ź –ļ–į–ļ –Ņ—Ä–ł–∑–Ĺ–į–ļ –≤—č—Ź–≤–Ľ–Ķ–Ĺ–ł—Ź —Ā–ł–Ĺ—Ö—Ä–ĺ—Ā–ł–ľ–≤–ĺ–Ľ–į –≤

—Ä–Ķ–∂–ł–ľ–Ķ –Ņ—Ä–ł–Ķ–ľ–į. –ē—Ā–Ľ–ł –∑–į–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä–ĺ–≤–į–Ĺ—č –ī–≤–į —Ā–ł–Ĺ—Ö—Ä–ĺ—Ā–ł–ľ–≤–ĺ–Ľ–į,

SYNDET —É—Ā—ā–į–Ĺ–ĺ–≤–ł—ā—Ā—Ź –≤ —Ā–Ķ—Ä–Ķ–ī–ł–Ĺ–Ķ –Ņ–ĺ—Ā–Ľ–Ķ–ī–Ĺ–Ķ–≥–ĺ –Ī–ł—ā–į –≤—ā–ĺ—Ä–ĺ–≥–ĺ —Ā–ł–Ĺ—Ö—Ä–ĺ—Ā–ł–ľ–≤–ĺ–Ľ–į. –°–ł–≥–Ĺ–į–Ľ –į–≤—ā–ĺ–ľ–į—ā–ł—á–Ķ—Ā–ļ–ł —Ā–Ī—Ä–į—Ā—č–≤–į–Ķ—ā—Ā—Ź –Ņ–ĺ—Ā–Ľ–Ķ

–ĺ–Ņ–Ķ—Ä–į—Ü–ł–ł —á—ā–Ķ–Ĺ–ł—Ź —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź. –ö–ĺ–≥–ī–į –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ—ā—Ā—Ź –ļ–į–ļ –≤—Ö–ĺ–ī–Ĺ–ĺ–Ļ (—Ä–Ķ–∂–ł–ľ –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ

—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–ł–∑–į—Ü–ł–ł), –Ķ–≥–ĺ –Ņ–ĺ—Ź–≤–Ľ–Ķ–Ĺ–ł–Ķ –∑–į—Ā—ā–į–≤–Ľ—Ź–Ķ—ā –į–ī–į–Ņ—ā–Ķ—Ä –Ĺ–į—á–į—ā—Ć –Ņ—Ä–ł–Ķ–ľ –ī–į–Ĺ–Ĺ—č—Ö. –í

–į—Ā–ł–Ĺ—Ö—Ä–ĺ–Ĺ–Ĺ–ĺ–ľ —Ä–Ķ–∂–ł–ľ–Ķ –≤—č–≤–ĺ–ī –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ—ā—Ā—Ź –ī–Ľ—Ź —Ā–ł–≥–Ĺ–į–Ľ–į Break Detect, –ļ–ĺ—ā–ĺ—Ä—č–Ļ —É—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā—Ā—Ź –Ņ—Ä–ł

–Ĺ–ł–∑–ļ–ĺ–ľ —É—Ä–ĺ–≤–Ĺ–Ķ –Ĺ–į –ł–Ĺ—ā–Ķ—Ä–≤–į–Ľ–į—Ö —Ā—ā–ĺ–Ņ-–Ī–ł—ā–ĺ–≤ –≤ –ī–≤—É—Ö –Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č—Ö –Ņ–ĺ—Ā—č–Ľ–ļ–į—Ö. –°–ł–≥–Ĺ–į–Ľ

–ľ–ĺ–∂–Ķ—ā –Ī—č—ā—Ć –≤—č—Ź–≤–Ľ–Ķ–Ĺ —á—ā–Ķ–Ĺ–ł–Ķ–ľ —Ā–Ľ–ĺ–≤–į —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—Ź. –°–Ī—Ä–į—Ā—č–≤–į–Ķ—ā—Ā—Ź –Ņ—Ä–ł —Ā–Ī—Ä–ĺ—Ā–Ķ –į–ī–į–Ņ—ā–Ķ—Ä–į

–ł–Ľ–ł –≤–ĺ–∑–≤—Ä–į—Č–Ķ–Ĺ–ł–ł –≤—Ö–ĺ–ī–Ĺ–ĺ–≥–ĺ —Ā–ł–≥–Ĺ–į–Ľ–į –ļ –Ĺ–ĺ—Ä–ľ–į–Ľ—Ć–Ĺ–ĺ–ľ—É —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł—é (–Ņ–ĺ—Ź–≤–Ľ–Ķ–Ĺ–ł—é –Ķ–ī–ł–Ĺ–ł—Ü –Ĺ–į

–ł–Ĺ—ā–Ķ—Ä–≤–į–Ľ–į—Ö —Ā—ā–ĺ–Ņ-–Ī–ł—ā–ĺ–≤).

6. –ü—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä—É–Ķ–ľ—č–Ķ –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä—č –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ

–ü—Ä–ł —Ä–į–Ī–ĺ—ā–Ķ –ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–Ĺ–ĺ–Ļ

—Ā–ł—Ā—ā–Ķ–ľ—č –≤ –Ĺ–Ķ–Ļ –ł–Ľ–ł –≤–Ĺ–Ķ—ą–Ĺ–Ķ–Ļ —Ā—Ä–Ķ–ī–Ķ –Ņ—Ä–ĺ–ł—Ā—Ö–ĺ–ī—Ź—ā —Ā–ĺ–Ī—č—ā–ł—Ź, —ā—Ä–Ķ–Ī—É—é—Č–ł–Ķ –Ĺ–Ķ–ľ–Ķ–ī–Ľ–Ķ–Ĺ–Ĺ–ĺ–Ļ

—Ä–Ķ–į–ļ—Ü–ł–ł, —á—ā–ĺ –ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–ł–≤–į–Ķ—ā—Ā—Ź –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ķ–ľ –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ–ľ—č—Ö –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ –ł –Ņ–Ķ—Ä–Ķ—Ö–ĺ–ī–ĺ–ľ –ļ

–ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—é –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤ –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź. –ź–Ņ–Ņ–į—Ä–į—ā–Ĺ–ĺ –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į—é—ā—Ā—Ź —Ā–Ņ–Ķ—Ü–ł–į–Ľ–ł–∑–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č–ľ–ł

–ė–°, –Ņ—Ä–ĺ—Ā—ā–Ķ–Ļ—ą–ł–ľ–ł –ł–∑ –ļ–ĺ—ā–ĺ—Ä—č—Ö —Ź–≤–Ľ—Ź—é—ā—Ā—Ź –Ī–Ľ–ĺ–ļ–ł –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–Ĺ–ĺ–≥–ĺ –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź (Intel 8214, –ö589–ė–ö14 –ł –ī—Ä.)- –≠—ā–ł –Ī–Ľ–ĺ–ļ–ł —Ä–Ķ—ą–į—é—ā –Ĺ–Ķ—Ā–Ľ–ĺ–∂–Ĺ—č–Ķ –∑–į–ī–į—á–ł

–ĺ–Ī—Ä–į–Ī–ĺ—ā–ļ–ł –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ł—Ö –≤–Ķ–ļ—ā–ĺ—Ä–Ĺ—č—Ö –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ –Ņ—Ä–ł —Ą–ł–ļ—Ā–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č—Ö –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–į—Ö

–∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤. –Ď–ĺ–Ľ–Ķ–Ķ —Ā–Ľ–ĺ–∂–Ĺ—č–Ķ –∑–į–ī–į—á–ł —Ä–Ķ—ą–į—é—ā—Ā—Ź –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä—É–Ķ–ľ—č–ľ–ł –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–į–ľ–ł

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ (–ü–ö–ü), –≤ —á–į—Ā—ā–Ĺ–ĺ—Ā—ā–ł –ė–° Intel 8259A, –ö1810–í–Ě59. –≠—ā–ł –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä—č –Ĺ–Ķ–Ņ–ĺ—Ā—Ä–Ķ–ī—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ —Ä–Ķ–į–Ľ–ł–∑—É—é—ā

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź —Ā –ĺ–Ī—Ä–į–Ī–ĺ—ā–ļ–ĺ–Ļ 8 –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤. –° –Ņ–ĺ–ľ–ĺ—Č—Ć—é –Ĺ–Ķ—Ā–ļ–ĺ–Ľ—Ć–ļ–ł—Ö –ü–ö–ü –Ľ–Ķ–≥–ļ–ĺ –ĺ—Ä–≥–į–Ĺ–ł–∑—É—é—ā—Ā—Ź

—É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į –ĺ–Ī—Ä–į–Ī–ĺ—ā–ļ–ł –ī–ĺ 64 –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤. –ö–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä—č –ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–ł–≤–į—é—ā —Ä–į–∑–Ľ–ł—á–Ĺ—č–Ķ –≤–ł–ī—č

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ. –°–ł—Ā—ā–Ķ–ľ–į –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ –ī–ĺ–Ľ–∂–Ĺ–į –≤—č–ī–į—ā—Ć –ļ–ĺ–ľ–į–Ĺ–ī—É –Ņ–Ķ—Ä–Ķ—Ö–ĺ–ī–į –ļ —ā–ĺ–Ļ

–Ņ–ĺ–ī–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–Ķ –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź, –ļ–ĺ—ā–ĺ—Ä–į—Ź —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É–Ķ—ā –Ņ—Ä–ł–∑–Ĺ–į–Ĺ–Ĺ–ĺ–ľ—É –∑–į–Ņ—Ä–ĺ—Ā—É.

–ö–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä –í–Ě59 –ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–ł–≤–į–Ķ—ā —Ä–į–∑–Ľ–ł—á–Ĺ—č–Ķ –≤–ł–ī—č –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ:

1 –í–Ľ–ĺ–∂–Ķ–Ĺ–Ĺ—č–Ķ –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź —Ā

—Ą–ł–ļ—Ā–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č–ľ–ł –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–į–ľ–ł –≤—Ö–ĺ–ī–ĺ–≤. –ė–ľ–Ķ—é—ā—Ā—Ź 8 –≤—Ö–ĺ–ī–ĺ–≤ –∑–į–Ņ—Ä–ĺ—Ā–į –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź IR7...IR0 (–ĺ—ā –į–Ĺ–≥–Ľ–ł–Ļ—Ā–ļ–ĺ–≥–ĺ Interrupt Request). –í—č—Ā—ą–ł–Ļ

–Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā –ł–ľ–Ķ–Ķ—ā –≤—Ö–ĺ–ī IR0, –Ĺ–ł–∑—ą–ł–Ļ - —É –≤—Ö–ĺ–ī–į IR7. –í–Ľ–ĺ–∂–Ķ–Ĺ–Ĺ–ĺ—Ā—ā—Ć - –≤–ĺ–∑–ľ–ĺ–∂–Ĺ–ĺ—Ā—ā—Ć –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź –Ņ–ĺ–ī–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—č

–ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź –∑–į–Ņ—Ä–ĺ—Ā–į –ī—Ä—É–≥–ĺ–Ļ –Ņ–ĺ–ī–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ĺ–Ļ —Ā –Ī–ĺ–Ľ–Ķ–Ķ –≤—č—Ā–ĺ–ļ–ł–ľ –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–ĺ–ľ, –ļ–ĺ—ā–ĺ—Ä–į—Ź,

–≤ —Ā–≤–ĺ—é –ĺ—á–Ķ—Ä–Ķ–ī—Ć, —ā–į–ļ–∂–Ķ –ľ–ĺ–∂–Ķ—ā –Ī—č—ā—Ć –Ņ—Ä–Ķ—Ä–≤–į–Ĺ–į –Ī–ĺ–Ľ–Ķ–Ķ –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–Ĺ–ĺ–Ļ –Ņ–ĺ–ī–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ĺ–Ļ –ł

—ā.–ī. –í–ĺ–∑–ľ–ĺ–∂–Ĺ–ĺ—Ā—ā—Ć –≤–Ľ–ĺ–∂–Ķ–Ĺ–Ĺ—č—Ö –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ –ĺ–Ī–Ķ—Ā–Ņ–Ķ—á–ł–≤–į–Ķ—ā—Ā—Ź –≤–≤–Ķ–ī–Ķ–Ĺ–ł–Ķ–ľ –ļ–ĺ–ľ–į–Ĺ–ī—č EI (Enable Interrupt) –≤ –Ņ–ĺ–ī–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—č –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ. –ü—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź —Ā

—Ą–ł–ļ—Ā–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č–ľ–ł –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–į–ľ–ł —Ä–Ķ–į–Ľ–ł–∑—É—é—ā—Ā—Ź –Ņ—Ä–ĺ—Ā—ā–ĺ, –Ĺ–ĺ –∑–į–Ņ—Ä–ĺ—Ā—č –Ĺ–Ķ—Ä–į–≤–Ĺ–ĺ–Ņ—Ä–į–≤–Ĺ—č–Ķ –ł –Ņ—Ä–ł

–ł–Ĺ—ā–Ķ–Ĺ—Ā–ł–≤–Ĺ–ĺ–ľ –Ņ–ĺ—Ā—ā—É–Ņ–Ľ–Ķ–Ĺ–ł–ł –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤ —Ā –≤—č—Ā–ĺ–ļ–ł–ľ–ł –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–į–ľ–ł –∑–į–Ņ—Ä–ĺ—Ā—č —Ā –Ĺ–ł–∑–ļ–ł–ľ–ł

–Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–į–ľ–ł –ľ–ĺ–≥—É—ā –≤–ĺ–ĺ–Ī—Č–Ķ –Ĺ–Ķ –Ņ–ĺ–Ľ—É—á–ł—ā—Ć –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź.

2

–ü—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź —Ā –ļ—Ä—É–≥–ĺ–≤—č–ľ (—Ü–ł–ļ–Ľ–ł—á–Ķ—Ā–ļ–ł–ľ)

–Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–ĺ–ľ. –í —ć—ā–ĺ–ľ —Ā–Ľ—É—á–į–Ķ —É –ļ–į–∂–ī–ĺ–≥–ĺ –≤—Ö–ĺ–ī–į —ā–ĺ–∂–Ķ –Ķ—Ā—ā—Ć —Ā–≤–ĺ–Ļ –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā, –Ĺ–ĺ –Ņ–ĺ—Ā–Ľ–Ķ

–ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź –ĺ–Ĺ –ł–∑–ľ–Ķ–Ĺ—Ź–Ķ—ā—Ā—Ź –≤ –ļ—Ä—É–≥–ĺ–≤–ĺ–ľ –Ņ–ĺ—Ä—Ź–ī–ļ–Ķ —ā–į–ļ, —á—ā–ĺ –ĺ–Ī—Ā–Ľ—É–∂–Ķ–Ĺ–Ĺ—č–Ļ –≤—Ö–ĺ–ī

–Ņ–ĺ–Ľ—É—á–į–Ķ—ā –Ĺ–ł–∑—ą–ł–Ļ –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā. –Ę–į–ļ–į—Ź –ī–ł—Ā—Ü–ł–Ņ–Ľ–ł–Ĺ–į –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź —Ö–į—Ä–į–ļ—ā–Ķ—Ä–Ĺ–į –ī–Ľ—Ź

—Ā–ł—ā—É–į—Ü–ł–ł —Ā –ł—Ā—ā–ĺ—á–Ĺ–ł–ļ–į–ľ–ł, –Ĺ–Ķ –ł–ľ–Ķ—é—Č–ł–ľ–ł –Ņ—Ä–Ķ–ł–ľ—É—Č–Ķ—Ā—ā–≤ –ī—Ä—É–≥

–Ņ–Ķ—Ä–Ķ–ī –ī—Ä—É–≥–ĺ–ľ. –ó–į–Ņ—Ä–į—ą–ł–≤–į—é—Č–Ķ–Ķ –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–ĺ –Ī—É–ī–Ķ—ā –∂–ī–į—ā—Ć –≤ —Ö—É–ī—ą–Ķ–ľ —Ā–Ľ—É—á–į–Ķ

–ī–ĺ —ā–ĺ–≥–ĺ, –ļ–į–ļ 7 –ī—Ä—É–≥–ł—Ö –ł—Ā—ā–ĺ—á–Ĺ–ł–ļ–ĺ–≤ –Ī—É–ī—É—ā –ĺ–Ī—Ā–Ľ—É–∂–Ķ–Ĺ—č –Ņ–ĺ –ĺ–ī–Ĺ–ĺ–ľ—É —Ä–į–∑—É. –†–į–Ī–ĺ—ā—É —Ā

–ļ—Ä—É–≥–ĺ–≤—č–ľ –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–ĺ–ľ –ľ–ĺ–∂–Ĺ–ĺ –ł–Ľ–Ľ—é—Ā—ā—Ä–ł—Ä–ĺ–≤–į—ā—Ć –Ņ—Ä–ł–ľ–Ķ—Ä–ĺ–ľ (–†–ł—Ā—É–Ĺ–ĺ–ļ 45), –≤ –ļ–ĺ—ā–ĺ—Ä–ĺ–ľ

—Ä–Ķ–≥–ł—Ā—ā—Ä –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤ –≤–Ĺ–į—á–į–Ľ–Ķ —Ā–ĺ–ī–Ķ—Ä–∂–ł—ā 6-–Ļ –ł 4-–Ļ –∑–į–Ņ—Ä–ĺ—Ā—č, —ā.–Ķ. –Ĺ–į–ł–≤—č—Ā—ą–ł–Ļ –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā

–ł–ľ–Ķ–Ķ—ā 4-–Ļ –∑–į–Ņ—Ä–ĺ—Ā, –ļ–ĺ—ā–ĺ—Ä—č–Ļ –ł –Ī—É–ī–Ķ—ā –ĺ–Ī—Ā–Ľ—É–∂–Ķ–Ĺ. –ü–ĺ—Ā–Ľ–Ķ –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–Ĺ–ĺ—Ā—ā—Ć

–≤—Ö–ĺ–ī–ĺ–≤ –ł–∑–ľ–Ķ–Ĺ—Ź–Ķ—ā—Ā—Ź –ļ–į–ļ –Ī—č –≤—Ä–į—Č–Ķ–Ĺ–ł–Ķ–ľ –ļ–ĺ–Ľ—Ć—Ü–į, –Ņ—Ä–ł—á–Ķ–ľ –Ĺ–ĺ–ľ–Ķ—Ä 7 —Ā –Ĺ–ł–∑—ą–ł–ľ –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–ĺ–ľ

—Ā—ā–į–Ĺ–ĺ–≤–ł—ā—Ā—Ź –Ĺ–į 4-—é –Ņ–ĺ–∑–ł—Ü–ł—é —ā–ĺ–Ľ—Ć–ļ–ĺ —á—ā–ĺ –ĺ–Ī—Ā–Ľ—É–∂–Ķ–Ĺ–Ĺ–ĺ–≥–ĺ –∑–į–Ņ—Ä–ĺ—Ā–į. –ü–ĺ–∑–ł—Ü–ł—é –Ĺ–ł–∑—ą–Ķ–≥–ĺ

–Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–į –Ĺ–į–∑—č–≤–į—é—ā –ī–Ĺ–ĺ–ľ –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–Ĺ–ĺ–≥–ĺ –ļ–ĺ–Ľ—Ć—Ü–į. –ö–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–į–ľ–ł —Ä–Ķ–į–Ľ–ł–∑—É–Ķ—ā—Ā—Ź

–ľ–į—Ā–ļ–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤, –ļ–ĺ–≥–ī–į –∑–į–Ņ—Ä–Ķ—Č–į–Ķ—ā—Ā—Ź –ł—Ö –≤–ĺ—Ā–Ņ—Ä–ł—Ź—ā–ł–Ķ —Ā –Ņ–ĺ–ľ–ĺ—Č—Ć—é

—Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–ł—Ö –Ī–ł—ā–ĺ–≤ —Ä–Ķ–≥–ł—Ā—ā—Ä–į –ľ–į—Ā–ļ–ł. –ü—Ä–ł —ć—ā–ĺ–ľ –ľ–ĺ–≥—É—ā –Ī—č—ā—Ć —Ä–Ķ–į–Ľ–ł–∑–ĺ–≤–į–Ĺ—č —Ä–į–∑–Ĺ—č–Ķ

—Ā–ł—ā—É–į—Ü–ł–ł. –ě–Ī—č—á–Ĺ–ĺ–Ķ –ľ–į—Ā–ļ–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ. –ú–į—Ā–ļ–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ –ļ–į–ļ–ĺ–≥–ĺ-–Ľ–ł–Ī–ĺ –∑–į–Ņ—Ä–ĺ—Ā–į –≤–Ķ–ī–Ķ—ā –ł –ļ

–ľ–į—Ā–ļ–ł—Ä–ĺ–≤–į–Ĺ–ł—é –ī—Ä—É–≥–ł—Ö –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤ —Ā –ľ–Ķ–Ĺ—Ć—ą–ł–ľ–ł –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–į–ľ–ł.

3

–°–Ņ–Ķ—Ü–ł–į–Ľ—Ć–Ĺ–ĺ–Ķ

–ľ–į—Ā–ļ–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ. –ü—Ä–ĺ–ł—Ā—Ö–ĺ–ī–ł—ā –Ī–Ľ–ĺ–ļ–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ –≤–ĺ—Ā–Ņ—Ä–ł—Ź—ā–ł—Ź —ā–ĺ–Ľ—Ć–ļ–ĺ –ĺ–ī–Ĺ–ĺ–≥–ĺ –≤—Ö–ĺ–ī–į –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤

–Ņ—Ä–ł –ĺ—ā—Ā—É—ā—Ā—ā–≤–ł–ł –ľ–į—Ā–ļ–ł—Ä–ĺ–≤–į–Ĺ–ł—Ź –ľ–Ľ–į–ī—ą–ł—Ö –Ņ–ĺ –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā—É. –ü–ĺ—Ā–Ľ–Ķ —Ā–Ĺ—Ź—ā–ł—Ź –ľ–į—Ā–ļ–ł

–ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł–Ķ –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤ —Ā—ā–į–Ĺ–ĺ–≤–ł—ā—Ā—Ź –≤–ĺ–∑–ľ–ĺ–∂–Ĺ—č–ľ.

–†–ł—Ā. –ü—Ä–ł–ľ–Ķ—Ä –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź —Ā –ļ—Ä—É–≥–ĺ–≤—č–ľ –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–ĺ–ľ

–í–ļ–Ľ—é—á–Ķ–Ĺ–ł–Ķ –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–į

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ –≤ —Ā–ł—Ā—ā–Ķ–ľ—É –Ņ–ĺ–ļ–į–∑–į–Ĺ–ĺ –Ĺ–į —Ä–ł—Ā—É–Ĺ–ļ–Ķ 46. –ö–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä –Ņ—Ä–ł–Ĺ–ł–ľ–į–Ķ—ā –∑–į–Ņ—Ä–ĺ—Ā—č –ĺ—ā

–≤–Ĺ–Ķ—ą–Ĺ–ł—Ö —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤, –ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ—Ź–Ķ—ā, –ļ–į–ļ–ĺ–Ļ –ł–∑ –Ĺ–Ķ–∑–į–ľ–į—Ā–ļ–ł—Ä–ĺ–≤–į–Ĺ–Ĺ—č—Ö –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤ –ł–ľ–Ķ–Ķ—ā

–Ĺ–į–ł–≤—č—Ā—ą–ł–Ļ –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā, —Ā—Ä–į–≤–Ĺ–ł–≤–į–Ķ—ā –Ķ–≥–ĺ —Ā –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–ĺ–ľ —ā–Ķ–ļ—É—Č–Ķ–Ļ –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—č –ł –Ņ—Ä–ł

—Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–ł—Ö —É—Ā–Ľ–ĺ–≤–ł—Ź—Ö –≤—č–ī–į–Ķ—ā –∑–į–Ņ—Ä–ĺ—Ā –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź INT

–ī–Ľ—Ź –ú–ü. –ü–ĺ—Ā–Ľ–Ķ –Ņ–ĺ–ī—ā–≤–Ķ—Ä–∂–ī–Ķ–Ĺ–ł—Ź –∑–į–Ņ—Ä–ĺ—Ā–į –ú–ü –ī–ĺ–Ľ–∂–Ķ–Ĺ –Ņ–ĺ–Ľ—É—á–ł—ā—Ć –ĺ—ā –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–į

–ł–Ĺ—Ą–ĺ—Ä–ľ–į—Ü–ł—é, –ļ–ĺ—ā–ĺ—Ä–į—Ź —É–ļ–į–∂–Ķ—ā –Ĺ–į –Ņ–ĺ–ī–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—É, —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č—É—é –ī–į–Ĺ–Ĺ–ĺ–ľ—É

–í–£, —ā.–Ķ. –≤–Ķ–ļ—ā–ĺ—Ä –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź.

–†–ł—Ā. –°—Ö–Ķ–ľ–į –≤–ļ–Ľ—é—á–Ķ–Ĺ–ł—Ź –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–į

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ –≤ –ú–ü-—Ā–ł—Ā—ā–Ķ–ľ—É

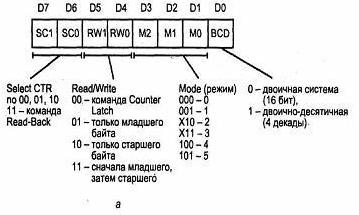

–°—ā—Ä—É–ļ—ā—É—Ä–į –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä—É–Ķ–ľ–ĺ–≥–ĺ –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–į –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ. –°—ā—Ä—É–ļ—ā—É—Ä–į –ü–ö–ü Intel 8259A –Ņ—Ä–Ķ–ī—Ā—ā–į–≤–Ľ–Ķ–Ĺ–į –Ĺ–į —Ä–ł—Ā—É–Ĺ–ļ–Ķ –Ĺ–ł–∂–Ķ. –í –į–Ĺ–≥–Ľ–ł–Ļ—Ā–ļ–ĺ–Ļ —ā–Ķ—Ä–ľ–ł–Ĺ–ĺ–Ľ–ĺ–≥–ł–ł

–ü–ö–ü –Ĺ–į–∑—č–≤–į—é—ā PIC, —ā.–Ķ. Programmable

Interrupt Controller. –ó–į–Ņ—Ä–ĺ—Ā—č

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ –ĺ—ā –í–£ –Ņ–ĺ—Ā—ā—É–Ņ–į—é—ā –Ĺ–į —Ä–Ķ–≥–ł—Ā—ā—Ä –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤ IRR,

—Ā–ĺ—Ö—Ä–į–Ĺ—Ź—é—Č–ł–Ļ –∑–į–Ņ—Ä–ĺ—Ā—č –ī–ĺ –ł—Ö –Ņ—Ä–ł–Ĺ—Ź—ā–ł—Ź –Ĺ–į –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł–Ķ. –Ď–ł—ā—č —Ä–Ķ–≥–ł—Ā—ā—Ä–į IRR —Ā–ĺ–Ņ–ĺ—Ā—ā–į–≤–Ľ—Ź—é—ā—Ā—Ź —Ā –Ī–ł—ā–į–ľ–ł —Ä–Ķ–≥–ł—Ā—ā—Ä–į –ľ–į—Ā–ĺ–ļ IMR (Interrupt Mask Register).

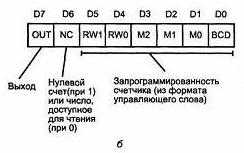

–†–ł—Ā.

–°—ā—Ä—É–ļ—ā—É—Ä–į –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä—É–Ķ–ľ–ĺ–≥–ĺ –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–į –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł–Ļ

–Ď–ł—ā—č —Ä–Ķ–≥–ł—Ā—ā—Ä–į –ľ–į—Ā–ĺ–ļ –ī–Ķ–Ļ—Ā—ā–≤—É—é—ā

—ā–į–ļ–∂–Ķ –Ĺ–į —Ä–į–Ī–ĺ—ā—É —Ā—Ö–Ķ–ľ—č –ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ–Ķ–Ĺ–ł—Ź –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–ĺ–≤ –ł —Ä–Ķ–≥–ł—Ā—ā—Ä –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź ISR, —ā–į–ļ —á—ā–ĺ –ľ–į—Ā–ļ–ł—Ä–ĺ–≤–į–Ĺ–ł–Ķ –ľ–ĺ–∂–Ķ—ā –Ī—č—ā—Ć –ĺ—Ā—É—Č–Ķ—Ā—ā–≤–Ľ–Ķ–Ĺ–ĺ –Ĺ–Ķ —ā–ĺ–Ľ—Ć–ļ–ĺ –Ĺ–į

—Ā—ā–į–ī–ł–ł –Ņ—Ä–ł–Ķ–ľ–į –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤, –Ĺ–ĺ –ł –Ĺ–į –Ī–ĺ–Ľ–Ķ–Ķ –Ņ–ĺ–∑–ī–Ĺ–ł—Ö —Ā—ā–į–ī–ł—Ź—Ö –ł—Ö –ĺ–Ī—Ä–į–Ī–ĺ—ā–ļ–ł.

–ē—Ā–Ľ–ł –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā –∑–į–Ņ—Ä–ĺ—Ā–į –≤—č—ą–Ķ

—ā–Ķ–ļ—É—Č–Ķ–≥–ĺ –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–į, —ā–ĺ –Ņ—Ä–ł –≤–Ľ–ĺ–∂–Ķ–Ĺ–Ĺ—č—Ö –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź—Ö —Ą–ĺ—Ä–ľ–ł—Ä—É–Ķ—ā—Ā—Ź —Ā–ł–≥–Ĺ–į–Ľ INT –ī–Ľ—Ź –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į. –ü—Ä–ł –Ņ–ĺ—Ā—ā—É–Ņ–Ľ–Ķ–Ĺ–ł–ł –ĺ—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į —Ā–ł–≥–Ĺ–į–Ľ–į

–Ņ–ĺ–ī—ā–≤–Ķ—Ä–∂–ī–Ķ–Ĺ–ł—Ź –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź INTA –Ņ—Ä–ł–Ĺ—Ź—ā—č–Ļ –∑–į–Ņ—Ä–ĺ—Ā –Ņ–Ķ—Ä–Ķ—Ö–ĺ–ī–ł—ā –≤

—Ä–Ķ–≥–ł—Ā—ā—Ä –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź ISR (Interrupt Servicing Register) –ł —Ā–Ī—Ä–į—Ā—č–≤–į–Ķ—ā—Ā—Ź –≤ —Ä–Ķ–≥–ł—Ā—ā—Ä–Ķ –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤ IRR. –£—Ā—ā–į–Ĺ–ĺ–≤–ļ–į –Ī–ł—ā–į ISR –∑–į–Ņ—Ä–Ķ—Č–į–Ķ—ā

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź –ĺ—ā –≤—Ā–Ķ—Ö –ī—Ä—É–≥–ł—Ö –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤ —Ā –ľ–Ķ–Ĺ—Ć—ą–ł–ľ–ł –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā–į–ľ–ł. –ü–ĺ–ī–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–į

–ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—Ź –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź –∑–į–≤–Ķ—Ä—ą–į–Ķ—ā—Ā—Ź —Ā–Ī—Ä–ĺ—Ā–ĺ–ľ –Ī–ł—ā–į —Ä–Ķ–≥–ł—Ā—ā—Ä–į ISR.

–ú–ĺ–∂–Ĺ–ĺ —ā–į–ļ–∂–Ķ –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į—ā—Ć

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź –Ņ–ĺ —Ä–Ķ–∑—É–Ľ—Ć—ā–į—ā–į–ľ –ĺ–Ņ—Ä–ĺ—Ā–į –ł—Ā—ā–ĺ—á–Ĺ–ł–ļ–ĺ–≤ –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤, –ļ–ĺ–≥–ī–į —Ā–ł–≥–Ĺ–į–Ľ INT –Ĺ–Ķ –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ—ā—Ā—Ź, –ł –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä —Ā–į–ľ –Ņ—Ä–ĺ–ł–∑–≤–ĺ–ī–ł—ā –Ņ–ĺ–ĺ—á–Ķ—Ä–Ķ–ī–Ĺ—č–Ļ

–ĺ–Ņ—Ä–ĺ—Ā –≤—Ö–ĺ–ī–ĺ–≤, –Ĺ–į—á–ł–Ĺ–į—Ź —Ā–ĺ —Ā—ā–į—Ä—ą–Ķ–≥–ĺ –Ņ–ĺ –Ņ—Ä–ł–ĺ—Ä–ł—ā–Ķ—ā—É.

–ě–Ī–Ĺ–į—Ä—É–∂–Ķ–Ĺ–ł–Ķ –∑–į–Ņ—Ä–ĺ—Ā–į –≤–Ķ–ī–Ķ—ā –ļ –Ķ–≥–ĺ –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł—é —Ā –Ņ–Ķ—Ä–Ķ—Ö–ĺ–ī–ĺ–ľ –Ĺ–į —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č—É—é

–Ņ–ĺ–ī–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—É.

–Ď—É—Ą–Ķ—Ä –®–Ē –≤–ĺ—Ā—Ć–ľ–ł—Ä–į–∑—Ä—Ź–ī–Ĺ—č–Ļ,

–ī–≤—É–Ĺ–į–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–Ĺ—č–Ļ, —Ā —ā—Ä–Ķ—ā—Ć–ł–ľ —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł–Ķ–ľ. –ü—Ä–ł –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä–ĺ–≤–į–Ĺ–ł–ł –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–į —á–Ķ—Ä–Ķ–∑

–Ĺ–Ķ–≥–ĺ –Ņ–Ķ—Ä–Ķ–ī–į—é—ā—Ā—Ź —É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł–Ķ —Ā–Ľ–ĺ–≤–į, –ł —Ā—á–ł—ā—č–≤–į–Ķ—ā—Ā—Ź —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł–Ķ —Ä–Ķ–≥–ł—Ā—ā—Ä–ĺ–≤, –į —ā–į–ļ–∂–Ķ

–ļ–ĺ–ī –∑–į–Ņ—Ä–ĺ—Ā–į, –≤—č—Ä–į–Ī–ĺ—ā–į–≤—ą–Ķ–≥–ĺ —Ā–ł–≥–Ĺ–į–Ľ INT. –ü—Ä–ł –ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į–Ĺ–ł–ł

–Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź –Ņ–ĺ —Ā–ł–≥–Ĺ–į–Ľ—É INTA —á–Ķ—Ä–Ķ–∑ –Ī—É—Ą–Ķ—Ä –®–Ē –≤ —ą–ł–Ĺ—É –ī–į–Ĺ–Ĺ—č—Ö

—Ā–ł—Ā—ā–Ķ–ľ—č –≤—č–ī–į–Ķ—ā—Ā—Ź —ā—Ä–Ķ—Ö–Ī–į–Ļ—ā–Ĺ–į—Ź –ļ–ĺ–ľ–į–Ĺ–ī–į –≤—č–∑–ĺ–≤–į –Ņ–ĺ–ī–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—č CALL.

–°–ľ—č—Ā–Ľ —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ ![]() ,

, ![]() ¬†–ł

¬†–ł ![]() , —Ź—Ā–Ķ–Ĺ (—Ā–ĺ–≤–Ņ–į–ī–į–Ķ—ā —Ā–ĺ —Ā–ľ—č—Ā–Ľ–ĺ–ľ

—ć—ā–ł—Ö —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ –≤ –ĺ–Ņ–ł—Ā–į–Ĺ–Ĺ—č—Ö –≤—č—ą–Ķ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į—Ö). –°–ł–≥–Ĺ–į–Ľ

, —Ź—Ā–Ķ–Ĺ (—Ā–ĺ–≤–Ņ–į–ī–į–Ķ—ā —Ā–ĺ —Ā–ľ—č—Ā–Ľ–ĺ–ľ

—ć—ā–ł—Ö —Ā–ł–≥–Ĺ–į–Ľ–ĺ–≤ –≤ –ĺ–Ņ–ł—Ā–į–Ĺ–Ĺ—č—Ö –≤—č—ą–Ķ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į—Ö). –°–ł–≥–Ĺ–į–Ľ ![]() ¬†–Ņ–ĺ—Ā—ā—É–Ņ–į–Ķ—ā –ĺ—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į –≤ –≤–ł–ī–Ķ —ā—Ä–Ķ—Ö

–Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č—Ö –ł–ľ–Ņ—É–Ľ—Ć—Ā–ĺ–≤, –ī–Ľ—Ź –≤—č–ī–į—á–ł –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–ĺ–ľ –ļ–ĺ–ī–į –ļ–ĺ–ľ–į–Ĺ–ī—č CALL, –ľ–Ľ–į–ī—ą–Ķ–≥–ĺ –Ī–į–Ļ—ā–į –į–ī—Ä–Ķ—Ā–į –Ĺ–į—á–į–Ľ–į –Ņ–ĺ–ī–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—č –ł —Ā—ā–į—Ä—ą–Ķ–≥–ĺ

–Ī–į–Ļ—ā–į —ć—ā–ĺ–≥–ĺ –į–ī—Ä–Ķ—Ā–į. –ü–Ķ—Ä–≤—č–Ļ –ł–ľ–Ņ—É–Ľ—Ć—Ā

¬†–Ņ–ĺ—Ā—ā—É–Ņ–į–Ķ—ā –ĺ—ā –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į –≤ –≤–ł–ī–Ķ —ā—Ä–Ķ—Ö

–Ņ–ĺ—Ā–Ľ–Ķ–ī–ĺ–≤–į—ā–Ķ–Ľ—Ć–Ĺ—č—Ö –ł–ľ–Ņ—É–Ľ—Ć—Ā–ĺ–≤, –ī–Ľ—Ź –≤—č–ī–į—á–ł –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–ĺ–ľ –ļ–ĺ–ī–į –ļ–ĺ–ľ–į–Ĺ–ī—č CALL, –ľ–Ľ–į–ī—ą–Ķ–≥–ĺ –Ī–į–Ļ—ā–į –į–ī—Ä–Ķ—Ā–į –Ĺ–į—á–į–Ľ–į –Ņ–ĺ–ī–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—č –ł —Ā—ā–į—Ä—ą–Ķ–≥–ĺ

–Ī–į–Ļ—ā–į —ć—ā–ĺ–≥–ĺ –į–ī—Ä–Ķ—Ā–į. –ü–Ķ—Ä–≤—č–Ļ –ł–ľ–Ņ—É–Ľ—Ć—Ā ![]() ¬†—Ā–Ī—Ä–į—Ā—č–≤–į–Ķ—ā –∑–į–Ņ—Ä–ĺ—Ā –≤ —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–Ķ–ľ –Ī–ł—ā–Ķ IRR.

¬†—Ā–Ī—Ä–į—Ā—č–≤–į–Ķ—ā –∑–į–Ņ—Ä–ĺ—Ā –≤ —Ā–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–Ķ–ľ –Ī–ł—ā–Ķ IRR.

–°–ł–≥–Ĺ–į–Ľ—č IR0...IR7 - –≤—Ö–ĺ–ī—č –∑–į–Ņ—Ä–ĺ—Ā–ĺ–≤ –Ņ—Ä–Ķ—Ä—č–≤–į–Ĺ–ł—Ź (Interrupt Requests), A0- –ľ–Ľ–į–ī—ą–ł–Ļ —Ä–į–∑—Ä—Ź–ī –į–ī—Ä–Ķ—Ā–į, –Ņ–ĺ–ļ–į–∑—č–≤–į–Ķ—ā, –ļ –ļ–į–ļ–ĺ–ľ—É —Ä–Ķ–≥–ł—Ā—ā—Ä—É

—É–Ņ—Ä–į–≤–Ľ—Ź—é—Č–ł—Ö —Ā–Ľ–ĺ–≤ (–£–°–ė –ł–Ľ–ł –£–°–ě) –ĺ–Ī—Ä–į—Č–į–Ķ—ā—Ā—Ź –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä. –°–ł–≥–Ĺ–į–Ľ—č CAS2-0 —Ā–≤—Ź–∑–į–Ĺ—č —Ā —Ä–į–Ī–ĺ—ā–ĺ–Ļ –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–į –≤ –≥—Ä—É–Ņ–Ņ–ĺ–≤–ĺ–Ļ —Ā—Ö–Ķ–ľ–Ķ,

–ĺ–Ī—Ä–į–∑—É—é—ā –≤—č—Ö–ĺ–ī–Ĺ—É—é —ą–ł–Ĺ—É –ī–Ľ—Ź –≤–Ķ–ī—É—Č–Ķ–≥–ĺ –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–į –ł –≤—Ö–ĺ–ī–Ĺ—É—é –ī–Ľ—Ź –≤–Ķ–ī–ĺ–ľ—č—Ö. –°–ł–≥–Ĺ–į–Ľ ![]() (

(![]() ) –ī–≤—É—Ö—Ą—É–Ĺ–ļ—Ü–ł–ĺ–Ĺ–į–Ľ—Ć–Ĺ—č–Ļ,

–ļ–į–ļ

) –ī–≤—É—Ö—Ą—É–Ĺ–ļ—Ü–ł–ĺ–Ĺ–į–Ľ—Ć–Ĺ—č–Ļ,

–ļ–į–ļ ![]() ¬†–ĺ–Ĺ –ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ—Ź–Ķ—ā, —Ź–≤–Ľ—Ź–Ķ—ā—Ā—Ź –Ľ–ł –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä –≤–Ķ–ī—É—Č–ł–ľ

–ł–Ľ–ł –≤–Ķ–ī–ĺ–ľ—č–ľ –≤ –≥—Ä—É–Ņ–Ņ–ĺ–≤–ĺ–Ļ —Ā—Ö–Ķ–ľ–Ķ, –ļ–į–ļ

¬†–ĺ–Ĺ –ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ—Ź–Ķ—ā, —Ź–≤–Ľ—Ź–Ķ—ā—Ā—Ź –Ľ–ł –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä –≤–Ķ–ī—É—Č–ł–ľ

–ł–Ľ–ł –≤–Ķ–ī–ĺ–ľ—č–ľ –≤ –≥—Ä—É–Ņ–Ņ–ĺ–≤–ĺ–Ļ —Ā—Ö–Ķ–ľ–Ķ, –ļ–į–ļ ![]() ¬†–ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ—ā—Ā—Ź –≤ —ā–į–ļ –Ĺ–į–∑—č–≤–į–Ķ–ľ–ĺ–ľ –Ī—É—Ą–Ķ—Ä–ł–∑–ĺ–≤–į–Ĺ–Ĺ–ĺ–ľ

—Ä–Ķ–∂–ł–ľ–Ķ –ī–Ľ—Ź —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ–ł—Ź –≤—č—Ö–ĺ–ī–į –Ĺ–į —ą–ł–Ĺ—É —Ā–ł—Ā—ā–Ķ–ľ—č, —ā.–Ķ. –ī–Ľ—Ź —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –≤—č—Ö–ĺ–ī–Ĺ—č–ľ–ł

–Ī—É—Ą–Ķ—Ä–į–ľ–ł —É—á–į—Ā—ā–Ĺ–ł–ļ–ĺ–≤ –ĺ–Ī–ľ–Ķ–Ĺ–į.

¬†–ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ—ā—Ā—Ź –≤ —ā–į–ļ –Ĺ–į–∑—č–≤–į–Ķ–ľ–ĺ–ľ –Ī—É—Ą–Ķ—Ä–ł–∑–ĺ–≤–į–Ĺ–Ĺ–ĺ–ľ

—Ä–Ķ–∂–ł–ľ–Ķ –ī–Ľ—Ź —Ä–į–∑—Ä–Ķ—ą–Ķ–Ĺ–ł—Ź –≤—č—Ö–ĺ–ī–į –Ĺ–į —ą–ł–Ĺ—É —Ā–ł—Ā—ā–Ķ–ľ—č, —ā.–Ķ. –ī–Ľ—Ź —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –≤—č—Ö–ĺ–ī–Ĺ—č–ľ–ł

–Ī—É—Ą–Ķ—Ä–į–ľ–ł —É—á–į—Ā—ā–Ĺ–ł–ļ–ĺ–≤ –ĺ–Ī–ľ–Ķ–Ĺ–į.

7. –ö–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä—č –Ņ—Ä—Ź–ľ–ĺ–≥–ĺ –ī–ĺ—Ā—ā—É–Ņ–į –ļ –Ņ–į–ľ—Ź—ā–ł

–ü—Ä—Ź–ľ–ĺ–Ļ –ī–ĺ—Ā—ā—É–Ņ –ļ –Ņ–į–ľ—Ź—ā–ł (–ü–Ē–ü) -

—Ā–ĺ–∑–ī–į–Ĺ–ł–Ķ –Ņ—Ä—Ź–ľ–ĺ–≥–ĺ —ā—Ä–į–ļ—ā–į –Ņ–Ķ—Ä–Ķ–ī–į—á –ī–į–Ĺ–Ĺ—č—Ö –ĺ—ā –≤–Ĺ–Ķ—ą–Ĺ–ł—Ö —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤ –ļ –Ņ–į–ľ—Ź—ā–ł –ł–Ľ–ł –ĺ—ā

–Ņ–į–ľ—Ź—ā–ł –ļ –≤–Ĺ–Ķ—ą–Ĺ–ł–ľ —É—Ā—ā—Ä–ĺ–Ļ—Ā—ā–≤–į–ľ. –í –į–Ĺ–≥–Ľ–ł–Ļ—Ā–ļ–ĺ–Ļ —ā–Ķ—Ä–ľ–ł–Ĺ–ĺ–Ľ–ĺ–≥–ł–ł —ć—ā–ĺ DMA - Direct Memory Access. –ü—Ä–ł –ĺ–Ī—č—á–Ĺ–ĺ–ľ –ĺ–Ī–ľ–Ķ–Ĺ–Ķ

–Ņ–Ķ—Ä–Ķ–ī–į—á–ł –ľ–Ķ–∂–ī—É –í–£ –ł –Ņ–į–ľ—Ź—ā—Ć—é —ā—Ä–Ķ–Ī—É—é—ā –≤–Ĺ–į—á–į–Ľ–Ķ –Ņ—Ä–ł–Ĺ—Ź—ā—Ć –ī–į–Ĺ–Ĺ—č–Ķ –ĺ—ā –ł—Ā—ā–ĺ—á–Ĺ–ł–ļ–į –≤

–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä, –į –∑–į—ā–Ķ–ľ –≤—č–ī–į—ā—Ć –ł—Ö –ł–∑ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į –Ņ—Ä–ł–Ķ–ľ–Ĺ–ł–ļ—É, —ā.–Ķ. —Ä–Ķ–į–Ľ–ł–∑—É—é—ā—Ā—Ź –∑–į –ī–≤–į

–ļ–ĺ–ľ–į–Ĺ–ī–Ĺ—č—Ö —Ü–ł–ļ–Ľ–į. –ü—Ä–ł –ü–Ē–ü –ī–į–Ĺ–Ĺ—č–Ķ –Ĺ–Ķ –Ņ—Ä–ĺ—Ö–ĺ–ī—Ź—ā —á–Ķ—Ä–Ķ–∑ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä, –ł –Ņ–Ķ—Ä–Ķ–ī–į—á–į —Ā–Ľ–ĺ–≤–į

–Ņ—Ä–ĺ–ł–∑–≤–ĺ–ī–ł—ā—Ā—Ź –∑–į –ĺ–ī–ł–Ĺ —Ü–ł–ļ–Ľ. –Ē–Ľ—Ź —Ä–Ķ–į–Ľ–ł–∑–į—Ü–ł–ł –ü–Ē–ü —Ä–į–∑—Ä–į–Ī–ĺ—ā–į–Ĺ—č —Ā–Ņ–Ķ—Ü–ł–į–Ľ—Ć–Ĺ—č–Ķ

–į–Ņ–Ņ–į—Ä–į—ā–Ĺ—č–Ķ —Ā—Ä–Ķ–ī—Ā—ā–≤–į, –≤—č–Ņ—É—Ā–ļ–į—é—ā—Ā—Ź –Ď–ė–° –ö–ü–Ē–ü, —Ā–Ņ–ĺ—Ā–ĺ–Ī–Ĺ—č–Ķ –Ī–Ľ–į–≥–ĺ–ī–į—Ä—Ź –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä–ĺ–≤–į–Ĺ–ł—é

–ĺ–Ī—Ā–Ľ—É–∂–ł–≤–į—ā—Ć –ü–Ē–ü —Ā —É—á–Ķ—ā–ĺ–ľ –ļ–ĺ–Ĺ–ļ—Ä–Ķ—ā–Ĺ—č—Ö —ā—Ä–Ķ–Ī–ĺ–≤–į–Ĺ–ł–Ļ —Ä–į–∑–Ľ–ł—á–Ĺ—č—Ö —Ā–ł—Ā—ā–Ķ–ľ.

–í–∑–į–ł–ľ–ĺ–ī–Ķ–Ļ—Ā—ā–≤–ł–Ķ –Ī–Ľ–ĺ–ļ–ĺ–≤ –ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–Ĺ–ĺ–Ļ —Ā–ł—Ā—ā–Ķ–ľ—č

–Ņ—Ä–ł –ü–Ē–ü –Ņ–ĺ–ļ–į–∑–į–Ĺ–ĺ –Ĺ–į —Ä–ł—Ā—É–Ĺ–ļ–Ķ 48. –ú–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –≤—č–Ņ–ĺ–Ľ–Ĺ—Ź–Ķ—ā –ĺ–Ņ–Ķ—Ä–į—Ü–ł—é

–Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ–ł—Ä–ĺ–≤–į–Ĺ–ł—Ź –ö–ü–Ē–ü, –Ĺ–į—Ā—ā—Ä–į–ł–≤–į—Ź –Ķ–≥–ĺ –Ĺ–į –ĺ–Ņ—Ä–Ķ–ī–Ķ–Ľ–Ķ–Ĺ–Ĺ—č–Ļ —Ä–Ķ–∂–ł–ľ —Ä–į–Ī–ĺ—ā—č, –ł –ľ–ĺ–∂–Ķ—ā

—á–ł—ā–į—ā—Ć —Ā–ĺ—Ā—ā–ĺ—Ź–Ĺ–ł–Ķ –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä–į. –°–ĺ–ĺ—ā–≤–Ķ—ā—Ā—ā–≤—É—é—Č–ł–Ķ —Ā–≤—Ź–∑–ł –Ņ–ĺ–ļ–į–∑–į–Ĺ—č —ą—ā—Ä–ł—Ö–ĺ–≤–ĺ–Ļ –Ľ–ł–Ĺ–ł–Ķ–Ļ.

–ü—Ä–ł –ĺ—Ā—É—Č–Ķ—Ā—ā–≤–Ľ–Ķ–Ĺ–ł–ł –ü–Ē–ü –ľ–ł–ļ—Ä–ĺ–Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –ĺ—ā–ļ–Ľ—é—á–Ķ–Ĺ, –į –ļ–ĺ–Ĺ—ā—Ä–ĺ–Ľ–Ľ–Ķ—Ä –≤—č—Ä–į–Ī–į—ā—č–≤–į–Ķ—ā

—Ā–ł–≥–Ĺ–į–Ľ—č —É–Ņ—Ä–į–≤–Ľ–Ķ–Ĺ–ł—Ź –ĺ–Ī–ľ–Ķ–Ĺ–ĺ–ľ –ī–Ľ—Ź –í–£ –ł –ě–ó–£. –Ę—Ä–į–ļ—ā –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –ī–į–Ĺ–Ĺ—č—Ö —Ā–≤—Ź–∑—č–≤–į–Ķ—ā –í–£ —Ā

–ě–ó–£ –Ĺ–Ķ–Ņ–ĺ—Ā—Ä–Ķ–ī—Ā—ā–≤–Ķ–Ĺ–Ĺ–ĺ.

–í–ĺ–∑–ľ–ĺ–∂–Ĺ—č –ī–≤–į –≤–ł–ī–į –ü–Ē–ü - —Ā –Ī–Ľ–ĺ—á–Ĺ—č–ľ–ł

–ł–Ľ–ł –ĺ–ī–ł–Ĺ–ĺ—á–Ĺ—č–ľ–ł –Ņ–Ķ—Ä–Ķ–ī–į—á–į–ľ–ł.

–†–ł—Ā. –°—Ö–Ķ–ľ–į –≤–∑–į–ł–ľ–ĺ–ī–Ķ–Ļ—Ā—ā–≤–ł—Ź –Ī–Ľ–ĺ–ļ–ĺ–≤ –ú–ü-—Ā–ł—Ā—ā–Ķ–ľ—č –Ņ—Ä–ł –ü–Ē–ü

–í –Ņ–Ķ—Ä–≤–ĺ–ľ —Ä–į–Ī–ĺ—ā–į –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į

–ĺ—Ā—ā–į–Ĺ–į–≤–Ľ–ł–≤–į–Ķ—ā—Ā—Ź –Ĺ–į –≤—Ā–Ķ –≤—Ä–Ķ–ľ—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á–ł –Ī–Ľ–ĺ–ļ–į –ī–į–Ĺ–Ĺ—č—Ö, –≤–ĺ –≤—ā–ĺ—Ä–ĺ–ľ –Ņ–Ķ—Ä–Ķ–ī–į—á–ł —Ā–Ľ–ĺ–≤ –≤

—Ä–Ķ–∂–ł–ľ–Ķ –ü–Ē–ü –Ņ–Ķ—Ä–Ķ–ľ–Ķ–∂–į—é—ā—Ā—Ź —Ā –≤—č–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł–Ķ–ľ –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—č, –ł –ī–Ľ—Ź –Ņ–Ķ—Ä–Ķ–ī–į—á –ü–Ē–ü –≤—č–ī–Ķ–Ľ—Ź—é—ā—Ā—Ź

–ĺ—ā–ī–Ķ–Ľ—Ć–Ĺ—č–Ķ —ā–į–ļ—ā—č –ľ–į—ą–ł–Ĺ–Ĺ—č—Ö —Ü–ł–ļ–Ľ–ĺ–≤, –≤ –ļ–ĺ—ā–ĺ—Ä—č—Ö –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä –Ĺ–Ķ –ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É–Ķ—ā —Ā–ł—Ā—ā–Ķ–ľ–Ĺ—č–Ķ

—ą–ł–Ĺ—č. –ö–į–∂–ī—č–Ļ –ļ–ĺ–ľ–į–Ĺ–ī–Ĺ—č–Ļ —Ü–ł–ļ–Ľ –Ĺ–į—á–ł–Ĺ–į–Ķ—ā—Ā—Ź —Ā –ľ–į—ą–ł–Ĺ–Ĺ–ĺ–≥–ĺ —Ü–ł–ļ–Ľ–į Ml - –≤—č–Ī–ĺ—Ä–ļ–ł –ļ–ĺ–ľ–į–Ĺ–ī—č. –í —ć—ā–ĺ–ľ –ľ–į—ą–ł–Ĺ–Ĺ–ĺ–ľ —Ü–ł–ļ–Ľ–Ķ –Ķ—Ā—ā—Ć —ā–į–ļ—ā

–ī–Ķ–ļ–ĺ–ī–ł—Ä–ĺ–≤–į–Ĺ–ł—Ź –Ņ—Ä–ł–Ĺ—Ź—ā–ĺ–Ļ –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–ĺ–ľ –ļ–ĺ–ľ–į–Ĺ–ī—č, –≤ –ļ–ĺ—ā–ĺ—Ä–ĺ–ľ —Ā–ł—Ā—ā–Ķ–ľ–Ĺ—č–Ķ —ą–ł–Ĺ—č –Ĺ–Ķ

–ł—Ā–Ņ–ĺ–Ľ—Ć–∑—É—é—ā—Ā—Ź. –Ě–į —ć—ā–ĺ –≤—Ä–Ķ–ľ—Ź —Ā–ł—Ā—ā–Ķ–ľ–Ĺ—č–Ķ —ą–ł–Ĺ—č –ľ–ĺ–∂–Ĺ–ĺ –ĺ—ā–ī–į—ā—Ć –ī–Ľ—Ź –ü–Ē–ü –ł –Ņ–Ķ—Ä–Ķ–ī–į—ā—Ć –ĺ–ī–Ĺ–ĺ

—Ā–Ľ–ĺ–≤–ĺ. –ü—Ä–ĺ–ł–∑–≤–ĺ–ī–ł—ā–Ķ–Ľ—Ć–Ĺ–ĺ—Ā—ā—Ć —Ā–ł—Ā—ā–Ķ–ľ—č –ľ–ĺ–∂–Ķ—ā –≤–ĺ–∑—Ä–į—Ā—ā–ł –ł–∑-–∑–į –Ņ–į—Ä–į–Ľ–Ľ–Ķ–Ľ–ł–∑–ľ–į –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ–≤

–ĺ–Ī–ľ–Ķ–Ĺ–į –ł –ĺ–Ī—Ä–į–Ī–ĺ—ā–ļ–ł –ī–į–Ĺ–Ĺ—č—Ö, –Ī–Ľ–į–≥–ĺ–ī–į—Ä—Ź —ā–ĺ–ľ—É, —á—ā–ĺ –ü–Ē–ü –Ī—É–ī–Ķ—ā –ī–Ľ—Ź –Ņ—Ä–ĺ—Ü–Ķ—Ā—Ā–ĺ—Ä–į

"–Ĺ–Ķ–≤–ł–ī–ł–ľ—č–ľ". –°–į–ľ –ĺ–Ī–ľ–Ķ–Ĺ —Ā –ü–Ē–ü –Ī—É–ī–Ķ—ā –Ĺ–Ķ –Ī—č—Ā—ā—Ä—č–ľ, —ā–Ķ–ľ–Ņ –ĺ–Ī–ľ–Ķ–Ĺ–į

–Ĺ–Ķ—Ä–Ķ–≥—É–Ľ—Ź—Ä–Ķ–Ĺ, —ā.–ļ. –ī–Ľ–ł—ā–Ķ–Ľ—Ć–Ĺ–ĺ—Ā—ā–ł —Ü–ł–ļ–Ľ–ĺ–≤ —Ä–į–∑–Ľ–ł—á–Ĺ—č—Ö –ļ–ĺ–ľ–į–Ĺ–ī —Ä–į–∑–Ľ–ł—á–Ĺ—č, –ł, –ļ—Ä–ĺ–ľ–Ķ —ā–ĺ–≥–ĺ,

–ü–Ē–ü –ľ–ĺ–∂–Ķ—ā –ł –∑–į–ľ–Ķ–ī–Ľ–ł—ā—Ć –≤—č–Ņ–ĺ–Ľ–Ĺ–Ķ–Ĺ–ł–Ķ –Ņ—Ä–ĺ–≥—Ä–į–ľ–ľ—č, –Ķ—Ā–Ľ–ł —Ü–ł–ļ–Ľ –ü–Ē–ü –Ĺ–Ķ —É–Ľ–ĺ–∂–ł—ā—Ā—Ź –≤