Однокристальные

микро-ЭВМ (Лекция)

ПЛАН ЛЕКЦИИ

– Введение

– Общие сведения об однокристальных микроЭВМ семейства МК48

– Однокристальные микро-ЭВМ семейства МК51

– Структура микроконтроллеров семейства MCS-x96

– Периферийные устройства микроконтроллеров семейства

MCS-x96

Введение

В микропроцессорной технике выделился самостоятельный класс

больших интегральных схем (БИС) -

однокристальные микроЭВМ (микроконтроллеры), которые предназначены для

"интеллектуализации" оборудования различного технологического назначения. Архитектура однокристальных микроЭВМ - результат эволюции архитектуры

микропроцессоров и микропроцессорных систем, обусловленный стремлением

существенно снизить их аппаратные затраты и стоимость.

Однокристальные

микроЭВМ представляют собой приборы, конструктивно выполненные в виде

одной БИС и включающие в себя все устройства, необходимые для реализации

цифровой системы управления минимальной

конфигурации: процессор, запоминающее устройства данных, запоминающее устройство

команд, внутренний генератор тактовых

сигналов, а также программируемые

схемы для связи

с внешней средой.

Использование однокристальных микроЭВМ в

системах управления обеспечивает

достижение исключительно высоких показателей эффективности при столь низкой

стоимости, что им, видимо, нет в

ближайшем времени альтернативной элементной

базы для построения управляющих и/или регулирующих

систем.

Отечественная микроэлектронная промышленность освоила

широкомасштабный выпуск однокристальных микроЭВМ, к числу которых можно отнести

4-битные микроконтроллеры серий 1814, 1820,

1829 и 1013; 8-битные микроЭВМ

серии 1816; микроконтроллеры сигнальные (аналоговые микропроцессоры) серии

1813. В данном курсе в качестве базовых выбраны однокристальные микроЭВМ (ОМЭВМ)

серии 1816. В настоящее

время в состав этой серии входят

два семейства ОМЭВМ МК48 и МК51.

Общие

сведения об однокристальных микроЭВМ семейства МК48

Семейство МК48 включает

ряд моделей ОМЭВМ,

функциональный состав и технические характеристики которых отражают как

различные в идеологическом подходе

к применению ОМЭВМ,

так и прогрессе технологии СБИС. Все модели,

входящие в семейство МК48, являются полностью совместимыми по системе

команд. назначению и

разводке выводов, совокупности основных функциональных устройств

из базового набора семейств.

Первое поколение отечественных

ОМЭВМ семейства МК48 - БИС КР1816ВЕ48 и

КР1816ВЕ35 являются функционально-конструктивными аналогами БИС

соответственно 8748 и 8035 фирмы

Intel (США), выполнены по

n-канальной МОП-технологии, что обусловило следующие ограничения: уровень

интеграции до 18

тыс. транзисторов на кристалле, частота следования тактовых

сигналов - 6.0 МГц, объем внутренней

памяти ОЗУ - 64 байта, ППЗУ - 1 кбайт

и минимальное время цикла - 2,5

мкс.

Второе поколение - БИС КР1816ВЕ49,

КР1816ВЕ39 (аналоги БИС 8049 и 8039 фирмы Intel) выполнено по

n-канальной МОП-технологии с пропорциональным масштабированием, что

позволило повысить уровень интеграции до

36 тыс. транзисторов на кристалле, частоту

следования тактовых сигналов до 11МГц, увеличить объем ОЗУ до 128

байт, ПЗУ до 2 кбайт и снизить минимальное время цикла до 1,36 мкс.

Третье поколение семейства МК48

- БИС ОМЭВМ

серии КР1830: КР1830ВЕ48,

КР1830ВЕ35 (аналоги БИС

80С48, 80С35 фирмы

Intel) выполнено по КМОП-технологии, что позволило на

порядок уменьшить ток потребления

по сравнению с БИС

КР1816 ВЕ48, КР1816ВЕ35

при сохранении остальных параметров.

ОМЭВМ КР1816ВЕ48, КР1816ВЕ35, КР1830ВЕ48 и КР1830ВЕ35

полностью идентичны в части

структурной реализации. При этом

в БИС КМ1816ВЕ48 программная

память размещается во внутреннем

ППЗУ с ультрафиолетовым (УФ)

стиранием, а в

БИС КР1830ВЕ48 - во

внутреннем ПЗУ масочного

типа. Таким образом,

оперативность программирования ППЗУ позволяет использовать ОМЭВМ

КР1816ВЕ48 при создании контроллеров

единичных экземпляров или

мелкосерийных изделий. Потребители БИС КР1830ВЕ48 лишены такой

возможности, так как программирование

ПЗУ осуществляется в процессе

изготовления БИС по данным "прошивки" заказа потребителя.

В микросхемах КР1816ВЕ35

и КР1830ВЕ35 в

отличие от БИС КМ1816ВЕ48, КР1830ВЕ48 память программ реализуется только за счет подключения внешней памяти любого типа

(ОЗУ, ППЗУ, ПЗУ)

общим объемом до 4 кбайт. Эта особенность позволяет использовать

их в качестве отладочного

варианта, когда память программ реализуется в ОЗУ, что позволяет легко

модифицировать отлаживание программ.

ОМЭВМ КР1816ВЕ49 и КР1816ВЕ39 имеют одну и

ту же структуру, одинаковые схемотехнические

решения и технические характеристики, за

исключением памяти программ: ОМЭВМ КР1816ВЕ49 имеет внутреннюю память программы объемом 2 кбайт,

выполненную в виде масочного ПЗУ, а ОМЭВМ

КР1816ВЕ39 может использоваться только

с внешним ЗУ программ.

Реализация

программной памяти КР1816ВЕ49

в виде ПЗУ обуславливает целесообразность

применения этих ОМЭВМ только

для изделий средне- и крупносерийного производства, что обеспечивает в

этом случае низкую стоимость ОМЭВМ. В качестве отладочной модели, а также при разработке единичных

экземпляров изделий целесообразно использовать ОМЭВМ КР1816ВЕ39 с внешней

памятью программ.

В общем

виде основные отличительные особенности ОМЭВМ

семейства МК48 представлены в таблице 1.

Таблица

1

|

Микро- схемы |

Аналог |

Объем внутр. памяти |

Тип памяти программ |

Объем Памяти Данных |

Макс. частота след.тактовых сигналов |

Ток потреб- ления |

|

|

|

|

|

байт |

МГц |

мА |

|

КР1826ВЕ35 КР1816ВЕ48 КР1816ВЕ39 КР1816ВЕ49 КР1830ВЕ35 КР1830ВЕ48 |

8035 8748 8039 8049 80С35 80С48 |

НЕТ 1К НЕТ 1К НЕТ 1К |

ВНЕШН. УФППЗУ ВНЕШН. ПЗУ ВНЕШН. ПЗУ |

64 64 128 128 64 64 |

6.0 6.0 11.0 11.0 64 64 |

135.0 135.0 110.0 110.0 8.0 8.0 |

В ОМЭВМ предусмотрена возможность

расширения памяти программ до 4 кбайт, памяти данных до 384 байт и увеличения

числа линий ввода вывода за счет подключения

внешних кристаллов памяти программ, ОЗУ и БИС интерфейсов.

Однокристальные

микро-ЭВМ семейства МК51

8-разрядные

высокопроизводительные однокристальные микроЭВМ семейства МК51 выполнены по высококачественной n-МОП-технологии

(серия 1816) и КМОП-технологии (серия 1830).

Использование

ОМЭВМ семейства МК51

по сравнению с

МК48 обеспечивает увеличение объема памяти программ и памяти

данных. Новые возможности ввода-вывода и периферийных устройств расширяют диапазон применения и снижают общие

затраты системы. В зависимости от условий

использования,

быстродействие системы увеличивается минимум в два с половиной раза

и максимум на порядок.

Семейство МК51 включает

пять модификаций ОМЭВМ

(имеющих идентичные основные характеристики), различающиеся

реализацией памяти программ и мощностью энергопотребления.

ОМЭВМ КР1816ВЕ51 и КР1830ВЕ57 содержат масочно-программируемое

в процессе изготовления кристалла ПЗУ памяти программ емкостью

4 кбайт и рассчитаны на применение

в массовой продукции.

За счет использования внешних микросхем

памяти общий объем памяти программ может

быть расширен до 64 кбайт.

ОМЭВМ КМ1816ВЕ751 содержит ППЗУ емкостью 4 кбайт с УФ

стиранием и удобна на этапе разработки системы при

отладке программ, а также при производстве небольшими партиями

или при создании

систем, требующих в процессе

эксплуатации периодической подстройки.

За счет использования внешних

микросхем памяти общий

объем памяти программ может быть

расширен до 64 кбайт.

ОМЭВМ КР1816ВЕ31 и КР1830ВЕ31 не

содержат встроенной памяти программ, однако могут использовать до

64 кбайт внешней постоянной или перепрограммируемой памяти программ и

эффективно использоваться в системах, требующих существенно большего по объему

(более чем 4 кбайт на кристалле) ПЗУ

памяти программ.

Каждая из перечисленных выше микросхем является соответственно аналогом БИС 8051, 80С51,

8751, 8031, 80С31 семейства МСS-51 фирмы Intel (США).

Сравнительные данные микросхем

МК51 приведены в таблице 2.

Таблица

2

|

Микро- схемы |

Аналог |

Объем внутр. памяти |

Тип памяти программ |

Объем памяти данных |

Макс. частота след. тактов. сигналов |

Ток потреб-ления |

|

|

|

байт |

|

байт |

МГц |

мА |

|

КР1826ВЕ31 КР1816ВЕ51 КР1816ВЕ751 КР1830ВЕ31 КР1830ВЕ51 |

8031АН 8051АН 8751Н 80С31ВН 80С51ВН |

НЕТ 4К 4К НЕТ 4К |

ВНЕШН. ПЗУ ППЗУ ВНЕШН. ПЗУ |

128 128 128 128 128 |

12.0 12.0 12.0 12.0 12.0 |

150.0 150.0 220.0 18.0 18.0 |

Каждая ОМЭВМ рассматриваемого семейства содержит встроенное

ОЗУ памяти данных емкостью 128 байт с возможностью расширения

общего объема оперативной памяти данных до 64 Кбайт за счет

использования внешних микросхем ЗУПВ.

Общий объем памяти ОМЭВМ семейства МК51 может

достигать 128 Кбайт: 64 Кбайт

памяти программ и 64 Кбайт памяти данных.

ОМЭВМ МК51 выполнены

на основе высокоуровневой n-МОП-технологии и

выпускаются в корпусе типа DIР, имеющем 40 внешних

выводов. ОМЭВМ данного семейства

содержат следующие основные узлы:

1. центральный 8-разрядный процессор;

2. память программ объемом 4 Кбайт;

3. память данных объемом 128 байт;

4. четыре 8-разрядных программируемых канала ввода-вывода;

5. два 16-битовых многорежимных таймера/счетчика;

6. систему прерываний с пятью векторами и двумя уровнями;

7. последовательный интерфейс;

8. тактовый генератор.

Система команд ОМЭВМ содержит 111

базовых команд с

форматом 1,2 или 3 байта.

ОМЭВМ имеет: 32 РОН; 128

определяемых пользователем программно-управляемых флагов; набор регистров

специальных функций.

РОН и определяемые

пользователем

программно-управляемые флаги

расположены в адресном

пространстве внутреннего ОЗУ

данных.

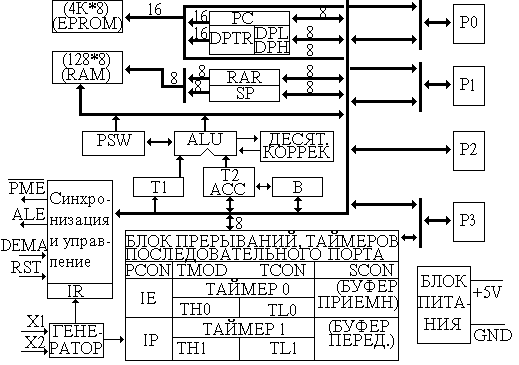

Структурная схема

ОМЭВМ представлена на

рис.10. Основу структурной схемы

МК51 составляет внутренняя

двунаправленная 8-битовая шина, которая связывает между собой все

основные узлы и устройства: арифметико-логическое устройство (АЛУ),

резидентную память, блок регистров специальных функций, устройство управления и порты ввода-вывода.

Устройство управления МК51 на основе сигналов синхронизации

формирует машинный цикл фиксированной длительности, равной 12 периодам

кварцевого резонатора или шести состояниям первичного управляющего автомата

(S1-S6). Каждое состояние управляющего автомата содержит две фазы (Р1, Р2) сигналов резонатора. В фазе Р1,

как правило, выполняется операция в АЛУ, а в фазе Р2 осуществляется

межрегистровая передача. Весь машинный цикл состоит из 12 фаз, начиная с фазы

S1P1 и кончая фазой S6P2.

Арифметико-логическое

устройство. 8-битное АЛУ может выполнять арифметические операции сложения, вычитания, умножения и деления,

логические операции И, ИЛИ, исключающее ИЛИ, а также

операции циклического сдвига,

сброса, инвертирования и т.п. В

АЛУ имеются программно-недоступные регистры

Т1 и Т2, предназначенные для временного

хранения операндов, схема

десятичной коррекции и схема формирования признаков.

Важной особенностью АЛУ является его способность

оперировать не только байтами, но и битами. Отдельные программно-доступные биты могут

быть установлены, сброшены,

инвертированы, переданы,

проверены и использованы в логических операциях. Вследствие этого, МК51 иногда

называют "булевским процессором".

Таким образом, АЛУ может оперировать

четырьмя типами объектов:

булевскими (1 бит),

цифровыми (4 бита),

байтовыми (8 бит), адресными (16 бит).

Резидентная

память. Резидентная память МК51 включает

в себя память программ (РПП) и память данных (РПД). РПП и РПД физически и

логически разделены, имеют

различные механизмы адресации,

работают под управлением различных сигналов и выполняют

разные функции.

РПП имеет емкость 4Кбайта

и предназначена для хранения

команд, констант, управляющих слов инициализации и т.п. Она имеет 16-битную шину адреса, по которой обеспечивается доступ

из счетчика команд (РС) или из

регистра указателя данных

(DРЕR). Последний выполняет функции базового регистра при косвенных

переходах.

РПД (ОЗУ) предназначена для

хранения переменных в

процессе выполнения прикладной программы, адресуется одним байтом и

имеет емкость 128 байт.

Кроме того, к

адресному пространству РПД примыкают адреса регистров

специальных функций (SFR).

Рис.10.

Структурная схема ОМЭВМ

На рис. 10. приняты следующие обозначения для управляющих

сигналов:

/PME- разрешение внешней памяти программ, сигнал выдается

только при обращении к внешней памяти программ;

ALE - строб адреса

внешней памяти, сигнал используется для приема и фиксации адреса внешней памяти

на внешнем регистре;

DEMA - блокирование работы с внутренней памятью, отключение

резидентной памяти программ;

RST - сигнал общего сброса, служит также выводом резервного

питания ОЗУ от внешнего источника;

Х1, Х2 - выводы для подключения

кварцевого резонатора.

РПП и РПД могут быть расширены до 64

Кбайт путем подключения внешних БИС.

Регистры

аккумулятора и PSW (регистр признаков операций). Аккумулятор

является источником операнда

и местом фиксации результата при выполнении

арифметических, логических операций

и ряда операций передачи данных.

При выполнении многих команд в АЛУ формируется

ряд признаков операций (флагов),

которые фиксируются в

регистре РSW.

Регистры указатели. 8-битный

указатель стека (SР) может адресовать

любую область РПД. Его

содержимое инкрементируется прежде,

чем данные будут запомнены в

стеке в ходе

выполнения команды РUSН и

САLL. Содержимое SР декрементируется после

выполнения команд RЕТ и РОР. Подобный

способ адресации элементов

стека называют прединкрементным/постинкрементным.

Двухбайтовый регистр указатель данных

(DРТR)

обычно используется для фиксации

16-битного адреса в операциях с

обращением к внешней памяти. DРТR может быть использован

или как 16-битный регистр, или как два независимых

8-битных регистра (DРН и DРL).

Буфер

последовательного порта. Регистр с символическим именем

SВUF

представляет собой два независимых регистра

- буфер приемника

и буфер передатчика. Загрузка байта в SВUF

автоматически вызывает начало

процесса передачи через последовательный порт.

Когда байт считывается из SВUF,

это значит, что его источником является

приемник последовательного порта.

Блок

таймеров/счетчиков. В составе средств МК51

имеются регистровые пары

с символическими именами

ТН0,

ТL0 и ТН1, ТL1,

на основе которых функционируют два

независимых

программно-управляемых 16-битных

таймера/счетчика событий. Таймеры/счетчики (Т/С)

предназначены для подсчета

внешних событий, для получения программно-управляемых временных задержек

и выполнения время-задающих

функций ОМЭВМ.

В состав блока Т/С входят:

два 16-разрядных регистра Т/С0 и Т/С1;

8-разрядный регистр режимов Т/С (ТМОD); 8-разрядный регистр управления

(ТСОN); схема инкремента; схема фиксации INT0, INT1, T0, T1; схема управления флагами.

16-разрядные регистры Т/С выполняют функцию

хранения содержимого счета. Код

начального счета заносится в указанные

регистры программно. В

процессе счета содержимое

регистров инкрементируется.

Признаком окончания счета является переполнение регистров.

Регистр ТМОD хранит код,

определяющий:

- один из 4-х возможных режимов работы каждого Т/С;

- работу в качестве таймеров или счетчиков;

- управление Т/С от внешнего

вывода.

Регистр ТСОN предназначен для

приема и хранения кода управляющего слова

При работе в качестве таймера содержимое Т/С инкрементируется в каждом машинном цикле, т.е. через

каждые 12 периодов резонатора. При работе в качестве счетчика

содержимое Т/С инкрементируется под воздействием перехода

из 1 в

0 внешнего входного

сигнала, подаваемого на соответствующий (Т0, Т1)

выводы МК51. Опрос значения внешнего входного сигнала

выполняется в момент

времени S5Р2 каждого машинного цикла. Содержимое счетчика будет увеличено на 1 в том случае, если в предыдущем

цикле был считан

входной сигнал высокого уровня (1), а в следующем - сигнал низкого уровня (0).

Новое (инкрементированное) значение

счетчика будет сформировано в

момент S3Р1 в цикле, следующем за тем, в

котором был обнаружен переход сигнала из 1 в 0. Так как на

распознавание перехода требуется два машинных цикла,

то максимальная частота подсчета входных

сигналов равна 1/24

частоты резонатора. На длительность периода входных сигналов

ограничений сверху нет. Для

гарантированного прочтения входного считываемого сигнала он должен удерживать

значение 1 как минимум в течении одного машинного

цикла МК51.

Режим работы 0,1 и 2 для обоих Т/С

одинаковы. Режим 3 для Т/С0 и Т/С1 различны.

Рассмотрим кратко работу Т/С во

всех режимах.

В режиме 0 таймерный регистр имеет

разрядность 13 бит.

При переходе из состояния "все единицы" в состояние

"все нули" устанавливается флаг прерывания от

таймера ТF. Входной

синхросигнал таймера разрешен (поступает на вход Т/С), когда управляющий

бит ТR установлен в 1 и либо управляющий бит GАТЕ (блокировка) равен

0, либо на внешний вывод запроса прерывания INТ

поступает уровень 1.

Отметим

попутно, что установка

бита GАТЕ в

1 позволяет использовать таймер

для измерения длительности импульсного сигнала, подаваемого на вход

запроса прерывания.

Работа любого Т/С в режиме 1 такая же,

как и в

режиме 0, за исключением того, что таймерный

регистр имеет разрядность 16 бит.

В режиме 2 работа организована таким образом, что переполнение 8-битного счетчика ТL приводит не только к установке флага ТF, но и автоматически перезагружает в ТL содержимое старшего байта

ТН таймерного

регистра, которое предварительно было

задано программным путем.

Т/С1 в

режиме 3 заблокирован и просто сохраняет значение кода в регистре Т/С.

Т/С0 в режиме 3 представляет собой

два независимых устройства на основе 8-ми разрядных регистров

ТL0 и ТН0. Устройство на основе ТL0 может работать в режиме таймера и в

режиме счетчика, за ним

сохраняются все биты управления Т/С0, оно реагирует на

воздействия по входам Т0, INТ0. При переполнении ТL0 устанавливается флаг ТF0.

Устройство на основе регистра ТН0 может работать

только в

режиме таймера. Оно использует бит включения ТR1, при

переполнении ТН0

выставляет флаг ТF1.

Порты. Порты Р0, Р1,

Р2, Р3 являются

двунаправленными портами

ввода-вывода и предназначены

для обмена информацией

ОМЭВМ с внешними устройствами,

образуя 32 линии ввода-вывода. Каждый

из портов содержит фиксатор-защелку, который представляет собой 8-ми разрядный регистр,

имеющий байтовую и

битовую адресацию для установки (сброса) разрядов с помощью

программного обеспечения.

Помимо работы в

качестве обычных портов

ввода-вывода линии портов Р0-Р3

могут выполнять ряд дополнительных функций.

Через порт Р0:

- выводится младший байт

адреса А0-А7 при

работе с внешней памятью программ и внешней памятью

данных;

- выдается и принимается байт данных при работе с внешней

памятью (при этом обмен байтом данных

и вывод младшего

байта адреса внешней памяти

мультиплексируются по времени);

- задаются данные

при программировании внутреннего

ППЗУ и

читается содержимое внутренней памяти программ.

Через порт Р1:

- задается младший байт адреса при программировании внутреннего ППЗУ и при чтении внутренней

памяти программ.

Через порт Р2:

- выводится старший байт адреса

А8-А15 при работе с ВПП и ВПД;

- задается старший байт адреса (А8-А14) при

программировании внутреннего ППЗУ и при

чтении внутренней памяти программ.

Каждая линия порта Р3 имеет индивидуальную альтернативную

функцию. Альтернативная функция любой из линий порта Р3 реализуется только в том случае, если в соответствующем

этой линии разряде фиксатора защелки содержится "1". В противном

случае на линии порта будет присутствовать "0".

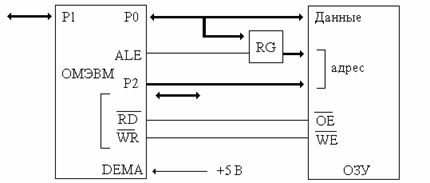

Организация

обращения к ВПД. В ОМЭВМ

предусмотрена возможность расширения

памяти данных путем подключения

внешних устройств емкостью до 64 Кбайт.

Команды ОМЭВМ могут формировать 8-разрядный адрес ВПД,

который выдается через порт Р0, либо

16-разрядный адрес, младший

байт которого выдается через порт

Р0, а старший - через порт Р2. Байт

адреса, выдаваемый через порт Р0, должен быть

зафиксирован во внешнем регистре по спаду сигнала АLЕ, т.к. в дальнейшем линии порта Р0 используются как шина данных,

через которую байт данных принимается из памяти при чтении или

выдается в память данных

при записи. При этом чтение стробируется

сигналом RD, а

запись - сигналом WR. Схема

подключения внешней памяти

данных к ОМЭВМ показана на рис.11.

Пространства внутренней и

внешней памяти данных

не пересекаются, т.к. доступ к

ним осуществляется с помощью разных команд. Т.о. в системе могут одновременно присутствовать внутренняя

память данных с адресом 00Н-FFН

и внешняя память

данных с адресом 0000Н-FFFFН. Обращение к

ячейкам ВПД осуществляется только

с использованием косвенной адресации по регистрам R0 и R1 активного банка регистров

внутреннего ОЗУ или

по регистру специальных функций DРТR.

Соответственно в первом случае

будет формироваться 8-разрядный

адрес ВПД.

Рис.11. Схема подключения внешней памяти данных к ОМЭВМ

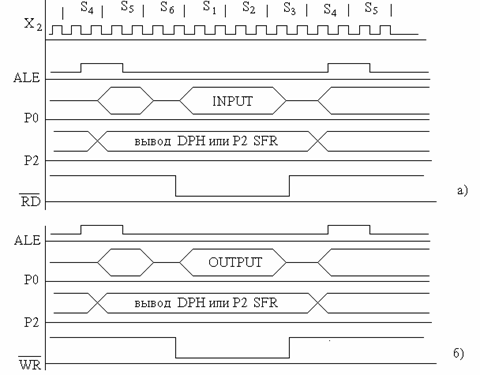

На рис.12а, 12б, соответственно, приведены

диаграммы циклов чтения и записи при

работе ОМЭВМ с внешней памятью данных.

DРL, DРН

- соответственно младший и

старший байты регистра указателя данных DРТR, который

используется в качестве

регистра косвенного адреса. R0

- регистр R 0

текущего банка, который используется в качестве регистра

косвенного адреса.

Р2SFR - защелка порта Р2.

Рис.12. Диаграммы циклов чтения и записи при работе ОМЭВМ с внешней памятью данных

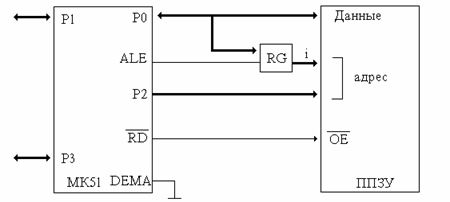

Память

программ. Память программ

предназначена для хранения кодов

программ и имеет отдельное от

памяти данных адресное пространство объемом

до 64 Кбайт, причем для БИС

1816ВЕ51, 1816ВЕ75 и

1830ВЕ51 часть

памяти программ с адресами 0000Н-0FFFН

расположена на кристалле ОМЭВМ. Если на вывод DЕМА подано

напряжение Uсс ,

то обращение к ВПП

происходит автоматически при

выработке счетчиком команд адреса, превышающего 0FFFН.

Если на вывод DЕМА подан "0", внутренняя

память программ отключается и

начиная с адреса 0000Н все

обращения выполняются только к

внешней памяти программ.

Чтение из внешней памяти программ стробируется сигналом

ОМЭВМ XOR(РМЕ). При работе с

внутренней памятью программ

сигнал XOR(РМЕ)

не формируется.

При обращении к

ВПП всегда формируется

16-разрядный адрес, младший байт

которого выдается через порт Р0, а старший - через

порт Р2. При этом байт адреса, выдаваемый через порт Р0, должен

быть зафиксирован во внешнем регистре по

спаду сигнала АLЕ,

т.к. в дальнейшем линии порта Р0

используются в качестве шины данных, по

которой байт из внешней памяти программ вводится в ОМЭВМ.

Функциональная схема включения

ОМЭВМ МК51 с ВПП

показана на рис.13.

Рис.13. Функциональная схема включения ОМЭВМ МК51 с ВПП

Порт Р0 работает как

мультиплексированная шина адрес/данные: выдает младший

байт счетчика команд,

а затем переходит

в высокоимпедансное состояние

и ожидает прихода

байта из ППЗУ программ. Когда младший байт адреса

находится на выходах порта Р0, сигнал ALЕ защелкивает

его в адресном режиме

RG. Старший байт адреса находится на выходах порта

P2 в течение

всего времени обращения к ППЗУ.

Сигнал XOR(РМЕ) разрешает

выборку байта из

ППЗУ, после чего выбранный байт поступает на порт Р0

МК51 и вводится в ОМЭВМ.

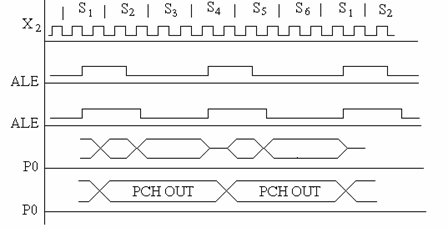

Диаграммы, показывающие формирование соответствующих сигналов при работе ОМЭВМ с ВПП,

приведены на рис.14.

Рис.14. Диаграммы, показывающие формирование соответствующих сигналов при работе ОМЭВМ с ВПП

На рис.14. использованы следующие

обозначения:

- РСL

ОUТ - выдача младшего байта РС;

- РСН ОUТ

- выдача старшего байта РС;

-INРUТ - данные на шине Р0.

Как видно из диаграмм, при работе

с ВПП сигнал РМЕ формируется дважды в

каждом машинном цикле независимо от количества

байт в команде. Если

второй выбираемый байт в текущей

команде не используется, он

игнорируется ОМЭВМ. В дальнейшем, при переходе

к выполнению следующей команды этот байт будет введен вторично.

Структура микроконтроллеров семейства MCS-x96

Семейство микроконтроллеров MCS-x96 предназначено специально для

построения высокопроизводительных контроллеров, реализующих алгоритмы

управления исполнительными двигателями постоянного и переменного тока.

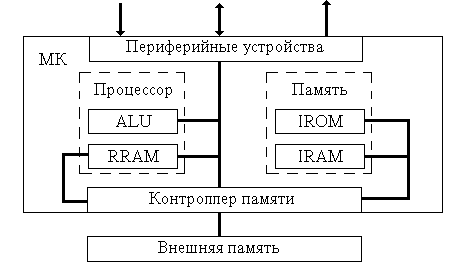

Обобщенная структурная схема микроконтроллера семейства

MCS-x96 изображена на

рис. 16. В его состав входят процессор,

память, набор периферийных устройств и контроллер памяти. К микроконтроллеру

можно подключить внешнюю память.

Процессор содержит арифметико-логическое устройство (ALU) и

регистровое оперативное запоминающее устройство (RRAM). Отличительная

особенность ALU - отсутствие регистра-аккумулятора. При выполнении

арифметических и логических операций в качестве источника первого операнда и

приемника результата может использоваться любой регистр в RRAM , при этом

операнд и результат могут иметь разные адреса. ALU обращается к RRAM

непосредственно или через контроллер памяти.

Рис.18. Обобщенная структурная схема микроконтроллера семейства MCS-x96

Внутренняя (Internal) память

микроконтроллера содержит постоянное (IROM) и оперативное (IRAM) запоминающие

устройства. Первое из них используется для хранения команд программы, констант

и специальных данных. Выпускаются микроконтроллеры, в которых IROM отсутствует

(в этом случае его функции возлагают на запоминающее устройство, входящее в

состав внешней памяти).

IRAM используется

для хранения данных и команд программы. При этом открывается возможность

модифицировать команды в процессе выполнения программы. В микроконтроллерах

некоторых типов IRAM отсутствует.

Общее число адресов в адресном пространстве

микроконтроллера равно 64К, а у микроконтрллеров

подсемейства NT может быть увеличено до 1М.

Контроллер памяти управляет процессом обращения к внутренней

и внешней памяти, при этом обеспечивается опережающая выборка кодов команд с

образованием их очереди.

В таблице 3. указана емкость RRAM, IROM и IRAM

микроконтроллеров разных типов, а также указаны интегрированные на кристалле

микроконтроллера периферийные устройства. Буква Х в обозначении типа заменяется

цифрой 0, если микроконтроллер не имеет IROM, цифрой 3, если он имеет IROM

масочного типа, и цифрой 7, если микроконтроллер содержит программируемое

постоянное запоминающее устройство с возможностью стирания записи путем

ультрафиолетового облучения (EPROM). При отсутствии окна в корпусе микросхемы

возможно лишь однократное программирование IROM (OTPROM).

Таблица 3

|

Микроконтроллер |

8XC196KB |

8XL196KD |

8XC196NТ |

8XC196MC |

8XC196MD |

|

RRAM байт |

232 |

1000 |

1000 |

488 |

488 |

|

IROM Кбайт |

8 |

32 |

32 |

16 |

16 |

|

IRAM байт |

- |

- |

512 |

- |

- |

|

P |

5 |

5 |

8 |

7 |

8 |

|

I/O |

40 |

40 |

56 |

53 |

64 |

|

SLP |

- |

- |

+ |

- |

- |

|

SP |

+ |

+ |

+ |

- |

- |

|

SSIO |

- |

- |

+ |

- |

- |

|

HSIO |

+ |

+ |

- |

- |

- |

|

EPA |

- |

- |

+ |

+ |

+ |

|

ADC |

8 |

8 |

4 |

13 |

14 |

|

PWM |

1 |

3 |

- |

2 |

2 |

|

WG |

- |

- |

- |

+ |

+ |

|

FG |

- |

- |

- |

- |

+ |

|

PTS |

- |

+ |

+ |

+ |

+ |

|

OFD |

- |

- |

+ |

- |

- |

Периферийные

устройства микроконтроллеров семейства MCS-x96

Расположенные на кристалле микроконтроллера периферийные

устройства предназначены для приема и выдачи данных, ввода и вывода событий и

аналоговых сигналов, обслуживания запросов прерывания и контроля правильности

работы микроконтроллера. В таблице 3 приведены данные о наличии определенных

периферийных устройств у микроконтроллеров разных типов и даны некоторые

характеристики этих устройств.

Для приема и выдачи данных в параллельном коде используются

параллельные порты. Микроконтроллеры

разных типов имеют разное число таких портов, при этом разные порты могут иметь

разное число разрядов. В графе Р таблицы указано число

параллельных портов у микроконтроллеров разных типов, а в графе I/O - суммарное

число их разрядов.

Для обмена данными между микроконтроллером и центральным

процессором в иерархической микропроцессорной системе предназначен процессорный

порт (SLP - Slave Port),

который подключают непосредственно к системной магистрали центрального

процессора. В качестве SLP используется один из параллельных портов, который

переводится в соответствующий режим путем программирования.

Для приема и выдачи данных в последовательном коде

используется последовательный порт (SP). Он позволяет увеличивать число

параллельных портов микроконтроллера путем подключения внешних сдвигающих

регистров, обмениваться данными с другими устройствами по последовательному

каналу связи (например, по интерфейсу RS

- 232) и создавать простейшие локальные сети микроконтроллеров.

Для обмена данными в последовательном коде между двумя

микроконтроллерами предназначен синхронный последовательный

порт (SSIO). При этом могут использоваться две, три или четыре соединительные

линии.

Все микроконтроллеры семейства MCS-x96 оснащены специальным

периферийным устройством, предназначенным для приема и регистрации

входных событий и формирования и выдачи выходных. Событием является изменение

значения сигнала. Различают единичные события (замена нулевого значения единичным) и нулевые (замена единичного значения нулевым).

Прием и регистрация входного события заключается в запоминании времени

появления события определенного типа на определенном входе микроконтроллера.

Это позволяет определять временные параметры входных импульсных последовательностей

(период следования и длительность импульсов и т.д.).

При формировании и выдаче выходного события в определенное,

заранее заданное время появляется событие определенного типа на определенном

выходе микроконтроллера (внешнее выходное событие) или в определенной точке

внутри микроконтроллера (внутреннее выходное событие). Это позволяет

формировать импульсные последовательности заданной формы (например,

широтно-модулированный сигнал) и реализовывать временные задержки.

Для работы с событиями в микроконтроллерах подсемейств КВ и КС используется блок быстрого ввода-вывода (HSIO), а в

микроконтроллерах подсемейств KR, NT, MС - блок процессоров событий (EPA). В

HSIO имеется определенное число входных и выходных каналов, в

ЕРА - универсальные модули, каждый из которых может

быть запрограммирован для работы с входными или выходными событиями.

Для ввода аналоговых сигналов используется многоканальный

аналогово-цифровой преобразователь (ADC). Значение аналогового сигнала

представляется восьми- или десятиразрядным двоичным кодом. Число каналов в

преобразователе указано в графе ADC.

Микроконтроллеры подсемейств КВ,

KC, MC имеют широтно-импульсный модулятор (PWM) с программируемым значением

скважности импульсной последовательности. Использование этого модулятора совместно

с внешним интегрирующим устройством позволяет осуществлять цифроаналоговое

преобразование.

Микроконтроллеры подсемейства МС содержат трехфазный

генератор (WG - Waveform Generator),

который может быть использован для управления трехфазными электродвигателями

переменного тока, вентильными электродвигателями постоянного тока, шаговыми

двигателями, а также для преобразования постоянного тока в

переменный.

В микроконтроллерах 8XC196MD имеется генератор меандра (FG-Frequency Generator) с

программируемой длительностью импульсов

и периодом их следования.

Все микроконтроллеры семейства MCS-x96 имеют систему управления

прерываниями. С ее помощью осуществляется переход от выполнения текущей

программы к выполнению прерывающей, составленной программистом и записанной в

память микроконтроллера. Для обслуживания прерываний микроконтроллеры

подсемейств KC, KR, NT, MC имеют, кроме того, периферийный сервер транзакций

(PTS - блок обслуживания групповых операций).

Обслуживание запроса прерывания с использованием PTS заключается в выполнении вместо очередной

команды текущей программы определенной микропрограммы, заложенной в специальную

память микроконтроллера при его изготовлении. Программист выбирает для

обслуживания запроса прерывания подходящую микропрограмму из набора

имеющихся и настраивает ее для

выполнения в каждом конкретном случае

путем записи группы кодов в RRAM.

В число операций, которые могут быть выполнены под

управлением PTS при обслуживании запроса прерывания, входят одиночная и

групповая пересылки и чтение результатов аналого-цифрового преобразования.

Кроме того, микроконтроллеры подсемейства

КС могут выполнять операции, связанные с регистрацией входных и

формированием выходных событий, микроконтроллеры подсемейств KR, NT-операции,

связанные с формированием широтно-модулированных сигналов, а подсемейства МС -

операции, реализующие функции последовательного порта.

Для контроля правильности работы все микроконтроллеры

оснащены сторожевым таймером, сбрасывающим их в исходное состояние при

появлении сбоя в ходе программы. Микроконтроллеры подсемейств KR, NT, кроме

того, содержат детектор падения частоты (OFD), который переводит их в состояние

сброса при катастрофическом снижении тактовой частоты.