Лекция. Питание, система команд и архитектура МК AVR

1.Режимы

пониженного энергопотребления

AVR

микроконтроллеры могут быть переведены программным путем в один из шести

режимов пониженного энергопотребления.

- Режим

холостого хода (IDLE), в котором прекращает работу только процессор и

фиксируется содержимое памяти данных, а внутренний генератор

синхросигналов, таймеры, система прерываний и WATCHDOG-таймер продолжают

функционировать.

- Режим микропотребления (Power Down), в котором сохраняется содержимое регистрового

файла, но останавливается внутренний генератор синхросигналов. Выход из Power Down возможен либо по

общему сбросу микроконтроллера, либо по сигналу (уровень) от внешнего

источника прерывания. При включенном WATCHDOG-таймере ток потребления в

этом режиме составляет около 60...80 мкА, а при выключенном - менее 1 мкА

для всех типов AVR. Вышеприведенные значения справедливы для величины

питающего напряжения 5 В.

- Режим

сохранения энергии (Power Save),

который реализован только у тех AVR, которые имеют в своем составе систему

реального времени. В основном, режим Power Save идентичен Power Down, но здесь допускается независимая работа

дополнительного таймера/счетчика RTC. Выход из режима Power

Save возможен по прерыванию, вызванному или

переполнением таймера/счетчика RTC, или срабатыванием блока сравнения

этого счетчика. Ток потребления в этом режиме составляет 6...10 мкА при

напряжении питания 5 В на частоте 32,768 кГц.

- Режим

подавления шума при работе аналого-цифрового преобразователя (ADC Noise Reduction). Как уже

отмечалось, в этом режиме останавливается процессорное ядро, но разрешена

работа АЦП, двухпроводного интерфейса I2C и сторожевого таймера.

- Основной

режим ожидания (Standby). Идентичен

режиму Power Down, но

здесь работа тактового генератора не прекращается. Это гарантирует быстрый

выход микроконтроллера из режима ожидания всего за 6 тактов генератора.

- Дополнительный

режим ожидания (Extended Standby).

Идентичен режиму Power Save, но здесь работа тактового генератора тоже не

прекращается. Это гарантирует быстрый выход микроконтроллера из режима

ожидания всего за 6 тактов генератора.

Микроконтроллеры AVR mega64, mega103 и mega128 имеют

еще одну примечательную архитектурную особенность, позволяющую значительно

снизить энергопотребление всего кристалла в целом, когда в процессе работы

возникают вынужденные паузы ожидания. В этом случае целесообразно уменьшить ток

потребления центрального процессора и периферийных устройств

как в активном режиме, так и в режиме холостого хода, понизив основную тактовую

частоту микроконтроллера. Для этой цели на кристалле размещен

специальный предделитель, позволяющий делить основную

тактовую частоту на целое число в диапазоне от 2 до 129. Включение/выключение

данной функции осуществляется одной короткой командой в программе. AVR

функционируют в широком диапазоне питающих напряжений от 1,8 до 6,0 Вольт.

Температурные диапазоны работы микроконтроллеров AVR - коммерческий (0С...70С)

и индустриальный (-40С...+85С). К сожалению, корпорация Atmel не выпускает и не

планирует выпускать AVR для работы в автомобильном (-40С...+125С) и военном

(-55С...+125С) температурных диапазонах.

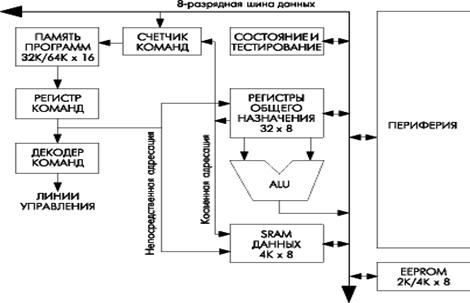

Рис. 2. Структурная схема AVR

С точки

зрения программиста AVR представляет собой 8-разрядный RISC микроконтроллер,

имеющий быстрый Гарвардский процессор, память программ, память данных, порты

ввода/вывода и различные интерфейсные схемы. Структурная схема микроконтроллера

приведена на рис. 2. Гарвардская архитектура AVR реализует полное логическое и

физическое разделение не только адресных пространств, но и информационных шин

для обращения к памяти программ и к памяти данных, причем способы адресации и

доступа к этим массивам памяти также различны. Подобное построение уже ближе к

структуре цифровых сигнальных процессоров и обеспечивает существенное повышение

производительности. Центральный процессор работает одновременно как с памятью

программ, так и с памятью данных; разрядность шины памяти программ расширена до

16 бит. Следующим шагом на пути

увеличения быстродействия AVR является использование технологии конвейеризации,

вследствие чего цикл "выборка - исполнение" команды заметно сокращен.

Например, у микроконтроллеров семейства MCS51 короткая команда выполняется за

12 тактов генератора (1 машинный цикл), в течение которого процессор последовательно

считывает код операции и исполняет ее. В PIC-контроллерах фирмы Microchip, где

уже реализован конвейер, короткая команда выполняется в течение 8 периодов

тактовой частоты (2 машинных цикла). За это время последовательно дешифрируется

и считывается код операции, исполняется команда, фиксируется результат и

одновременно считывается код следующей операции (одноуровневый конвейер).

Поэтому в общем потоке команд одна короткая команда

реализуется за 4 периода тактовой частоты или за один машинный цикл. В

микроконтроллерах AVR тоже используется одноуровневый конвейер при обращении к

памяти программ и короткая команда в общем потоке

выполняется, как и в PIC-контроллерах, за один машинный цикл. Главное же

отличие состоит в том, что этот цикл у AVR составляет всего один период

тактовой частоты. Для сравнения, на рис. 3 приведены временные диаграммы при

выполнении типовой команды для различных микроконтроллерных платформ.

2. Система команд AVR

Система команд AVR весьма развита и насчитывает до 133

различных инструкций. Почти все команды имеют фиксированную длину в одно слово

(16 бит), что позволяет в большинстве случаев объединять в одной команде и код

операции, и операнд(ы). Лишь

немногие команды имеют размер в 2 слова (32 бит) и относятся к группе команд

вызова процедуры CALL, длинных переходов в пределах всего адресного

пространства JMP, возврата из подпрограмм RET и команд работы с памятью

программ LPM. Различают пять групп команд AVR:

условного ветвления, безусловного ветвления, арифметические и логические

операции, команды пересылки данных, команды работы с битами. В последних

версиях кристаллов AVR семейства "mega"

реализована функция аппаратного умножения, что придает новым микроконтроллерам

еще больше привлекательности с точки зрения разработчика.

3. Архитектура микроконтроллеров AVR

Файл регистров быстрого доступа, содержит 32

8-разрядных рабочих регистра общего назначения связанных непосредственно с ALU.

За один тактовый цикл из файла регистров выбираются два операнда, выполняется операция и результат вновь возвращается в файл регистров. Шесть из 32 регистров

могут быть использованы как три 16-разрядных регистра указателя косвенной

адресации адресного пространства данных, обеспечивающие эффективное вычисление

адресов. Один из этих указателей адреса используется, также,

как указатель адреса для функции непрерывного просмотра таблиц. Эти

16-разрядные дополнительные регистры обозначаются X-регистр, Y-регистр и

Z-регистр.

ALU поддерживает арифметические и логические операции

между регистрами или между константой и регистром. Выполняются в ALU и операции

с отдельными регистрами.

На Рис. 5 показана AVR расширенная RISC архитектура

микроконтроллеров ATmega603/103.

Рис. 5. Расширенная RISC

архитектура микроконтроллеров ATmega603/103

В дополнение к операциям с регистрами, регистровый файл

может использоваться и для обычной адресации памяти. Это объясняется тем, что

файл регистров располагается по 32 самыми младшими адресами пространства

данных, и к ним можно обращаться как к обычным ячейкам памяти. Пространство памяти I/O содержит 64

адреса периферийных функций CPU таких как: регистры управления,

таймеры/счетчики, аналого-цифровые преобразователи и другие I/O функции. К

памяти I/O можно обращаться непосредственно или как к ячейкам пространства

памяти соответствующим адресам регистра файлов $20 - $5F. В

микроконтроллерах AVR использованы принципы Гарвардской архитектуры - отдельные

память и шины для программ и данных. При работе с памятью программ используется

одноуровневый конвейер - в то время, как одна команда

выполняется, следующая команда выбирается из памяти программ, Такой прием

позволяет выполнять команду в каждом тактовом цикле. Памятью программ является внутрисистемно программируемая Flash память. За малым

исключением AVR команды имеют формат одного 16-разрядного слова, в связи с чем каждый адрес памяти программ содержит одну

16-разрядную команду. В

процессе обработки прерываний и вызовов подпрограмм адрес возврата счетчика

команд (PC) сохраняется в стеке. Стек размещается в SRAM данных и, следовательно размер стека ограничен только общим размером

SRAM и уровнем ее использования. Все пользовательские программы в подпрограммах

возврата (прежде, чем подпрограммы или прерывания будут выполняться) должны

инициализировать указатель стека (SP). 16-разрядный указатель стека, с

возможностью чтения/записи располагается в пространстве I/O. AVR

архитектура поддерживает пять различных режимов адресации 4000 байт SRAM

данных. Гибкий модуль обработки прерываний имеет в пространстве I/O свой

управляющий регистр с дополнительным битом разрешения глобального прерывания в

регистре статуса. Все прерывания имеют свои векторы прерывания в таблице

векторов прерывания, располагаемой в начале памяти программ. Приоритеты

прерываний соответствуют положению векторов прерываний - прерывание с

наименьшим адресом вектора имеет наивысший приоритет. По

разнообразию и количеству реализованных инструкций AVR больше похожи на CISC,

чем на RISC процессоры. Например, у PIC-контроллеров система команд насчитывает

до 75 различных инструкций, а у MCS51 она составляет 111. В целом,

прогрессивная RISC архитектура AVR в сочетании с наличием регистрового файла и

расширенной системы команд позволяет в короткие сроки создавать работоспособные

программы с эффективным кодом как по компактности реализации,

так и по скорости выполнения.

3.1.Регистровый файл быстрого доступа

Следующая отличительная черта архитектуры

микроконтроллеров AVR - регистровый файл быстрого доступа, структурная схема

которого показана на рис. 4. Каждый из 32-х регистров общего назначения длиной

1 байт непосредственно связан с арифметико-логическим устройством (ALU)

процессора. Другими словами, в AVR существует 32 регистра - аккумулятора

(сравните, например, с MCS51). Это обстоятельство позволяет в сочетании с

конвейерной обработкой выполнять одну операцию в ALU за один машинный цикл.

Так, два операнда извлекаются из регистрового файла, выполняется команда и

результат записывается обратно в регистровый файл в течение только одного

машинного цикла.

Рис. 3. Сравнительная характеристика некоторых

микропроцессорных платформ

Шесть из 32-х регистров файла могут использоваться как

три 16-разрядных указателя адреса при косвенной адресации данных. Один из этих

указателей (Z Pointer) применяется также для доступа

к данным, записанным в памяти программ микроконтроллера. Использование трех

16-битных указателей (X, Y и Z Pointers) существенно

повышает скорость пересылки данных при работе прикладной программы.

Рис. 4. Регистровый файл

Регистровый файл занимает младшие 32 байта в общем адресном пространстве SRAM AVR. Такое архитектурное решение позволяет получать доступ к быстрой

"регистровой" оперативной памяти микроконтроллера двумя путями -

непосредственной адресацией в коде команды к любой ячейке и другими способами

адресации ячеек SRAM. В

технической документации фирмы Atmel это полезное свойство носит название

"быстрое контекстное переключение" и является еще одной отличительной

особенностью архитектуры AVR, повышающей эффективность работы микроконтроллера

и его производительность. Особенно заметно данное преимущество при реализации

процедур целочисленной 16-битной арифметики, когда исключаются многократные

пересылки между различными ячейками памяти данных при обработке арифметических

операндов в ALU.