Особенности архитектуры

однокристальных МП (Лекция)

ПЛАН ЛЕКЦИИ

1. Основные характеристики

однокристальных микропроцессоров

2.

Эволюция архитектуры однокристальных микропроцессоров Intel x86

3. Семейства однокристальных

микроконтроллеров. Базовая организация

4. Набор регистров МК - 51

5. Организация памяти МК-51

6. Периферийные средства МК – 51

1. Основные

характеристики однокристальных микропроцессоров

Основной областью использования микропроцессоров общего назначения являются персональные компьютеры, рабочие станции, серверы и

другие цифровые системы массового применения.

Повышение производительности является

магистральным направлением развития этого класса микропроцессоров. Обычно это

32-разрядные микропроцессоры (некоторые микропроцессоры этого класса имеют

64-разрядную или 128-разрядную структуру), которые следует отнести к CISC-процессорам, так как они выполняют большой набор

разноформатных команд с использованием многочисленных способов адресации.

Однако в их внутренней структуре содержится RISC-процессор, который выполняет

поступившие команды после их преобразования в последовательность простых RISC-операций.

RISC-архитектура характерна для большинства этих

микропроцессоров, также успешно применяются принципы VLIW-apхитектуры, которые может составить конкуренцию RISC-архитектуре в соревновании за достижение наивысшей

производительности.

Практически все современные микропроцессоры

этого класса используют Гарвардскую внутреннюю архитектуру, где разделение

потоков команд и данных реализуется с помощью отдельных блоков кэш-памяти. В

большинстве случаев они имеют суперскалярную структуру с несколькими

исполнительными конвейерами (до 10 в современных моделях), которые содержат до

20 ступеней.

Промышленные

компьютеры размещаются в

корпусах специальной конструкции, обеспечивающих их надежную работу в жестких

производственных условиях. Обычно они работают без стандартных периферийных

устройств (монитор, клавиатура, «мышь») или используют специальные варианты

этих устройств, модифицированные с учетом специфических условий применения.

Микроконтроллеры являются специализированными микропроцессорами, которые

ориентированы на реализацию устройств управления, встраиваемых в разнообразную

аппаратуру. Ввиду огромного количества объектов, управление которыми обеспечивается

с помощью микроконтроллеров, номенклатура выпускаемых микроконтроллеров

содержит несколько тысяч типов.

Характерной особенностью структуры

микроконтроллеров является размещение на одном кристалле с центральным

процессором внутренней памяти и большого набора периферийных устройств. Для

удовлетворения запросов потребителей выпускается большая номенклатура

микроконтроллеров, которые принято подразделять на 8-, 16- и 32-разрядные:

1) 8-разрядные микроконтроллеры имеют

относительно низкую производительность, достаточной для решения широкого круга

задач управления различными объектами. Основными областями их применения

являются бытовая и измерительная техника, промышленная автоматика,

автомобильная электроника, теле-, видео- и аудиоаппаратура, средства связи.

Для этих микроконтроллеров характерна

реализация Гарвардской архитектуры, где используется отдельная память для

хранения программ и данных. Внутренняя память программ обычно имеет объем от

нескольких единиц до десятков Кбайт. Для хранения данных используется

регистровый блок, организованный в виде нескольких регистровых банков, или

внутреннее ОЗУ. Объем внутренней памяти данных составляет от нескольких

десятков байт до нескольких Кбайт. Относительно небольшой набор команд

(50-100), использующих наиболее простые способы адресации. В ряде последних

моделей этих микроконтроллеров реализованы принципы RISC-архитектуры,

что позволяет существенно повысить их производительность. В результате такие

микроконтроллеры обеспечивают выполнение большинства команд за один такт

машинного времени.

2) 16-разрядные

микроконтроллеры характеризуются не только увеличенной разрядностью

обрабатываемых данных, но и расширенной системой команд и способов адресации,

увеличенным набором регистров и объемом адресуемой памяти, а также рядом других

дополнительных возможностей, использование которых позволяет повысить

производительность и обеспечить новые области применения. Основная сфера

применения таких микроконтроллеров - сложная промышленная автоматика,

телекоммуникационная аппаратура, медицинская и измерительная техника.

3) 32-разрядные

микроконтроллеры содержат высокопроизводительный процессор, соответствующий по

своим возможностям младшим моделям микропроцессоров общего назначения. На

кристалле микроконтроллера размещается внутренняя память команд емкостью до

десятков Кбайт, память данных емкостью до нескольких Кбайт, а также

сложно-функциональные периферийные устройства - таймерный процессор,

коммуникационный процессор, модуль последовательного обмена и ряд других.

Микроконтроллеры работают с внешней памятью объемом до 16 Мбайт и выше. Во

внутренней структуре этих микроконтроллеров реализуется Принстонская или

Гарвардская архитектура. Входящие в их состав процессоры могут иметь CISC - или RISC - архитектуру, а

некоторые из них содержат несколько исполнительных конвейеров, образующих

суперскалярную структуру.

Они находят широкое

применение в системах управления сложными объектами промышленной автоматики

(двигатели, робототехнические устройства, средства комплексной автоматизации

производства), в контрольно-измерительной аппаратуре и телекоммуникационном

оборудовании.

Цифровые

процессоры сигналов (ЦПС) представляют

класс специализированных микропроцессоров, ориентированных на цифровую

обработку поступающих аналоговых сигналов. Специфической особенностью

алгоритмов обработки аналоговых сигналов является необходимость

последовательного выполнения ряда команд умножения-сложения с накоплением

промежуточного результата в регистре-аккумуляторе. Поэтому архитектура ЦПС

ориентирована на реализацию быстрого выполнения операций такого рода. Набор

команд этих процессоров содержит специальные команды MAC

(Multiplication with Accumlation), реализующие эти операции. Для повышения

производительности при выполнении специфических операций обработки сигналов в

большинстве ЦПС реализуется Гарвардская архитектура с использованием нескольких

шин для передачи адресов, команд и данных. В ряде ЦПС нашли применение также

некоторые черты VLIW-архитектуры: совмещение в одной

команде нескольких операций, обеспечивающих обработку имеющихся данных и

одновременную загрузку в исполнительный конвейер новых данных для последующей

обработки.

2. Эволюция

архитектуры однокристальных микропроцессоров Intel x86

1) Особенности процессоров 8086/8088.

Процессор i8086 имеет совмещенную (мультиплексированную) 20-разрядную

внешнюю шину адреса/данных. Данные передаются по 16 разрядам, адрес - по 20

разрядам. Шина управления имеет 16 разрядов (в частности, в нее входят строб

адреса и стробы обмена с памятью и устройствами ввода/вывода). Среднее время

выполнения команды занимает 12 тактов синхронизации, один цикл обмена по

внешней шине требует 4 тактов (без учета тактов ожидания, вводимых при

асинхронном обмене). У процессора i8088 внешняя шина

данных 8-разрядная.

Процессоры i8086/8088

– имеют сегментированную память. То есть вся память представляется не в виде

непрерывного пространства, а в виде нескольких кусков - сегментов заданного

размера (по 64 Кбайта), положение которых в пространстве памяти можно

программно изменять. Процессор 8086/8088 имеет 14 регистров разрядностью по 16

бит. Для ускорения выборки команд из памяти в процессоре 8086 предусмотрен

внутренний 6-байтный конвейер (в процессоре 8088 - 4-байтный). Система команд

процессора включает в себя 133 команды, поддерживающие 24 метода адресации

операндов. Такое большое число команд может рассматриваться как достоинство

(можно гибко выбирать команду, оптимально подходящую для каждого конкретного

случая), но оно же заметно усложняет структуру процессора. Каждая команда

содержит 1, 2 или 4 байта кода команды, за которыми могут следовать 1, 2 или 4

байта операнда.

Процессор может обрабатывать 256 типов

прерываний: внешних (аппаратных), программных и внутренних. Векторы прерываний

представляют собой двойное слово (два слова по 16 разрядов), определяющее

сегмент и смещение начального адреса программы обработки прерываний. Внутренние

прерывания вырабатываются при особых ситуациях.

Важная отличительная особенность процессора -

разделение операций обмена с устройствами ввода/вывода и с памятью. Процессор

работает от одного источника питания напряжением +5В и требует внешнего

тактирующего сигнала с частотой, определяемой номером модели (от 4,77 МГц до 10

МГц). Специальный управляющий сигнал MN/MX определяет минимальный или максимальный режим работы

процессора.

2) Особенности процессора 80286. Отличие от

процессора 8086/8088 - в механизме управления адресацией памяти, который

обеспечивает четырехуровневую систему защиты и поддержку виртуальной памяти.

(Виртуальная память - это внешняя память большого объема, с которой процессор

может взаимодействовать как со своей системной памятью, но с некоторыми

ограничениями). Специальные средства предусмотрены также для поддержки

механизма переключения задач (Task switching). В процессоре 80286 также расширена система команд за

счет добавления команд управления защитой и нескольких новых команд общего

назначения.

Процессор 80286 может работать в двух режимах:

- реальный режим (8086 Real Address Mode - режим реальной адресации), полностью совместимый с процессором

8086/8088. В этом режиме возможна адресация только в пределах 1 Мбайта

физической памяти. Он используется для обеспечения программной преемственности

с процессором 8086/8088;

- защищенный режим (Protected Virtual Address Mode - защищенный

режим виртуальной адресации). В этом режиме возможна адресация в пределах 16

Мбайт физической памяти.

Процессор 80286 имеет 16-разрядную внешнюю

шину данных и 6-байтный конвейер команд. Для ускорения выполнения

математических операций предусмотрено подключение к процессору 80286 микросхемы

математического сопроцессора 80287.

Так же, как и в 8086,

применяется сегментация памяти, но управление сегментацией в реальном и

защищенном режимах различно. Процессор 80286 может обрабатывать до 256 типов

прерываний. Прерывания подразделяются на аппаратные (маскируемые или

немаскируемые), вызываемые сигналами на входах процессора, программные,

вызываемые командой INT, и исключения инструкций.

Система команд процессора 80286 включает,

помимо полного набора 8086, ряд дополнительных команд, например: сохранение

константы в стеке, сохранение в стеке и восстановление из стека всех регистров

одной командой; целочисленное умножение на константу; сдвиги (включая

циклические) на заданное в константе количество шагов; вход и выход из процедур;

команды управления защитой.

3) Особенности процессора 80386. В 32-разрядном процессоре i80386 нет

ограничения на длину непрерывного сегмента памяти в 64 Кбайт. В защищенном

режиме 80386 длина сегмента может достигать 4 Гбайт, то есть всего объема физически

адресуемой памяти. Таким образом, память фактически стала непрерывной. Кроме

того, 80386 обеспечивает поддержку виртуальной памяти объемом до 64 Тбайт (1

Тбайт = 1024 Гбайт). Встроенный блок управления памятью поддерживает механизмы

сегментации и страничной трансляции адресов (Paging). Обеспечивается четырехуровневая система защиты памяти и

ввода/вывода, а также переключение задач.

Процессор 80386, как и 80286, может работать в

двух режимах: реальный режим, который полностью совместим с 8086, защищенный

режим. В этом режиме возможна адресация до 4 Гбайт физической памяти (32

разряда), через которые при использовании механизма страничной адресации может

отображаться до 16 Тбайт виртуальной памяти каждой задачи. Процессор может

оперировать с 8, 16, 32-битными операндами, строками байт, слов и двойных слов,

а также с битами, битовыми полями и строками бит.

В архитектуру процессора введены средства

отладки и тестирования.

Разрядность регистров данных (АХ, ВХ, СХ, DX) и адресов (SI, D1, ВР, SP) увеличена до 32.

При этом в их обозначении появилась приставка Е (Extended - расширенный), например, ЕАХ, ESI.

Расширен до 32 разрядов регистр-указатель (счетчик) команд EIP. 32-разрядным стал регистр флагов EFLAGS. Такой же формат используется и в процессорах 80486 и Pentium. Регистры сегментов процессора содержат 16-битные

указатели (в реальном режиме) или селекторы (в защищенном режиме) шести

сегментов. С каждым из шести сегментных регистров связаны программно

недоступные регистры дескрипторов, как и в случае 80286. В защищенном режиме в

регистры дескрипторов загружается 32-битный базовый адрес сегмента, 32-битный

лимит и атрибуты сегментов.

Процессор позволяет выделять в памяти сегменты

и страницы. Сегменты в реальном режиме имеют фиксированный размер, в защищенном

- переменный. Процессор 80386 обрабатывает все виды прерывания: аппаратные

(маскируемые и немаскируемые) и программные, которые в данном случае

обрабатываются как разновидность исключений, и собственно исключения.

Исключения подразделяются на отказы, ловушки и аварийные завершения.

Каждому номеру прерывания (0...255) или

исключения соответствует элемент в таблице дескрипторов прерываний IDT (Interrupt Descriptor Table). В защищенном

режиме IDT может иметь размер от 32 до 256 дескрипторов, каждый из

которых состоит из 8 байт.

Защищенный режим был предложен для обеспечения

независимости одновременного выполнения нескольких задач (как системных, так и

прикладных). Для этого предусмотрена защита ресурсов каждой задачи от действий

других задач. Под ресурсами здесь понимается память с данными, программами,

системными таблицами, а также используемая задачей аппаратура. Защита

основывается на сегментации памяти, причем, в отличие от реального режима,

задача не может переопределять положения своих сегментов в памяти и использует

только сегменты, определенные для нее операционной системой.

Сегмент определяется дескриптором сегмента,

который задает положение сегмента в памяти, его размер (или лимит), назначение

и характеристики защиты.

В защищенном режиме предусматривается

иерархическая четырехуровневая (уровни 0, 1,2, 3) система привилегий,

предназначенная для управления выполнением привилегированных команд и доступом

к дескрипторам. Механизм виртуальной памяти, используемый в защищенном режиме,

позволяет любой задаче использовать логическое пространство размером до 64

Тбайт (16К сегментов по 4 Гбайта).

Начиная с процессора 80386,

появляются средства обслуживания многозадачного режима. Естественно, процессор

не может обрабатывать несколько задач одновременно, выполняя по несколько

команд сразу. Он только периодически переключается между задачами. Но с точки

зрения пользователя получается, что компьютер параллельно работает с

несколькими задачами.

4) Особенности процессора 486. Процессор 486 является представителем

второго поколения 32-разрядных процессоров. Он сохраняет основные принципы

архитектуры процессора 80386, а также обеспечивает полную совместимость со

своими предшественниками. Ряд преимуществ: в процессор введена внутренняя

кэш-память 1-го уровня (Internal cache Level 1) размером 8

Кбайт и предусмотрены средства для двухуровневого кэширования; введен

математический сопроцессор (в модели процессора 486SX сопроцессор отсутствует);

повышена производительность обмена по внешней шине - введены так называемые

пакетные циклы, передающие одно слово за один такт шины; в архитектуре

процессора применено скоростное RISC-ядро, которое

позволяет наиболее часто встречающиеся команды выполнять за один такт; в

структуру введены буферы отложенной записи.

Кэш-память (или просто кэш, от англ. Cache - склад, тайник) предназначена для промежуточного хранения

информации из системной памяти с целью ускорения доступа к ней. Ускорение

достигается за счет использования более быстрой памяти и более быстрого доступа

к ней. При этом в кэш-памяти хранится постоянно обновляемая копия некоторой

области основной памяти.

Необходимость введения кэша связана с тем, что

системная память персонального компьютера выполняется на микросхемах

динамической памяти, которая характеризуется меньшей стоимостью, но и более

низким быстродействием, по сравнению со статической памятью. В принципе

кэш-память может быть как внутренней (входить в состав процессора), типовой

размер 32 Кбайт так и внешней – до нескольких мегабайт. Внутренний кэш

называется кэшем первого уровня, внешний - кэшем второго уровня.

Режим пакетной передачи (Burst Mode), впервые появившийся в процессоре 486, предназначен для

быстрых операций со строками кэша. Пакетный цикл обмена (Burst Cycle) отличается

тем, что для пересылки всего пакета адрес по внешней шине адреса передается

только один раз - в начале пакета, а затем в каждом следующем такте передаются

только данные. Режим внутреннего умножения тактовой частоты процессора повышает

быстродействие процессора.

5) Особенности процессоров Pentium. Процессоры Pentium относятся к пятому поколению процессоров или к третьему

поколению 32-разрядных процессоров нового поколения с существенными отличиями:

суперскалярная

архитектура процессора, то есть процессор имеет два пятиступенчатых параллельно

работающих конвейера обработки информации, благодаря чему он способен

одновременно выполнять две команды за один такт;

внешняя 64-разрядная

шина данных для повышения производительности. Это требует соответствующей

организации памяти. Из-за такой особенности процессор иногда неправильно

называют 64-разрядным (хотя внутри он все-таки остался 32-разрядным). Внешняя

шина адреса процессора - 32-разрядная;

применение технологии

динамического предсказания ветвлений (переходов);

раздельный кэш для

команд и данных объемом 8 Кбайт каждый. Длина строки кэша - 32 байта. Оба кэша

работают в режиме обратной записи;

повышенная в 2-10 раз

по сравнению с процессором 486 производительность встроенного математического

сопроцессора. В нем применена восьмиступенчатая конвейеризация и специальные

блоки сложения, умножения и деления, что позволяет выполнять операции с

плавающей точкой за один такт процессора;

сокращено время (число

тактов) выполнения команд;

предусмотрена

возможность построения двухпроцессорных систем;

введены средства управления

энергопотреблением и тестирования.

Средства для слежения за

производительностью (мониторинга производительности) включают в себя таймер

реального времени и счетчики событий. Таймер представляет собой 64-разрядный

счетчик, инкрементируемый с каждым тактом процессора. Два счетчика событий

имеют разрядность по 40 бит и программируются на подсчет событий различных

классов, связанных с шинными операциями, исполнением команд, связанных с

работой кэша, контролем точек останова и т.д. Сравнивая состояния таймера и

счетчиков событий, можно сделать вывод о производительности процессора.

Средства для построения двухпроцессорных

систем позволяют на одной локальной шине устанавливать два процессора с

объединением почти всех одноименных выводов. Это дает возможность использовать

симметричную мультипроцессорную обработку (SMP

- Symmetric Multi-Processing) или строить функционально избыточные системы (FRC - Functional Redundancy Checking).

В конфигурации FRC

два процессора выступают как один логический процессор. Основной процессор (Master) работает в обычном однопроцессорном режиме. Проверочный

процессор (Checker) выполняет все те же операции внутри себя, не управляя

внешней шиной, и сравнивает сигналы основного процессора с теми, которые

генерирует сам. В случае несовпадения формируется сигнал ошибки, обрабатываемый

как прерывание. То есть в данном случае увеличивается надежность системы в

целом (в идеале - вдвое).

Развитием Pentium стало добавление технологии ММХ, рассчитанной на

мультимедийное, графическое и коммуникационное применение. Основная идея ММХ

заключается в одновременной обработке нескольких элементов данных за одну

команду (SIM D, Single Instruction - Mutiple Data). Команды ММХ

доступны из любого режима процессора. Кроме того, в процессорах Pentium ММХ увеличен объем кэша данных и программ (до 16 Кбайт

каждый), увеличено число ступеней конвейеров и введено еще несколько

усовершенствований, повышающих производительность обычных (не мультимедийных)

операций.

6) Особенности процессора Pentium Pro. Это шестое

поколение процессоров, имеющего следующие усовершенствования:

динамическое

исполнение команд предполагает, что команды, независящие от результатов

предыдущих операций, могут выполняться в измененном порядке (последующие раньше

предыдущих), однако последовательность обмена с внешними устройствами (памятью

и устройствами ввода/вывода) будет соответствовать программе. То есть процессор

сам выбирает удобный ему порядок выполнения команд. Это позволяет повысить

производительность процессора без увеличения тактовой частоты;

архитектура двойной

независимой шины повышает суммарную пропускную способность. Одна шина

(системная) служит для обмена с основной памятью и устройствами ввода/вывода, а

другая (локальная) предназначена только для обмена с вторичным кэшем;

в процессор введен кэш

второго уровня объемом 256-512 Кбайт;

возможно построение

многопроцессорных систем (до четырех микропроцессоров).

7) Особенности процессора Pentium II сочетает в себе

архитектуру Pentium Pro с технологией MMX. Размер первичных кэшей данных и команд составляет 16

Кбайт, вторичного кэша - до 512 Кбайт. Кэш второго уровня несколько медленнее,

чем кэш первого уровня, зато он имеет больший объем. Такая двухуровневая

организация позволяет достигать компромисса между быстродействием кэш-памяти и

ее объемом. Шина адреса имеет 36 разрядов (то есть максимально допустимый объем

памяти - 64 Гбайта).

Процессоры Pentium III и Pentium 4 отличаются значительно возросшей предельной тактовой

частотой (до 3 ГГц у Pentium 4, а в перспективе и до 5 ГГц),

увеличенным объемом кэша (от 512 Кбайт до нескольких мегабайт) и дальнейшим

совершенствованием архитектуры Pentium. Размер

внутреннего конвейера у Pentium 4 доведен до 20 ступеней.

Уже появились и полностью 64-разрядные

процессоры. Правда, полное использование возможностей 64-разрядной архитектуры

потребует существенного изменения программного обеспечения. Надо отметить, что

в составе персональных компьютеров практически никогда не используются все

возможности процессоров семейства Pentium.

Для портативных компьютеров были предложены

упрощенные версии процессоров Pentium III и Pentium 4, продаваемые под маркой Celeron. Они отличаются уменьшенной тактовой частотой и

сокращенным объемом кэша второго уровня. Их тактовая частота сейчас доходит до

2 ГГц. Надо учитывать, что рассеиваемая мощность процессора Celeron остается практически такой же, как у процессоров Pentium III и Pentium 4.

3. Семейства

однокристальных микроконтроллеров. Базовая организация

Семейства однокристальных микроконтроллеров ориентировано

на применение встраиваемых в изделие недорогих управляющих систем реального

времени, рабочая программа которых расположена в ПЗУ системы. Широко

применяются микроконтроллеры семейства iMCS-48,

iMCS-51, iMCS-96, имеющие гарвардскую

архитектуру, содержащие на кристалле все необходимые узлы для работы в

автономном режиме и предназначенные для реализации различных цифровых

алгоритмов управления. Рассмотрим базовый микроконтроллер Intel 8051 (МК-51),

условное обозначение которого приведено на рисунке 52.

Рис. Условное обозначение микроконтроллера МК – 51

В состав микроконтроллера

МК-51 входит 8-разрядный центральный процессор, управляющий работой

исполнительных устройств микроЭВМ и имеющий аппаратную поддержку операций

умножения и деления. Всего процессор выполняет 111 команд разрядностью в 1, 2

или 3 байта.

На рисунке 53 приведена

структурная схема базовой организации микроконтроллера МК-51:

Рис.

Структурная схема микроконтроллера МК-51

Внутренняя (расположенная на

кристалле) память программ объемом 4К байт. Внутренняя память данных объемом

128 байт, используемая для организации регистровых банков, стека и хранения

пользовательских данных. 32 двунаправленные интерфейсные линии, индивидуально

настраиваемые на ввод или вывод информации и организованные в виде четырех

8-разрядных параллельных портов Р0 - Р3. Два 16-разрядных многорежимных

таймера/счетчика T/C0 и T/C1, используемые для подсчета внешних событий,

организации временных задержек и тактирования последовательного порта.

Двунаправленный дуплексный

асинхронный последовательный приемопередатчик - последовательный порт.

Двухуровневая приоритетная система прерываний от четырех внутренних и двух

внешних источников. Встроенный тактовый генератор, частота которого задается с

помощью внешнего кварцевого резонатора, LC-цепочки или внешнего генератора.

В архитектуре ВЕ51 и ее модификациях

использован стандартный для МК принцип независимости сред для хранения программ

и данных. Всего же архитектура ВЕ51 включает пять типов пространств, четыре из

которых являются областями данных:

RSEG Пространство регистров

DSEG Пространство внутренней памяти данных

BSEG Битовое пространство данных

XSEG Пространство внешней памяти

CSEG Пространство программного кода

4. Набор

регистров МК - 51

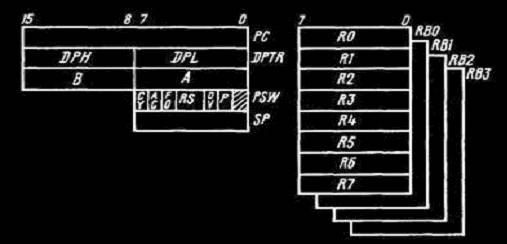

Набор программно-доступных регистров

процессора ВЕ51 приведен на рисунке 54. Он является расширением набора

регистров ВЕ48, что обеспечивает совместимость архитектур ВЕ48 и ВЕ51 снизу

вверх. Центральным регистром набора считается 8-разрядный аккумулятор А,

выполняющий обычные функции основного арифметического регистра.

Регистр В служит расширением аккумулятора А,

необходимым для осуществления операций умножения и деления, причем он является

как источником, так и приемником операндов. Во всех других операциях регистр В выполняет

функции, определяемые пользователем.

Регистр слова состояния программы включает

флажки:

PSW.7 CY Перенос

из старшего разряда АЛУ

PSW.6 АС Дополнительный

перенос из младшей тетрады АЛУ

PSW.5 F0 Флажок

пользователя общего назначения

PSW.2 OV Признак

арифметического переполнения результата

PSW.1 Р Признак

четности

Сюда же входит двухразрядное поле RS (Registers Select) выбора одного из четырех возможных банков рабочих

регистров. Флажки признаков результата CY,

АС и OV, как правило, отражают состояние последней арифметической

операции, флажок Р - четность содержимого А. Флажок переноса CY является аккумулятором булевого процессора. Функциональное

назначение флажка F0 определяется пользователем в

конкретной ситуации.

Рис. Набор регистров МК-51

Шестнадцатиразрядный программный счетчик PC управляет последовательностью выполнения команд,

хранящихся в программной памяти объемом до 64К байт. Указатель данных DPTR также имеет длину 16 разрядов, каждая его половина может

быть адресована независимо от другой. Этот регистр используется в качестве

адресного при пересылке констант из памяти программ и доступе к переменным из

внешней памяти данных, а также для организации передачи управления.

Указатель стека образует системный стек

глубиной до 256 байт. Он всегда содержит адрес последнего байта, занесенного в

стек. Стек растет в сторону увеличения содержимого SP.

В МК - 51 предусмотрено четыре банка по восемь

рабочих регистров R0-R7

в каждом, переключаемых полем RS слова состояния

программы. Регистры выполняют общецелевые функции промежуточного хранения

данных. Два регистра R0 и R1

каждого банка реализуют также функции 8-разрядных указателей данных.

5.

Организация памяти МК-51

Пространство внутренней памяти DSEG имеет общий объем 256 байт. Однако организация ВЕ51

предусматривает реализацию только первой его половины (128 байт). В МК 8052 DSEG используется в полном объеме.

Подобно архитектуре ВЕ48 все банки рабочих

регистров, а также системный стек в МК ВЕ51 располагаются во внутренней памяти

данных и могут рассматриваться как обычные ячейки памяти. Существуют два

способа адресации памяти данных МК: прямой (direct) и косвенный (@Ri, i = 0- 1) через регистры R0,

R1 выбранного в данный момент одного из банков RB0-RB3. При прямой адресации доступна

только младшая половина адресного пространства внутренней памяти данных (128

байт), при косвенной обеспечивается доступ к любой ее ячейке (256 байт).

Введение отсутствующей в ВЕ48 прямой адресации значительно расширило

возможности обработки данных МК, в частности появились средства прямого доступа

в соседние регистровые банки и стек системы, интерпретируемые как обычные

ячейки памяти.

Микроконтроллер ВЕ51 имеет мощную и развитую

подсистему ВВ и средства поддержки режима реального времени. Для их управления

в МК предусмотрен ряд регистров, которые размещаются во второй половине прямо

адресуемого пространства (Рисунок 55), образующей пространство специальных

регистров (128 байт). Сюда же включены порты и основные регистры ЦП.

Центральный процессор МК - 51 содержит специальную логику, предназначенную для

выполнения нескольких однобитовых операций, булев или одноразрядный процессор

для вычисления булевых выражений. В основу булева процессора положен

стандартный аккумуляторный принцип организации. В данном случае роль аккумулятора

выполняет флажок переноса CY.

Для хранения булевых данных в архитектуре ВЕ51

предусмотрено специальное одноразрядное линейно упорядоченное пространство BSEG объемом 256 байт, которое физически совмещено с байтовым

пространством данных DSEG. При этом одна часть пространства BSEG попадает на обычные ячейки памяти DSEG

и может рассматриваться как область общего назначения. Обычно она используется

для хранения булевых переменных. Другая часть пространства BSEG попадает на ячейки памяти, совмещенные с регистрами МК,

что обеспечивает независимый доступ к их отдельным разрядам. В булевом

пространстве определена только прямая адресация bit.

На рисунке 53 показано в байтах пространство с

прямой адресацией, которое размещено в булевом пространстве, указаны диапазоны

адресов BSEG, относящихся к их разрядам.

Рис. Прямо

адресуемая часть внутренней

памяти данных (а) и память специальных регистров (б)

Например, старший разряд аккумулятора А,

отождествленного с ячейкой пространства памяти с прямой адресацией под адресом

0E0H, имеет адрес пространства BSEG, равный 0Е7Н.

6. Периферийные

средства МК – 51

Параллельные

каналы связи. Подсистема ВВ

микроконтроллера МК - 51 размещается непосредственно на кристалле. Для ВВ

данных и управления процессом их передачи в состав МК введен ряд портов данных

и регистров управления/состояния, совокупность которых образует набор

специальных регистров.

Физическая

система ВВ микроконтроллера МК - 51 состоит из четырех двунаправленных

8-разрядных портов Р0 - РЗ. Все порты ВВ отображены в пространстве внутренней

памяти DSEG по адресам 80Н, 90Н, 0А0Н, 0В0Н и ничем не отличаются от

обычных ячеек памяти. Отказ от изолированного пространства ВВ, используемого в

архитектуре ВЕ48, позволил увеличить вычислительную эффективность МС интенсивного

ВВ, привел к более регулярной структуре набора команд ВЕ51. Любая команда с

операндом из внутренней памяти может быть применена к содержимому портов Р0 -

РЗ.

Кроме того, порты Р0 - РЗ совмещены с битовым

пространством BSEG, что обеспечивает доступ к отдельным

его разрядам независимо от других. Порты Р0 - РЗ занимают адреса BSEG: 80Н - 87Н, 90Н -97Н, 0А0Н -0А7Н и 0В0Н - 0В7Н

соответственно.

Расширение пространства ВВ может быть

выполнено за счет области XSEG или другими

средствами с помощью самих портов Р0 - РЗ и SBUF.

При обращении к внешней памяти программ или

данных порты Р0, Р2 выполняют функции системных шин AD

и АВ соответственно. Младший байт адреса и данные передаются через Р0 в

мультиплексном режиме: сначала выводится адрес, а затем для передачи данных

используется порт. Старший байт адреса формируется на Р2. Линии порта РЗ

реализуют управление циклами обмена и другие специальные функции аппаратного

уровня

Таблица 3. Линии порта РЗ

|

РЗ.0 |

RxD |

Вход

приемника последовательного канала |

|

Р3.1 |

TxD |

Выход

передатчика последовательного канала |

|

Р3.2 |

INT0 |

Вход

запроса на прерывание 0 |

|

РЗ.З |

INT1 |

Вход

запроса на прерывание 1 |

|

Р3.4 |

T0

|

Внешний

вход таймера/счетчика 0 |

|

Р3.5 |

Tl |

Внешний

вход таймера/счетчика 1 |

|

Р3.6 |

WR |

Строб

записи в XSEG |

|

Р3.7 |

RD |

Строб

чтения XSEG |

Последовательный

канал связи. В состав МК-51 входит

дуплексный канал последовательной связи с буферизацией, который может быть

запрограммирован для работы в одном из четырех режимов:

режим 0-синхронный последовательный ВВ со

скоростью OSC/12;

режим 1-асинхронный с 10-битовым кадром и

переменной скоростью передачи;

режим 2 - асинхронный с 11-битовым кадром и

фиксированной скоростью передачи OSC/32 или OSC/64;

режим 3-асинхронный с 11-битовым кадром и

переменной скоростью передачи.

Входные и выходные данные хранятся в буферном

регистре SBUF с адресом 99Н. Управление работой приемопередатчиков

осуществляется через слово управления и состояния SCON,

расположенное в регистре по адресу 98Н:

SCON.0 RI Флаг прерывания приемника

SCON.l TI Флаг

прерывания передатчика

SCON.2 RB8 Восьмой бит приемника в режимах 2 и 3.

В режиме 1, если SM2

= 0, то отображает стоп-бит. В режиме 0 не используется.

SCON.3 ТВ8 Восьмой

бит передатчика в режимах 2 и 3

SCON 4 REN Разрешение приема

SCON.5 SM2 Запрещение приема кадров с нулевым восьмым

битом данных. В режиме 0 должен быть сброшен

SCON.6 SMI Младший разряд для кодирования номера

режима

SCON.7 SM0 Старший разряд для кодирования номера

режима:

|

SM0 |

SM1 |

Режим |

SM0 |

SM1 |

Режим |

|

0 |

0 |

0 |

1 |

0 |

2 |

|

0 |

1 |

1 |

1 |

1 |

3 |

Таймеры/счетчики. К стандартным средствам поддержки режима реального времени

относятся таймеры/счетчики и подсистема прерываний. Если таймеры необходимы для

организации системных меток реального времени и отработки временных интервалов,

то подсистема прерываний обеспечивает своевременную реакцию МК на асинхронные

события, происходящие как внутри МС, так и вне ее.

В состав МК - 51 входят два 16-разрядных

таймера/счетчика СТ0, СТ1. Еще один (СТ2) добавлен в архитектуре 8052.

Состояние таймеров/счетчиков отражается программно-доступными регистровыми

парами (TH0, TL0), (TH1,

ТЫ) и (ТН2, TL2) соответственно, размещенными в пространстве DSEG по адресам (8СН, 8АН), (8DH,

8ВН) и (0CDH, 0ССН).

Таймеры/счетчики СТ0 - СТ2 могут быть

запрограммированы для работы либо в качестве таймера, либо в качестве счетчика.

Функция таймера состоит в счете числа машинных циклов, следующих с частотой OSC/12. Функция счетчика заключается в отслеживании числа

переходов из 1 в 0 на соответствующих входах Т0, Tl,

T2.

Управление режимом работы СТ0, СТ1

осуществляет регистр TMOD (Timer/Counter Mode), который

расположен по адресу 89Н. Регистр разбит на два 4-разрядных подрегистра T0MOD и T1MOD, которые ответственны за управление СТО и СТ1

соответственно:

Таблица 4

|

TMOD.0 |

M0 |

Младший бит поля управления режимом СТ0 |

|||||

|

TMOD.l |

Ml |

Старший бит поля управления режимом СТ0: |

|||||

|

|

|

М0 |

Ml |

Режим |

М0 |

Ml |

Режим |

|

|

|

0 |

0 |

0 |

1 |

0 |

2 |

|

|

|

0 |

1 |

1 |

1 |

1 |

3 |

|

TMOD.2 |

C/TN |

Выбор функции таймера или счетчика СТ0. При |

|||||

|

|

|

С/Т - 0 выбирается функция таймера, в противном случае

счетчика |

|||||

|

TMOD.3 |

GATE |

Флажок

управления работой СТО. При GATE = 1 работа

разрешается, если INTO = 1 и TR0

= 1(см. TCON). При GATE=0 работа счетчика зависит только от состояния TR0 |

|||||

|

TMOD.4 |

М0 |

То же, но для СТ1 |

|||||

|

TM0D.5 |

Ml |

То же, но для СТ1 |

|||||

|

TMOD.6 |

С/Т |

То же, но для СТ1 |

|||||

|

TMOD.7 |

GATE |

То же, но для СТ1 |

|||||

Система

прерываний. Архитектура МК- 51

поддерживает двухуровневую приоритетную систему прерываний с пятью (или шестью

в случае 8052) источниками запросов на обслуживание, имеющими фиксированные

векторы прерываний. Программное управление системой осуществляется через два

8-разрядных регистра: IP (Interrupt Priopity) - регистр приоритета прерываний и IE (Interrupt Enable) - регистр разрешения прерываний.

Для приема внешних запросов на прерывание

служат линии INT0 и INT1, которые могут быть запрограммированы

на срабатывание как по переходу из одного состояния в другое, так и по уровню

входного сигнала независимо друг от друга. Управление типом входа

осуществляется флажками IT0/TCON.0

(Interrupt Туре 0) и IT1/TCON.2. При ITi = l устанавливается режим срабатывания по переходу из 1 в 0, в

противном случае - по напряжению низкого уровня на входе INTi, i = 0-1. Запросы на прерывание от

внешних источников INT0 или INT1

устанавливают флажки IE0/TCON.1

(Interrupt Edge 0) и IE1/TCON.3. В случае работы по переходу эти

флажки сбрасываются автоматически при входе в соответствующую процедуру

обслуживания прерывания. В случае режима работы по уровню флажки отслеживают

состояние сигналов на входных линиях INT0 и INT1, повторяя все их изменения.

Источниками внутренних запросов могут быть:

флажок TF0/TCON.5 (Timer Flag 0) - признак переполнения СТ0, с

флажок TF1/TCON.7 - признак переполнения СП, а

также флажок TI/SCON.1 (Transmit Interrupt) или флажок RI/SCON.O

(Recive Interrupt).

Выводы

Рассмотрены основные

технические характеристики, структура микроконтроллера МК – 51, входящего в

семейство iMCS51. Приводится материал по организации памяти, адресации и

встроенных интерфейсных системах.